Intelの前CEO Pat Gelsinger氏が、同社の最先端18Aプロセスノードの歩留まりを巡る否定的な報道に対して反論を展開した。業界アナリストPatrick Moorhead氏のSNS投稿に応答する形で、Gelsinger氏は18Aチームの進捗を強く擁護し、報道内容を「フェイクニュース」と一蹴した。

18Aプロセスの実態と歩留まりの技術的解説

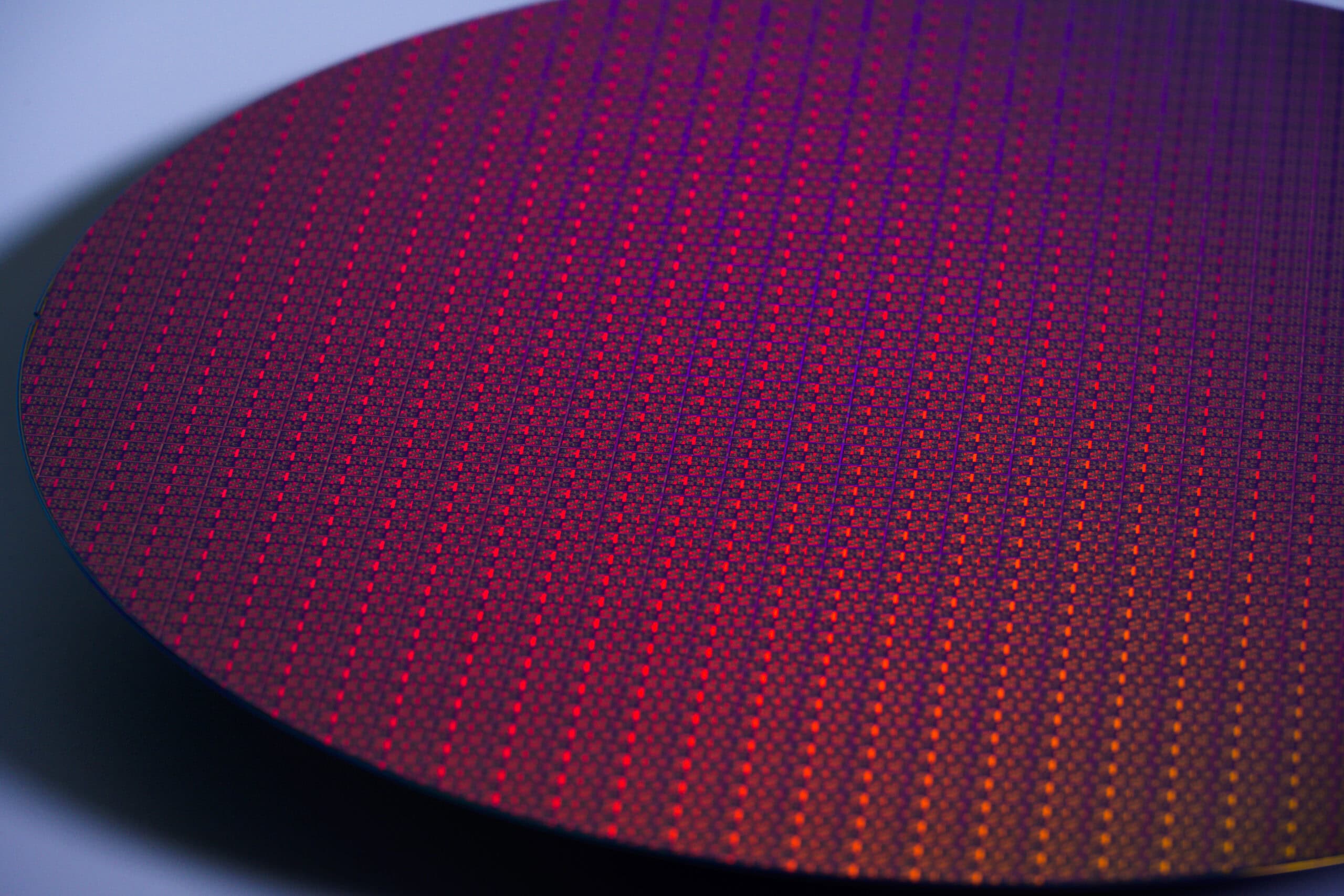

半導体製造プロセスにおける歩留まりを理解する上で最も重要な指標が、単位面積あたりの欠陥密度(defect density:D0)である。2023年9月時点での Intel 18Aプロセスの欠陥密度は0.4 def/cm²を記録している。これはTSMCの同時期における N7/N5プロセスの0.33 def/cm²と比較してやや高いものの、量産開始前の段階としては許容範囲内とされる数値だ。業界では一般的に0.5 def/cm²以下であれば良好な製造プロセスとして評価される。

歩留まりの計算には複数の数理モデルが用いられており、その代表的なものがポアソン収率モデル(Poisson Yield Model)である。このモデルは欠陥がランダムに分布すると仮定し、Y = e^(-AD)という数式で表現される。ここでYは歩留まり、Aはチップ面積、Dは欠陥密度を示す。ただし、実際の製造現場では欠陥がランダムではなくクラスター化する傾向があるため、ポアソンモデルは実際の歩留まりを過度に悲観的に見積もる傾向がある。

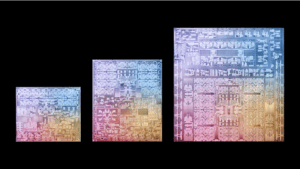

チップサイズによる歩留まりの違いを具体的に見てみよう。大規模なAIアクセラレータチップの場合、その面積は800mm²に達することもある。これはEUVリソグラフィの露光限界である858mm²に迫る大きさだ。このサイズのチップでは、0.4 def/cm²の欠陥密度の場合、300mmウェハーあたり約59-65個のダイ(チップ候補)が取れ、そのうち完全な状態で製造できるのは約5個、歩留まりにして約9%となる。一方で、同じ製造プロセスでもスマートフォン向けプロセッサ(約105mm²)の場合、一枚のウェハーから625個のダイが取れ、そのうち387個が完全な状態で製造可能となり、歩留まりは68.2%に達する。

さらに実際の製造では、各半導体メーカーは独自の冗長設計技術を導入している。これにより、物理的な欠陥があっても機能的に問題のない製品として出荷できるチップの割合は、理論値よりも大幅に向上する。例えばNVIDIAやBroadcomのような大規模チップメーカーは、この冗長設計によって歩留まりを実質的に改善し、ウェハーあたり20,000ドルという高額な製造コストを経済的に成立させている。

これらの技術的背景を踏まえると、現時点での18Aプロセスの欠陥密度は、決して致命的な問題ではないと評価できる。特に小規模から中規模のチップ製造においては、十分に実用的な歩留まりを達成できている。また、製造プロセスは継続的に改善され、欠陥密度は時間とともに低下していく傾向にあることから、量産開始時期までにはさらなる向上が期待できる状況だ。

半導体製造プロセスの複雑性と歩留まり改善の取り組み

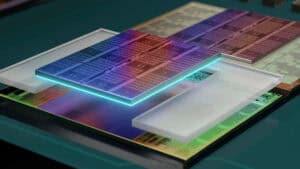

半導体製造における歩留まり向上は、設計段階から製造後の評価に至るまで、複数の層が重なり合う複雑なプロセスとして進められる。その中核となるのが、フォトマスクと呼ばれる原版の設計だ。現代の最先端プロセスでは、EUVリソグラフィの制限により、フォトマスクのサイズは858mm²(26×33mm)が上限となっている。このサイズ制限の中で、いかに効率的に製造可能な設計を実現するかが、歩留まり向上の重要な鍵となる。

設計段階での最も重要な取り組みが、冗長性の実装である。例えばNVIDIAのような大規模チップメーカーは、チップ内の特定の領域に欠陥が発生しても、その機能を別の領域で代替できるような設計を採用している。これは一見すると無駄に思えるかもしれないが、TSMCのような製造委託先に支払うウェハあたり20,000ドルという製造コストを考慮すると、経済的に合理的な選択となる。実際、この冗長設計により、理論上の歩留まりを大幅に上回る実用的な製品歩留まりを達成している。

製造プロセスの最適化も継続的に行われている。半導体の製造では、シリコンウェハー上に特定のパターンを転写する際、配線やトランジスタの配置によって欠陥の発生率が大きく変動する。製造開始後も、これらのパターン配置の微調整や製造条件の最適化を繰り返すことで、徐々に歩留まりが改善されていく。時には、量産開始後でも設計の一部を変更して歩留まりを向上させることもある。

Intel の18Aプロセスの場合、現在はPDK(Process Design Kit)1.0のリリース前の段階にある。PDKとは、半導体設計に必要な各種パラメータや設計ルールをまとめたツールキットであり、これを用いて顧客企業は自社製品の設計を最適化することができる。PDK 1.0のリリース後は、顧客企業による設計最適化と、Intelによる製造プロセスの改善が並行して進むことで、さらなる歩留まり向上が期待できる。

また、製造プロセスの進化は製造開始後も継続する。2023年8月時点で報告された0.4 def/cm²という欠陥密度は、その後の製造条件の最適化により、さらなる改善が見込まれる。半導体製造プロセスは、製造準備が整った後でも継続的な進化を遂げることが一般的だからだ。この観点からすれば、量産開始前の現時点での数値を過度に悲観的に評価することは適切ではないと言える。

半導体製造の改善サイクルは、世界で最も複雑な製造業の一つとされる半導体産業ならではの特徴を持っている。その改善には時として数年単位の時間が必要となり、短期的な成果を求めるビジネス的な要請との間でしばしば軋轢を生む。Pat Gelsinger氏の指摘する「半導体製造のサプライチェーンの修復には年単位の時間が必要」という主張は、このような産業の特性を反映したものと理解できる。

Xenospectrum’s Take

半導体製造における歩留まり問題は、単純な数値だけでは評価できない複雑な課題である。Gelsinger氏の反論は技術的な根拠に基づいており、初期段階の18Aプロセスが示す0.4 def/cm²という数値は、決して致命的な問題ではない。

しかし皮肉なことに、この技術的な成果を示しながらもGelsinger氏自身はCEOの座を追われることとなった。半導体業界の回復には「年単位の時間」が必要だという彼の主張は正しいかもしれないが、ビジネスの世界では必ずしも技術的な正しさだけが評価されるわけではない。今後、Intel 18Aプロセスの真価が問われるのは、外部顧客からの評価においてであろう。

Sources

コメント