TSMCは、2024年度のテクノロジーシンポジウムにおいて、新たに1.6nmプロセス「A16」を発表したが、同社はこのA16において、初のBSPDN(Back Side Power Delivery Network)の実装を発表した。これはつまり、これまでに発表されていた2nm世代の「N2」プロセスでのBSPDN採用を見送る事に外ならないが、その他にもN2製造プロセスの大幅な改善を発表している。

TSMC 「N2」プロセスシリーズ(N2、N2P、N2X)はNanoFlexに対応へ

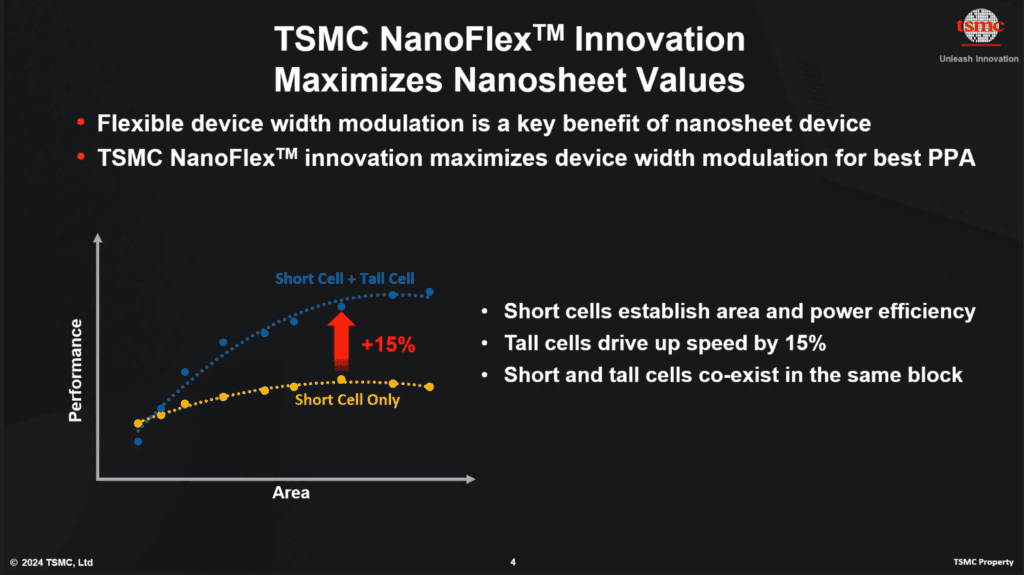

Anandtechによると、これまで計画されていた「N2」プロセスシリーズ(N2、N2P、N2X)はすべて「NanoFlex」に対応するという。これにより、チップ設計者は同じブロック設計内で異なるライブラリ(高性能、低消費電力、面積効率)のセルを混在させ、組み合わせることができるようになる。

N2の製造工程はすべて新しいナノシート・トランジスタ(GAAFET)に依存するため、TSMCはFinFlex技術をさらに発展させ、新しいトランジスタ用のNanoFlexとして機能するようにした。機能領域にもよるが、NanoFlexテクノロジーにより、チップは15%高速化されるか、より高い効率が確保されるはずだ。

N2での生産は2025年にリスク生産に入る予定である。TSMCは、今年後半に量産が開始されると見込んでいる。これらのチップを搭載した最初のデバイスは、2026年以降に登場する予定だ。性能強化された「N2P」と電圧最適化された「N2X」がその直後に続くと予想される。そしてTSMCはその後、A16で初めてSper Power Rail (SPR)経由でBSPDNを利用することになる。

すでに述べたように、ナノシートトランジスタはN2で初めて使用される。より優れた安定供給を可能にするため、TSMCはSHPMIM(Super-High-Performance Metal-Insulator-Metal)キャパシタを採用し、電源レベルに組み込んでいる。Intelでは、こうした同様に設計された部品をMIM(Super Metal Insulator Metal)と呼んでいる。TSMCが現在使用しているSHDMIM(Super-High-Density Metal-Insulator-Metal)コンデンサと比較すると、新しいSHPMIMコンデンサは低抵抗で2倍の静電容量を持つ。

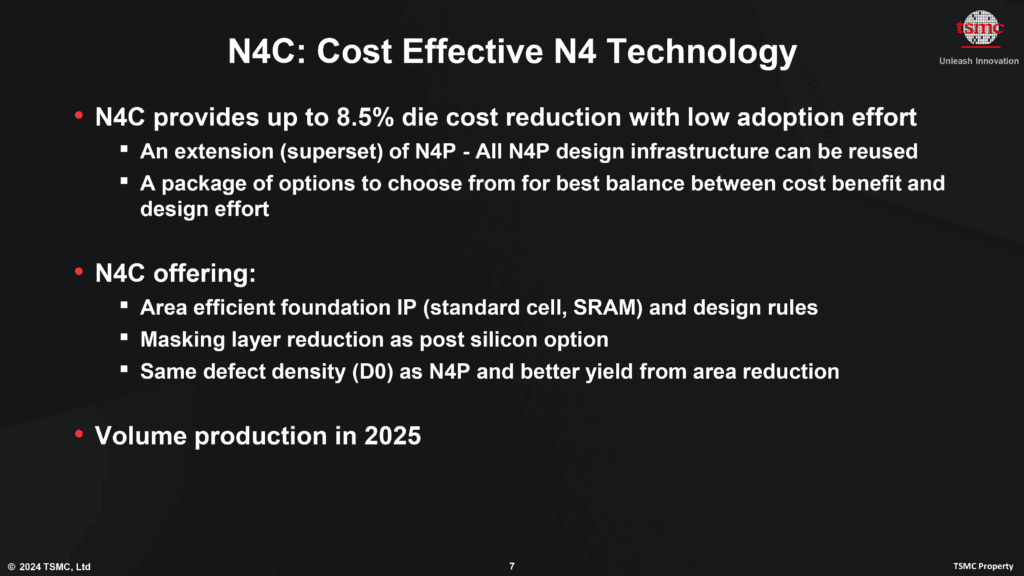

2025年に低コストのN4Cプロセスを計画

TSMCは、2025年に向けた低コストのN4Cプロセスも発表した。他のN4ファミリーと同様、これは5nmプロセスをベースとしている。TSMCは、スタンダード・セルとSRAMセルにN4C用の新しい設計を採用し、N4Cでのウェハー製造コストを8.5%削減した。もう一つの要因はマスク層の削減である。

現在N4Pで製造されているチップは、簡単にN4Cに移行できる。TSMCは、歩留まりが向上し、N4Pと同じ欠陥密度(D0)が得られるとしている。さらに、顧客はチップ設計をN4Pで製造したことがなくても、N4Cに直接移行することができる。N4Cによる最初のチップの量産開始は2025年を予定している。

加えてTSMCは、AIブームによる大きな需要に対応するため、Compact Universal Photonic Engine(COUPE™)技術を開発しているという。COUPEは、SoIC-Xチップ積層技術を使用してフォトニックダイの上に電気ダイを積層することで、ダイ間インターフェイスのインピーダンスを最低限に抑え、従来の積層方法よりも高いエネルギー効率を実現するものだ。TSMCは、2025年にCOUPEをスモールフォームファクタプラグケーブル向けに認定し、その後2026年にCPO(Co-Packaged Optics)としてCoWoSパッケージに統合し、光接続をパッケージに直接組み込む計画である。

Sources

コメント