CadenceはPCI-SIG DevCon 2024で、市販の部品を使用して、128GT/sを達成する世界初のPCIe 7.0光インターコネクションを実演した。

Cadenceの最新PCIe 7.0用IPが驚異的な高速化と効率化を目指す

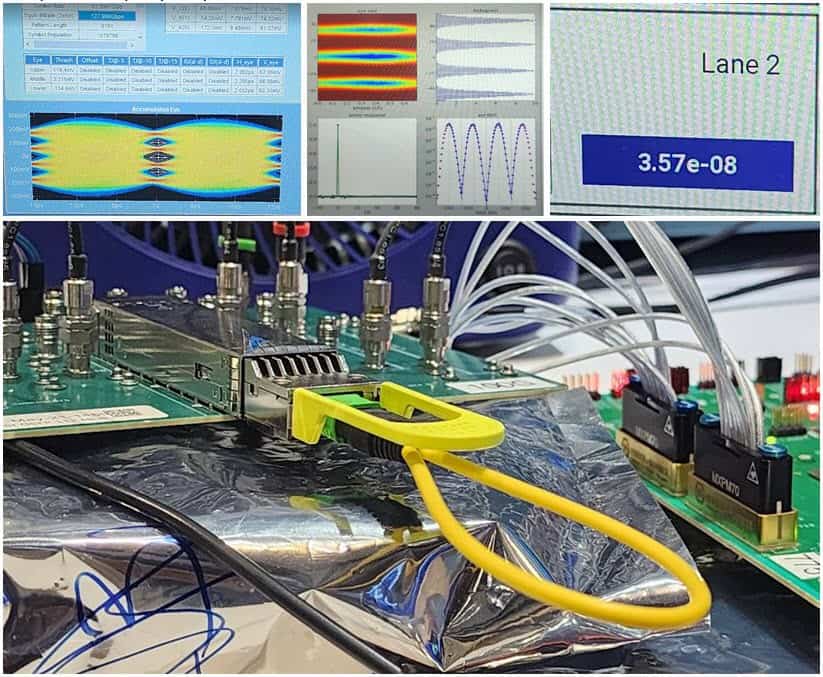

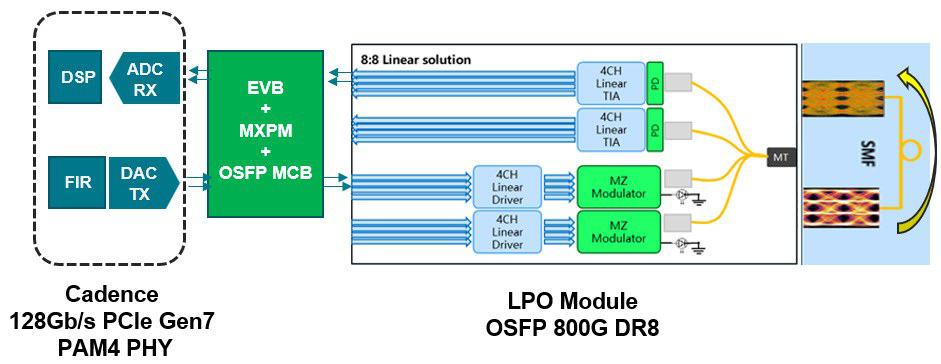

イベント中、Cadenceは実世界で低遅延かつリタイミングなしの線形光接続を使用して、128 GT/sのPCIe 7.0 IPの送受信能力を実演した。このセットアップは、一貫してプレFEC BER ~3E-8を達成し、PCIe仕様要件である1E-6以内に収まっており、コンベンションが開催されている2日間に渡って途切れることなく接続が維持され、標準の光コネクタを使用した128 GT/sの最初の安定したデモンストレーションとなった。Cadenceが示した受信機のEye PAM4ヒストグラムは、優れた線形性とマージンを示している。

光PCIeコネクタは、ハイパースケール、クラウドコンピューティング、HPC、データセンターなどのエンタープライズアプリケーションを対象としている。CopperLinkの代替として、サーバーおよびデータセンターのビルダーに、優れた速度と帯域幅の選択肢を提供することができるかもしれない。

これまで、PCI Expressは銅のインターコネクションにのみ依存していたが、昨年8月に業界標準の光インターフェースを通じてPCIeを実現するための光ワーキンググループを設立し、開発を進めている。

ちなみに、銅接続の新たなPCI-Expressの相互配線規格「CopprLink」の仕様も既に発表され、こちらではPCIe 5.0および6.0に対してそれぞれ32または64 GT/sの接続を可能にするように設計されている。新たな光技術はPCIe 6.0および7.0に対応するが、Cadenceが実演した驚異的な128 GT/sは7.0でのみ可能だ。

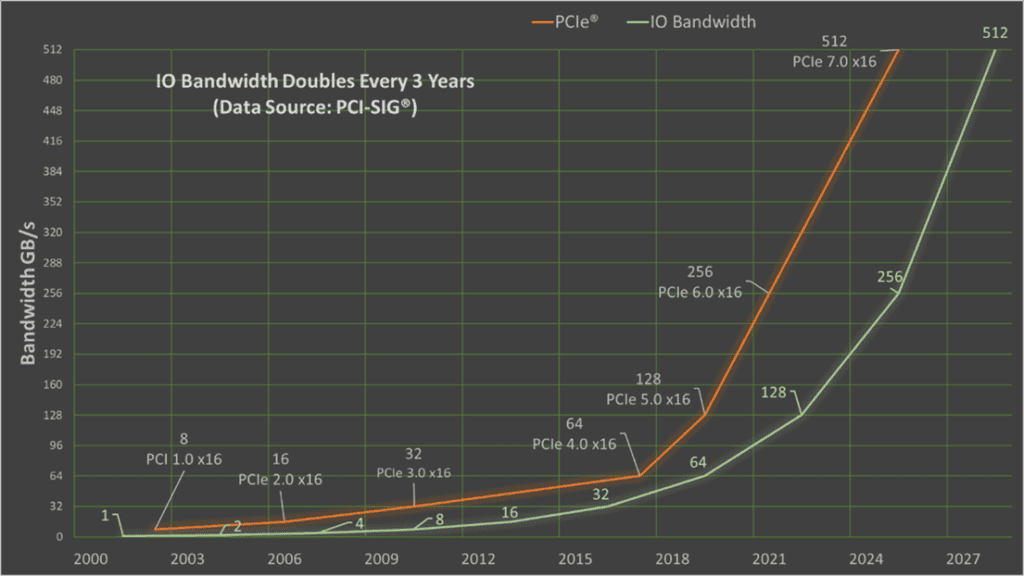

現在ハイエンドコンシューマーPCは現在、主にSSDの読み取り速度を10 GB/s以上に引き上げるために、PCIe 5.0を利用している。PCI-SIGは2022年初頭にPCIe 6.0の完全な仕様を公開し、この標準が2024年から2025年にかけてエンタープライズハードウェアに登場し始めるかもしれない。

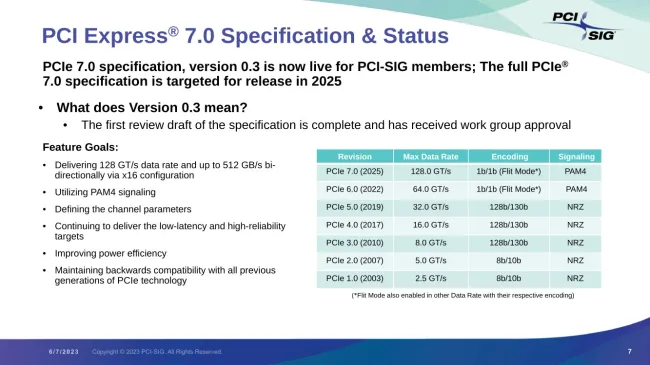

一方、PCIe 7.0のドラフト仕様はバージョン0.5に更新され、最終仕様は来年に発表される予定だ。PCI-SIGグループは当初、2027年に実世界のハードウェアが出現し始めることを意図していたが、現在は2028年まで登場しないと見られている。

PCIe 6.0および7.0の仕様は、それぞれx16レーンで256 GB/sおよび512 GB/sまでの帯域幅をサポートする。これらの革新には、4レベルのパルス振幅変調(PAM4)、軽量フォワードエラー訂正(FEC)、巡回冗長検査(CRC)、およびフロー制御ユニット(Flits)が含まれる。Cadenceは複数のDevConブースでPCIe 6.0のFlitsおよびその他の新機能を実演した。

Sources

コメント