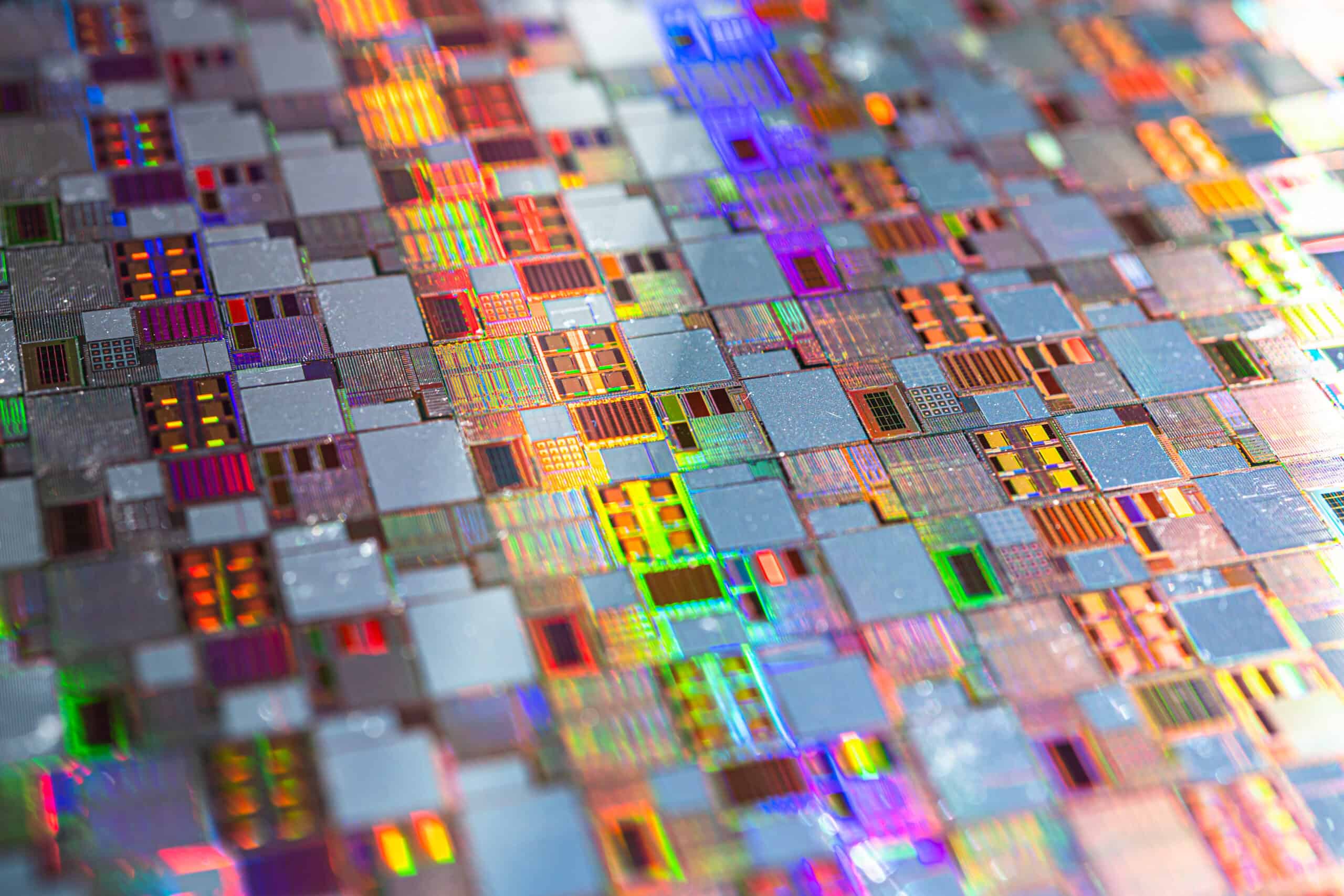

UCIe(Universal Chiplet Interconnect Express)Consortiumは、半導体業界に大きな影響を与える可能性のある「UCIe 2.0」仕様を新たに発表した。この新仕様は、チップレット間の相互運用性を大幅に向上させ、3Dパッケージングをサポートすることで、次世代のシステムインパッケージ(SiP)設計に新たな可能性を開くものだ。

様々なチップレットにまたがる管理アーキテクチャと3Dパッケージングを標準化

UCIe 2.0仕様の最も注目すべき点は、標準化された管理システムアーキテクチャの導入だ。これにより、複数のチップレットにまたがるSIPライフサイクル全体にわたって、テスト容易性、管理性、デバッグ(DFx)の設計課題に対する統合的なアプローチが可能となる。この新しいアーキテクチャは、チップの製造時の選別から実際の運用管理に至るまで、一貫したフレームワークを提供する。

またUCIe 2.0では、オプションの管理機能とUCIe DFxアーキテクチャ(UDA)が導入された。UDAには各チップレット内にテスト、テレメトリ、デバッグ機能のための管理ファブリックが含まれており、ベンダーに依存しないチップレットの相互運用性を実現する。これにより、SiP管理とDFx操作に対する柔軟で統一されたアプローチが可能となり、異なるベンダーのチップレットを組み合わせた複雑なシステムの開発と管理が容易になる。

さらに、UCIe 2.0仕様は3Dパッケージングをサポートした。この3Dパッケージング技術は、従来の2Dおよび2.5Dアーキテクチャと比較して、より高い帯域幅密度と改善された電力効率を提供する。UCIe-3Dは、ハイブリッドボンディングに最適化されており、10-25ミクロンから1ミクロン以下までの幅広いバンプピッチに対応する。この柔軟性とスケーラビリティにより、多様な設計要件に適応することが可能となる。

UCIe 2.0仕様のもう一つの重要な側面は、相互運用性とコンプライアンステストのためのパッケージ設計の最適化である。これにより、テスト対象デバイス(DUT)のメインバンドサポート機能を、既知の良好なUCIe実装と比較して検証することが可能となる。UCIe 2.0は、物理的、アダプタ、およびプロトコルコンプライアンステストの初期フレームワークを確立しており、これは業界全体での一貫性と信頼性を確保する上で重要な役割を果たす。

UCIe Consortium会長であり、Samsung ElectronicsのCorporate VPであるCheolmin Park氏は、この新仕様の意義について次のように述べている:「UCIe Consortiumは、急速に変化する半導体業界のニーズに応えるため、多様なチップレットをサポートしています。UCIe 2.0仕様は、包括的なソリューションスタックを開発し、チップレットソリューション間の相互運用性を促進することで、以前の反復に基づいて構築されています。これは、コンソーシアムが繁栄するオープンチップレットエコシステムに献身していることを示すもう一つの例です。」

UCIe 2.0仕様は、UCIe 1.1およびUCIe 1.0との完全な後方互換性を維持しており、既存のシステムとの統合を容易にしている。これにより、企業は新しい技術を段階的に採用しながら、既存のインフラストラクチャを活用し続けることができる。

この新仕様の影響は、理論的な改善にとどまらない。2024年8月6日から8日にかけて開催されるFuture of Memory and Storage (FMS)イベントにおいて、UCIe Consortium会長のDr. Debendra Das Sharma氏が新仕様の特徴について講演を行う予定だ。この講演は、業界関係者にUCIe 2.0の実際の適用と潜在的な影響について深い洞察を提供するものと期待されている。

UCIe 2.0仕様の発表は、半導体業界におけるチップレット技術の重要性が急速に高まっていることの現れと言えるだろう。UCIe 2.0により、異なるベンダーのチップレットを組み合わせたより複雑で効率的なシステムの開発が可能となり、次世代の高性能コンピューティングシステムの実現に向けた重要な一歩となることが期待出来る。さらに、この標準化されたアプローチにより、チップレット技術の革新が加速し、より柔軟で拡張性の高いシステム設計が可能になるだろう。

今後、UCIe 2.0仕様の採用が進むにつれ、半導体業界はより高度な集積回路の設計と製造が可能になり、AI、データセンター、エッジコンピューティングなどの分野で新たな可能性が開かれることが予想される。

Sources

コメント