北京大学の研究チームが、シリコンを使用しない世界初の2次元ゲートオールアラウンド電界効果トランジスタ(2D GAAFET)の開発に成功した。このビスマスベースの新技術は、Intel、TSMC、Samsungなどの最先端3nmシリコンチップと比較して40%の性能向上と10%のエネルギー削減を実現したと報告されている。

革新的な「レーン変更」アプローチ

北京大学の物理化学教授である彭海琳(Peng Hailin)氏とQiu Chenguang氏が率いる研究チームは、この新技術を「既存材料に基づくチップ革新が『近道』と考えられるのに対し、2D材料ベースのトランジスタの開発は『レーン変更』に似ている」と位置づけている。

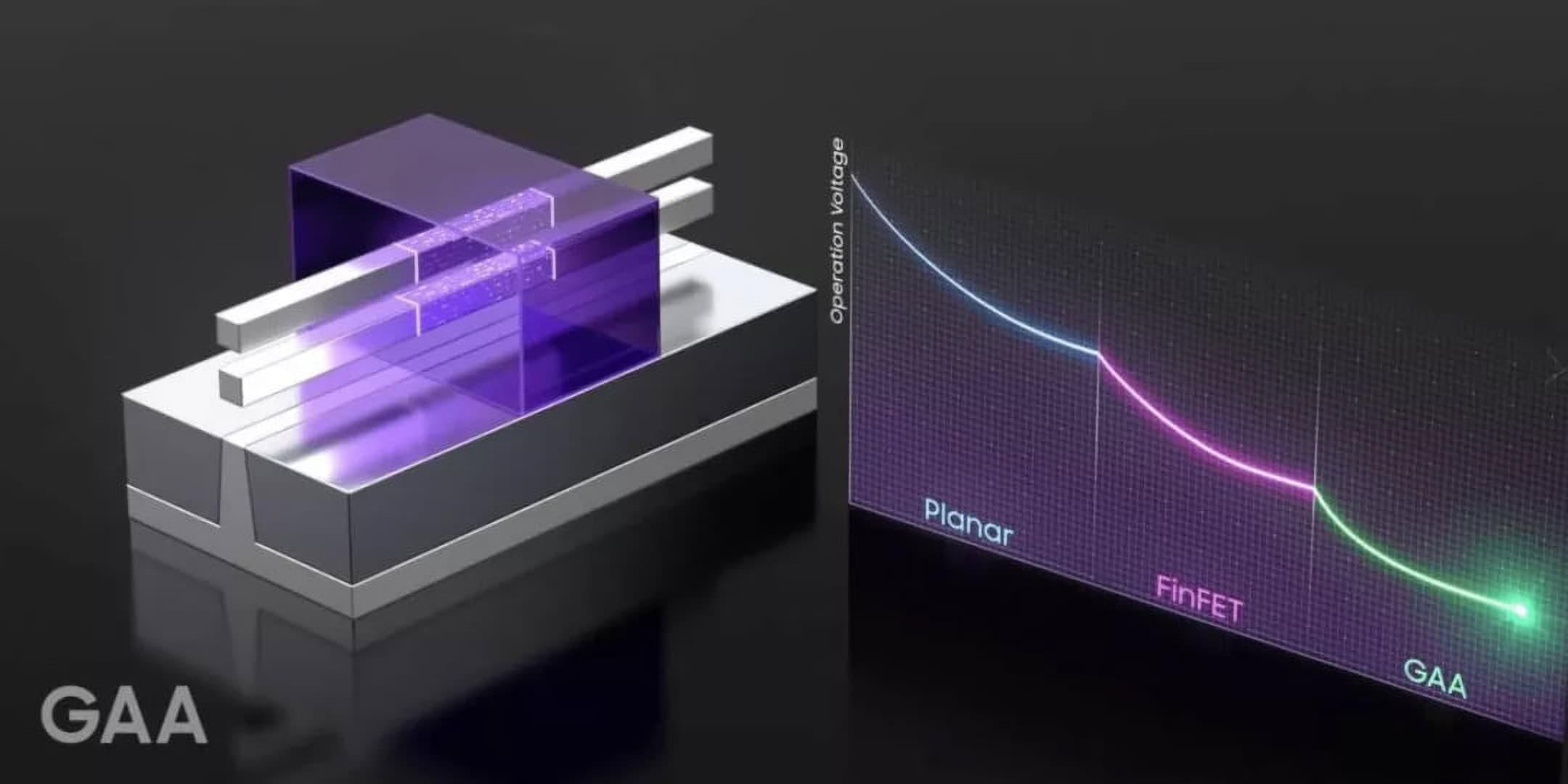

従来のシリコンベースの半導体は極小化に伴い、特定のサイズ以下になると消費電力の増加や性能低下などの物理的限界に直面していた。これに対し、研究チームが開発したGAAFET(ゲートオールアラウンド電界効果トランジスタ)技術は、従来のFinFET(フィン電界効果トランジスタ)構造と根本的に異なるアプローチを採用している。

「これは史上最速かつ最も効率的なトランジスタだ」と彭教授は北京大学のWebサイトで発表した声明で述べている。

技術的ブレイクスルーの詳細

新開発されたトランジスタは、半導体材料としてビスマスオキシセレニド(Bi₂O₂Se)、高誘電率酸化物材料としてBi₂SeO₅を使用している。これらの材料は彭教授のチームが10年前に発見し、研究を重ねてきたものである。

従来のFinFETは、2011年にIntelが商業化して以来、22nmから3nmまでチッププロセスを進化させてきたが、3nm以下への微細化に限界が見えていた。新しいGAAFET構造は基礎となる「フィン」を完全に排除し、ゲートとチャネル間の接触面積を増加させている。研究者はこの変化を、「高層ビルから編み込まれた橋」への転換に例えている。

重要な技術的優位性として、Bi₂O₂Se/Bi₂SeO₅材料界面のエネルギーが他の一般的な半導体-酸化物界面よりも著しく低く、これにより電子散乱と電流損失が減少し、「ほとんど抵抗なしに電子が流れることができる」点が挙げられる。

米中技術競争下での戦略的意義

この技術開発は、米国主導の制裁により中国が最先端のシリコンベース半導体製造技術へのアクセスを制限されている中で行われた。特にEUVリソグラフィーなどの先端製造装置へのアクセスが制限される中、中国は代替技術の開発に注力している。

「この道は現在の制裁のために必要に迫られたものだが、研究者に新しい視点から解決策を見つけることを強いている」と彭教授は指摘している。

中国が単に既存技術の改良(追いつき)を目指すのではなく、まったく新しい技術的アプローチ(レーン変更)を開拓することで、半導体技術における独自の道を切り開こうとしている点は注目に値する。

実用化への道と今後の展望

研究チームは既に、この新しいトランジスタ技術を用いて小規模な論理ユニットを構築し、超低電圧動作での高い電圧ゲインを実証している。これにより、回路性能の向上、消費電力の削減、ノイズ耐性の強化などが期待できる。

現在、研究チームはこの技術の量産化に向けて取り組んでおり、製造精度が向上するにつれて性能指標がさらにシリコンデバイスを上回ると予測している。

この研究成果は『Nature Materials』誌に掲載され、「2D GAAFETは商業用シリコンベースのトランジスタに匹敵する性能とエネルギー効率を示し、次の技術ノードの有望な候補である」と結論づけている。

論文

参考文献

- South China Morning Post: ‘Changing lanes’: China heralds fastest-ever chip technology – without silicon