PCI-SIG(PCI Special Interest Group)は、次世代PCIeインターフェース規格となる「PCIe 7.0」の仕様ドラフトバージョン0.7をリリースした。2025年の正式リリースを目指す本規格は、レーン当たり16GB/sという革新的な帯域幅を実現し、急速に発展するAIワークロードに対応する新たな転送規格として注目を集めている。

安定性を増す仕様策定プロセス

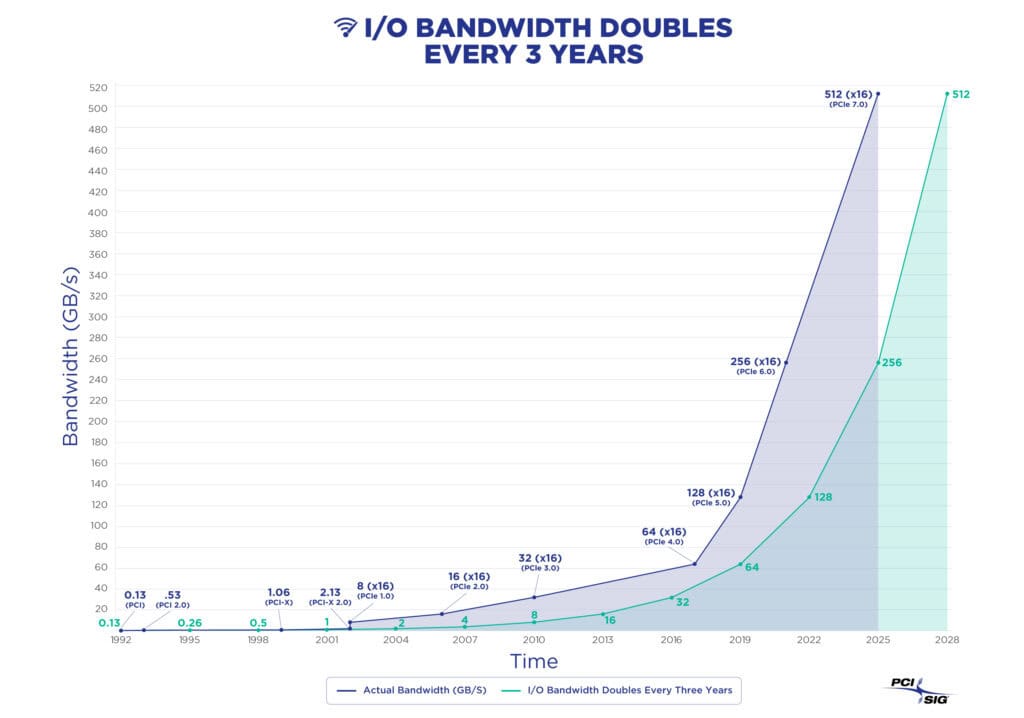

2024年4月にリリースされたバージョン0.5から大きな変更点が見られないことは、基幹技術の安定性を示す重要な指標となっている。PCI-SIGは3年サイクルでの新規格リリースを目標に掲げており、PCIe 7.0仕様もこのスケジュールに沿って着実に進展している。

革新的な性能向上と技術的特徴

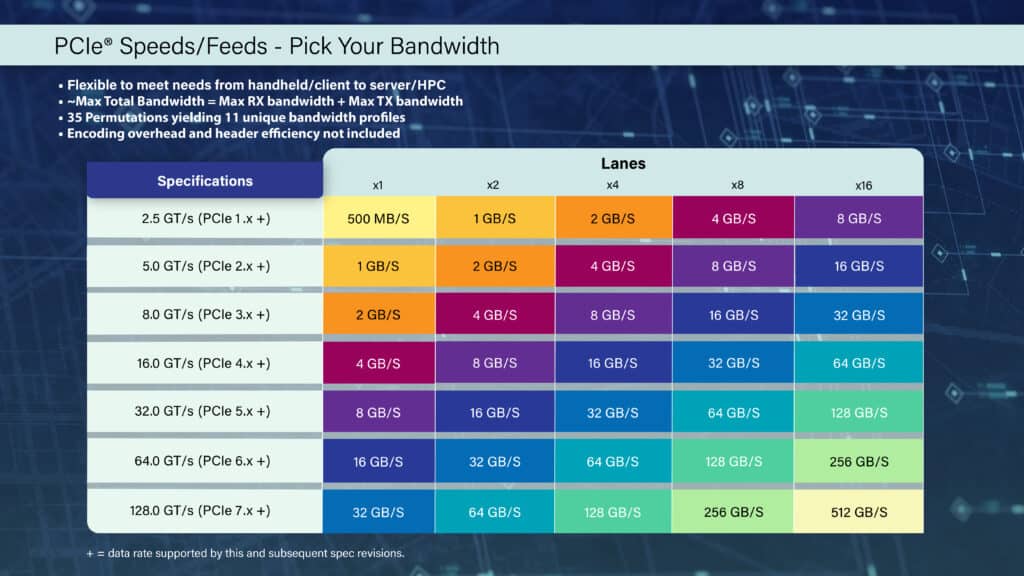

PCIe 7.0の最大の特徴は、PCIe 6.0から倍増となる128GT/sの生データ転送レートだ。これは16レーン構成において最大512GB/sの双方向転送速度を実現する画期的な仕様となる。この進化を歴史的な文脈で見ると、PCIe 5.0が1レーン当たり4GB/sだったことを考えれば、わずか2世代で転送速度が4倍に向上したことになる。

この驚異的な性能向上を技術面で支えているのが、PCIe 6.0から導入されたPAM4(Pulse Amplitude Modulation with 4 levels)シグナリング技術だ。従来のPCIe 4.0やPCIe 5.0で採用されていたNRZ(Non-Return-to-Zero)方式と比較して、PAM4は1クロックサイクルあたり2ビットのデータエンコードを実現する。これにより、物理的な信号周波数を上げることなく、実効的なデータ転送速度を2倍に高めることに成功している。

さらにPCIe 7.0では、チャネルパラメータと到達距離の最適化に特に注力している。高速なデータ転送では信号の減衰や干渉が大きな課題となるが、新仕様ではこれらの問題に対する改善が図られている。同時に、すべての世代のPCIe技術との下位互換性を維持しながら、低レイテンシーと高信頼性という相反する要求にも対応している。

電力効率の改善も見逃せない特徴だ。データセンターやクラウドコンピューティング環境では、増大する帯域幅要求に対して電力消費を抑制することが重要な課題となっている。PCIe 7.0では、信号品質を維持しながら、より効率的な電力利用を実現するための最適化が行われている。これは特にAIやML(機械学習)のワークロードにおいて重要性を増している大規模な並列処理において、システム全体の電力効率向上に貢献することが期待される。

このような技術革新により、PCIe 7.0は次世代の高性能コンピューティングインフラストラクチャに必要不可欠な基盤技術として位置づけられる。特に800GイーサネットやAI/ML処理、量子コンピューティングなど、極めて大量のデータ転送を必要とするアプリケーションにおいて、その真価を発揮することになるだろう。

実用化に向けた技術的課題と市場展望

PCIe 7.0の画期的な性能向上は、同時に深刻な技術的課題をもたらしている。その最たるものが熱設計の問題だ。データ転送速度の向上は必然的に発熱量の増加を招き、この熱をいかに効率的に制御するかが実用化への重要な鍵となっている。

この課題に対して、業界は既に具体的な対策の検討を始めている。例えばIntelが開発中のLinux向けPCIeクーリングドライバーが挙げられる。このドライバーは、温度上昇時にPCIeリンク速度を動的に調整することで、熱問題に対する柔軟な対応を可能にする。これは従来になかった画期的なアプローチだが、同時に高速データ転送と熱管理のトレードオフという新たな課題も提起している。

将来的には、内部コンポーネントの設計思想そのものの変革が必要となるだろう。大型のヒートシンクやアクティブクーリングシステムの採用は、もはや選択肢ではなく必須要件となりつつある。これは特にSSDなどのストレージデバイスにおいて顕著で、宣伝したとおりの動作を維持するためには、従来考えられなかったような大規模な冷却機構が必要となる可能性が高い。

このような技術的ハードルは、PCIe 7.0搭載製品の市場投入までの道のりを必然的に長いものとしている。参考として、2022年に仕様が確定したPCIe 6.0は、3年が経過した現在もなお相互運用性テストの段階にある。さらに遡れば、2019年にリリースされたPCIe 5.0規格の製品が実際に市場に登場したのは2023年になってからだ。この長期化の背景には、新規格の実装における複雑な検証プロセスがある。

具体的には、シリコンの製造プロセスの最適化、実環境での信頼性テスト、様々なデバイスとの相互運用性の確認、そして熱設計を含めたプラットフォーム全体の統合検証といった、多岐にわたる工程が必要となる。特にPCIe 7.0では、前述の熱問題に加えて、PAM4シグナリングの高速動作における信号品質の維持も重要な検証項目となる。

さらに、製品化に向けては製造コストの最適化も重要な課題となる。高速データ転送を実現するための精密な回路設計や高品質な基板材料の使用は、必然的にコストを押し上げる要因となる。市場に受け入れられる価格帯を実現するためには、これらの製造コストを適切にコントロールする必要がある。

このように、PCIe 7.0の実用化には数多くの技術的ハードルが存在するものの、AI/MLワークロードの急速な発展に伴うデータ転送需要の増大は、これらの課題を克服する強い推進力となっている。業界全体が直面するこれらの課題に対して、どのような革新的なソリューションが生まれるか、その動向が注目される。

Source

コメント