TSMCは北米技術シンポジウムで、同社の今後の半導体技術とチップパッケージング技術の両方の取り組みについて詳述している。

TSMCがリリースする予定の、BSPDNを採用するA16製造ノードについてはすでに取り上げた。同社はまた、System-on-Wafer(SoW)と名付けられた、300mmウェハーサイズのチップの上に直接ロジックとメモリーを3D積層できる、さらに野心的な技術も発表している。

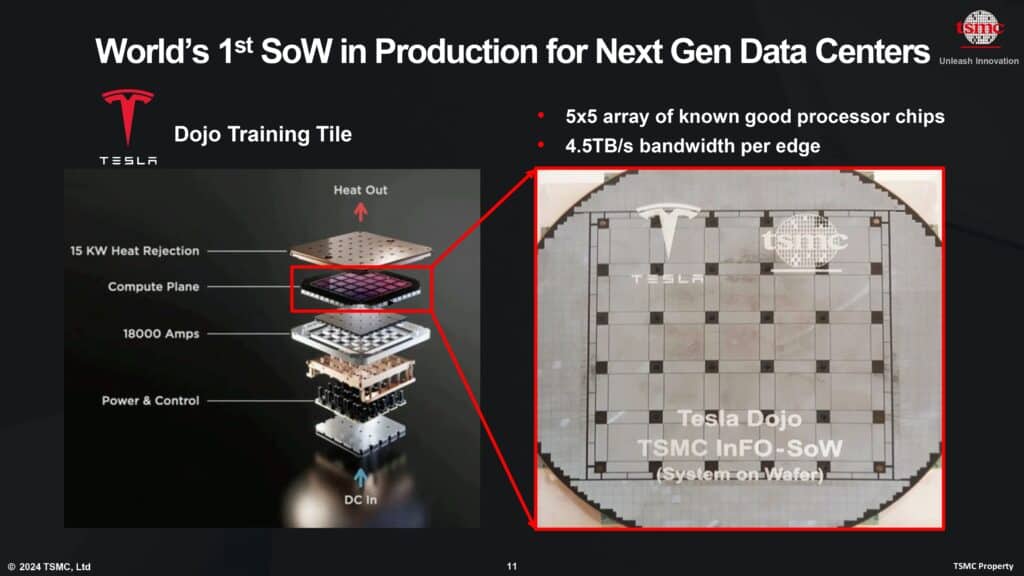

TSMCによると、SoWの初期バージョンは、同社のInFO(Integrated Fan-Out)-SoW設計を用いたロジック専用ウェハーで、すでに生産が開始されている。今のところ、これを用いてウェハースケールのプロセッサー設計を開発したのはCerebras社とTesla社のみだ。これは、性能と電力効率は素晴らしいものの、ウェハースケールのプロセッサーは開発と製造が極めて複雑だからだ。

しかしTSMCは、ウェハースケール設計の利用が拡大するだけでなく、AIやHPCのようなメガトレンドがさらに複雑なソリューション、すなわち垂直スタック型SoW設計を求めるようになると考えている。

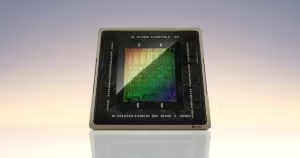

TSMCのInFO-SoW技術に基づくソリューションとして量産が開始された最初のものであるTesla Dojoのウェハースケール・プロセッサは、低レイテンシの高帯域幅コア間通信、非常に高い性能と帯域幅密度、比較的低い電力供給ネットワーク・インペンダンス、高い性能効率、再冗長性など、一般的なSystem-in -Package(SiP)を上回る多くの利点を備えている。

しかし、InFO-SoWやその他のウェハースケールの集積方法では、プロセッサ設計者はオンチップ・メモリだけに頼らざるを得ない。これは多くのアプリケーションには十分だが、次世代のAIワークロードには不十分かもしれない。さらに、InFO-SoWでは、ウェハー全体を1つの製造技術で処理しなければならないため、設計によっては最適でなかったり、コストがかかりすぎたりする可能性がある。

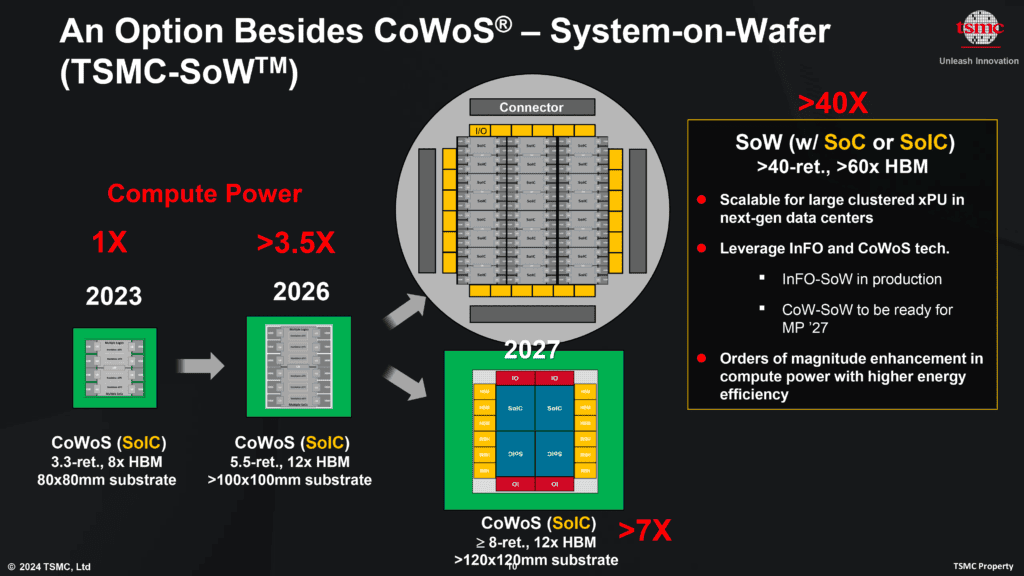

そこでTSMCは、次世代System-on-Waferプラットフォームで、2つのパッケージング技術を統合することを計画している:InFO-SoWとSoIC(System-on-Integrated Chips)である。

これは、既存のSoW設計を採用し、その上にSoICを載せることで、ウェハーサイズのチップの上に直接ロジックとメモリーを積み重ねることを可能にしている。同社は以前からSoW設計を採用していたが、この新バージョンは、高帯域幅メモリー(HBM)製造に使用しているChip-on-Wafer-on-Substrate(CoWoS)技術を統合したものである。そのため、技術略語ではCoWoS_SoWと読む。

これは基本的に、複数の小型ダイを1つのパッケージに統合する典型的なチップレット設計の強化版である。しかし、TSMCはこれを信じられないような新しいレベルの規模と複雑さに引き上げようとしている。

現在のCoWoSは、リソグラフィで使用される一般的なフォトマスクの3.3倍の大きさのインターポーザー(シリコンベース層)をサポートしている。しかし、2026年までにTSMCの「CoWoS_L」はこれを約5.5倍のマスク・サイズに引き上げ、より大きなロジック・チップレットと最大12スタックのHBMメモリーを搭載する余地を残す。そして2027年には、40倍の計算能力、40レチクル分以上のシリコン、60個以上のHBMを搭載するスペースを提供するフルウェハー統合が可能になるとTSMCは予測している。

これはクレジットカードよりもはるかに大きい、6,864mm2に及ぶ集積パッケージの話である。これらのCoWoS巨大パッケージは、12個のHBM4メモリ・スタックと追加のI/Oダイとともに、4個のスタックド・ロジック・チップレットを組み込むことができる。

もちろん、このような大型チップの製造には、TSMCが対処しなければならない以上の結果が伴う。チップ設計者がこのような巨大なプロセッサを構築できるようになれば、システム設計や、データセンターがこのようなシステムに対応する方法にも影響を与えることになる。TSMCの100×100mm基板は、そもそもモジュールのサイズが102×165mmであるOAM 2.0フォームファクターの限界まで乗り上げることになる。そして、その世代のCoWoSが現在のOAMフォームファクターを破らなければ、120×120mmチップは確実に破れるだろう。

基板が大きくなれば、その上に集積できる部品が増え、より強力で複雑な電子デバイスを実現できる可能性がある。しかし、巨大なスケールは、何キロワットもの電力を消費し、エキゾチックな液体冷却ソリューションが必要になる可能性が高いことも意味する。そのため、ハードウェア・ベンダーはすでに、液冷や液浸冷却を調査することで、数キロワットのチップを冷却する方法を準備している。

結局のところ、ムーアの法則がトランジスタ密度の向上を実現するという点では鈍化しているとしても、CoWoSはこれまで以上に多くのトランジスタを搭載したチップを製造するための出口を提供している。TSMCは、現在のソリューションの2倍以上の面積を持つインターポーザーと基板を提供する予定であり、HPCシステム向けの大型チップは、性能とサイズの両方で成長し続けるだろう。

Source

コメント