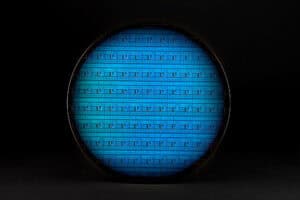

TSMCのN2ノードは2025年後半に登場し、同社初のGAAFETを採用することも合わせて大きな技術的飛躍となるが、同社の発表によれば性能と歩留まりの目標はほぼ達成された様で、当初のスケジュール通りに量産が開始されそうだ。

N2の平均歩留まりは80%近い

AnandTechによれば、TSMCはSymposiums 2024において第1世代2nm「N2」ノードの開発進捗状況を共有し、これが順調に推移していることを確認したと言う。同社、「N2の開発は順調に進んでおり、次はN2Pである」と、既に次の開発に目標を定めているようだ。

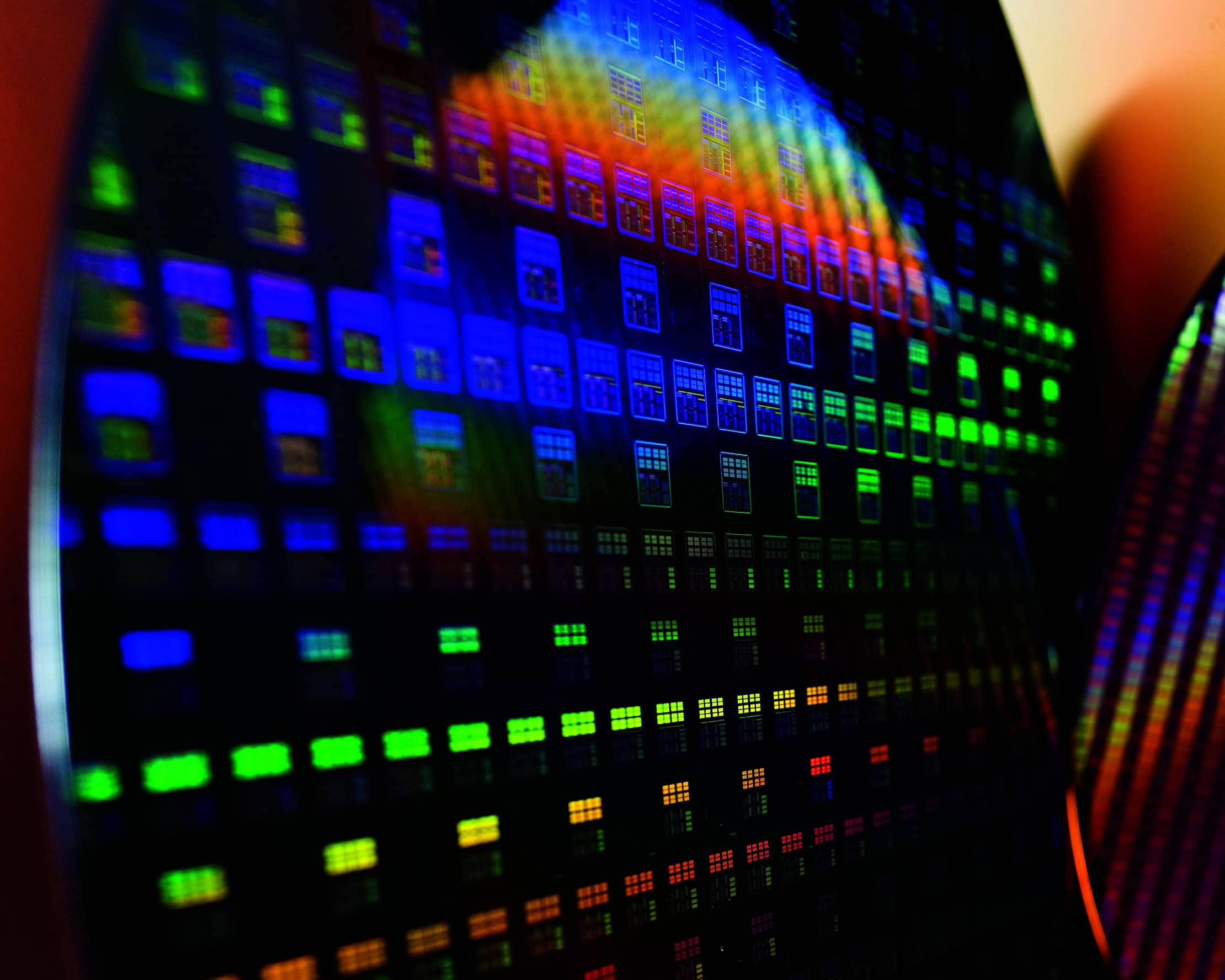

TSMCにとってN2は大きな挑戦となるが、GAAFETによる大きな変更にもかかわらず、現在期待される性能の90%以上を達成しており、256Mb SRAM(32MB)デバイスの歩留まりはバッチによっては80%を超えているという。量産開始までまだ1年以上ある状況での成果であり、今後更にブラッシュアップされていくことが期待される。

2024年3月時点での256Mb SRAMの平均歩留まりも約70%と、およそ1年前の2023年4月の平均歩留まり約35%から2倍近い改善が見られる。デバイスの性能も改善されており、消費電力を抑えながら高い周波数が達成されている。

N2の立ち上げから翌年、2026年後半にTSMCは第2世代2nm「N2P」プロセスを展開する予定であり、ここでは性能の向上、電力効率の改善が期待されている。N2Pは、N3Eと比較して周波数を15%〜20%向上させ、消費電力を30%〜40%削減し、チップ密度を1.15倍以上に増加させることが予想されている。これを可能にするのが、GAAだ。

そしてその後、TSMCは2026年にも1nm領域にまで進出する計画だ。最高の性能、電力効率、および密度を必要とする企業向けに、「A16」(AはオングストロームのA)プロセスを提供する準備を整えている。このノードはバックサイドパワーデリバリーも導入され、コストは増加するものの、性能効率とスケーリングの大幅な向上が期待されている。

TSMCは3nmプロセスも素晴らしい歩留まりを記録しており、歩留まりに悩まされているSamsungを尻目に開発を加速させているようだ。

Source

コメント