TSMCは現在全世界でテクノロジーシンポジウムを開催中だ(6月28日には日本でも開催される)。2nmや1nm世代と言った、最先端プロセスが注目されがちではあるが、同社はInFO、CoWoS、TSMC-SoIC等の先進パッケージング技術についても急速に技術開発を進めており、現在のバンプピッチ9μmから2027年までに3μmピッチまで進化し、A16とN2ダイの組み合わせを積層するロードマップを明らかにしている。

2027年にはA16ダイにN2ダイを組み合わせたチップも可能に

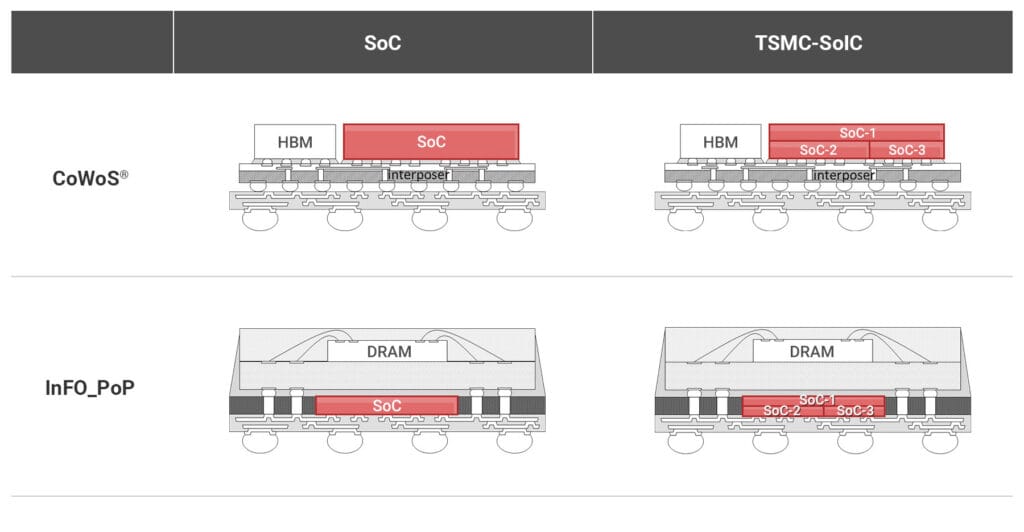

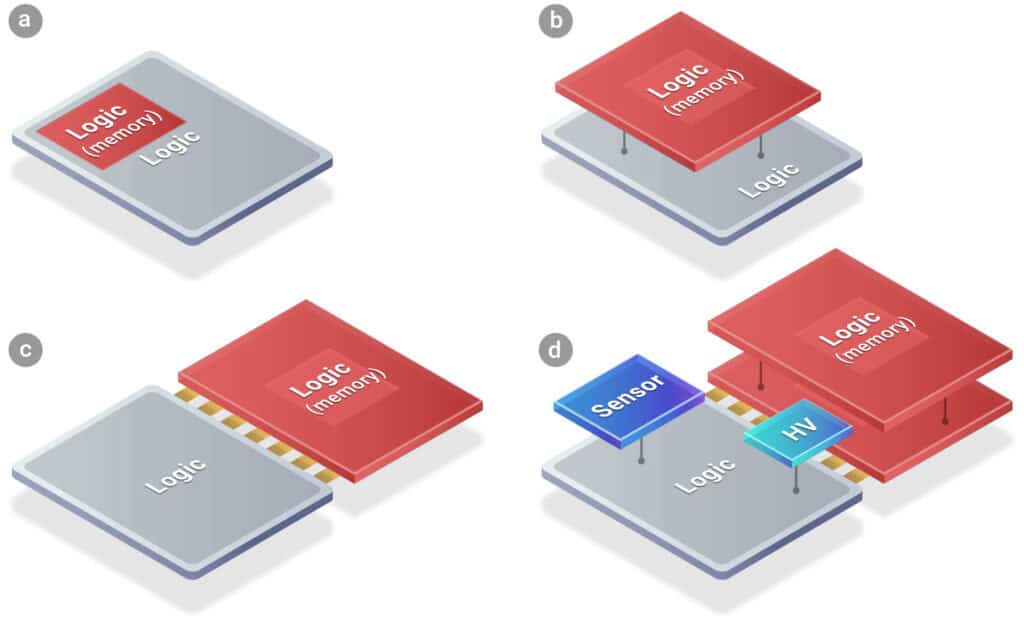

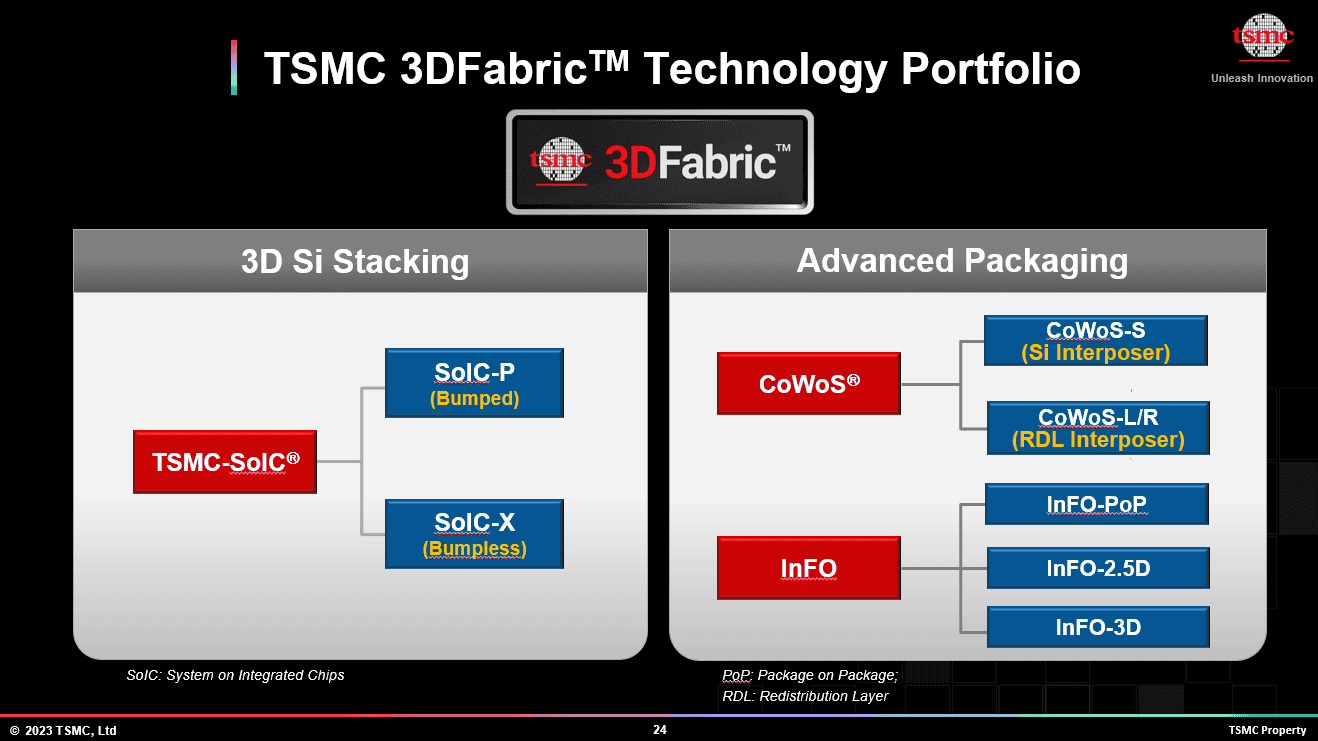

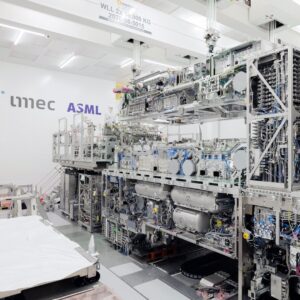

TSMCは、CoWoS(Chip on Wafer on Substrate)やInFO (Integrated Fan-Out)などの先進的なパッケージング技術を有しているが、最も複雑なテクノロジーは、TSMC-SoIC(System on Integrated Chips)だ。このシリコンダイを3次元積層する技術は、ハイブリッドウェハー接合のTSMC版であり、ハイブリッド接合により、2つの先進ロジックデバイスを直接積層し、極めて高密度(かつ超短距離)の接続を実現する。

SoIC技術は、同種のチップと異種のチップの両方を、より小さなフットプリントと薄型の単一のSoCのようなチップに統合する事を可能にし、CoWoSやInFoに統合する事が可能だ。新たに統合されたSoCは外見上は、一般的なSoCチップと同じに見えるが、異種統合機能が組み込まれている。

この技術は主に高性能部品を対象としている。現時点では、SoIC-X(バンプレス)は、AMDのCPU向け3D Vキャッシュ技術やInstinct MI300シリーズのAI製品など、特定の用途に使用されている。ただし、現在は、ダイサイズや相互接続ピッチの制約によって制限されている。

しかし、これらの制約もTSMCによれば急速に解消される見込みとのことだ。SoIC-X技術は急速に進化し、2027年にはTSMCの最先端A16(1.6nmクラス)で製造されたレチクルサイズのトップダイと、TSMCのN2(2nmクラス)で製造されたボトムダイを組み合わせたチップが組み立て可能になるという。このダイは、現在の9μmピッチの3倍の密度を持つ3μmのボンドピッチTSV(スルーシリコンビア)で接続される。このような小さな相互接続により、全体の接続数が大幅に増加し、組み立てられたチップの帯域幅密度(および性能)が大幅に向上する。

改良されたハイブリッド接合技術により、TSMCの大手HPC顧客(AMD、Broadcom、Intel、NVIDIAなど)は、大規模で超高密度の分離型プロセッサデザインを構築することが可能になる。これにより、ダイ間の距離と全体のフロアスペースが重要なアプリケーションにも対応できるようになる。一方、性能のみが重要なアプリケーションでは、複数のSoIC-XパッケージをCoWoSインターポーザに配置し、より低い消費電力で性能を向上させることができる。

TSMCは、極限性能を必要とするデバイス向けのバンプレスSoIC-Xパッケージング技術の開発に加えて、近い将来にバンプ付きSoIC-Pパッケージングプロセスも開始する予定である。SoIC-Pは、より低価格で低性能なアプリケーション向けに設計されており、3D積層を希望するが、バンプレスの銅対銅TSV接続に伴う追加の性能と複雑さを必要としない場合に適している。このパッケージング技術により、より広範な企業がSoICを活用できるようになり、低価格版の技術により、コストを重視する消費者向けアプリケーションにも利用できる可能性がある。

TSMCの現行計画によれば、2025年までに0.2レチクルサイズのN3(3nmクラス)トップダイとN4(4nmクラス)ボトムダイを25μmピッチのマイクロバンプ(µバンプ)で接続可能なフェーストゥバック(F2B)バンプ付きSoIC-P技術を提供する予定とのことだ。2027年には、フェーストゥフェース(F2F)バンプ付きSoIC-P技術を導入し、N2トップダイをN3ボトムダイに16μmピッチで配置することが可能になる。

SoICをチップ開発者の間でより普及させ、利用しやすくするためには、多くの作業が必要であり、ダイ間インターフェースの改善を続ける必要がある。しかし、TSMCはSoICの採用に対して非常に楽観的であり、2026年から2027年にかけて約30のSoICデザインがリリースされると予想している。

Sources

- AnandTech:

コメント