エレクトロニクス機器のエネルギー効率を向上させるため、マイクロチップ上に直接エネルギーを蓄えることが出来るコンデンサを組み込む研究が進められている。これは未だ達成されていない目標であるが、今回Lawrence Berkeley National Laboratory (Berkeley Lab) とUC Berkeleyの研究者らは、この実現への道を切り拓く、画期的なマイクロキャパシタの開発に成功した事を報告している。

マイクロチップ技術のブレークスルー

マイクロチップに直接エネルギー貯蔵機能を組み込むことは、エレクトロニクス分野で大きな変革をもたらす可能性を秘めている。マイクロチップ上にコンデンサを組み込む事で、エネルギー輸送経路の大幅な短縮に繋がるのだ。これは、電力を輸送する際に必ず発生するエネルギーの損失を削減することにつながり、大幅な電力の削減が期待出来るが、マイクロチップ上という非常に小さなスペースに大量のエネルギーを蓄えるという非常に困難な課題が待ち受けている。

今回、Berkeley Lab とUC Berkeleyの研究者らは、既存の半導体チップ製造技術と、よく用いられる材料であるハフニウム酸化物(HfO2)とジルコニウム酸化物(ZrO2)を用いて、記録的なエネルギー密度と電力密度を保持出来るマイクロコンデンサの開発に成功した事を報告している。

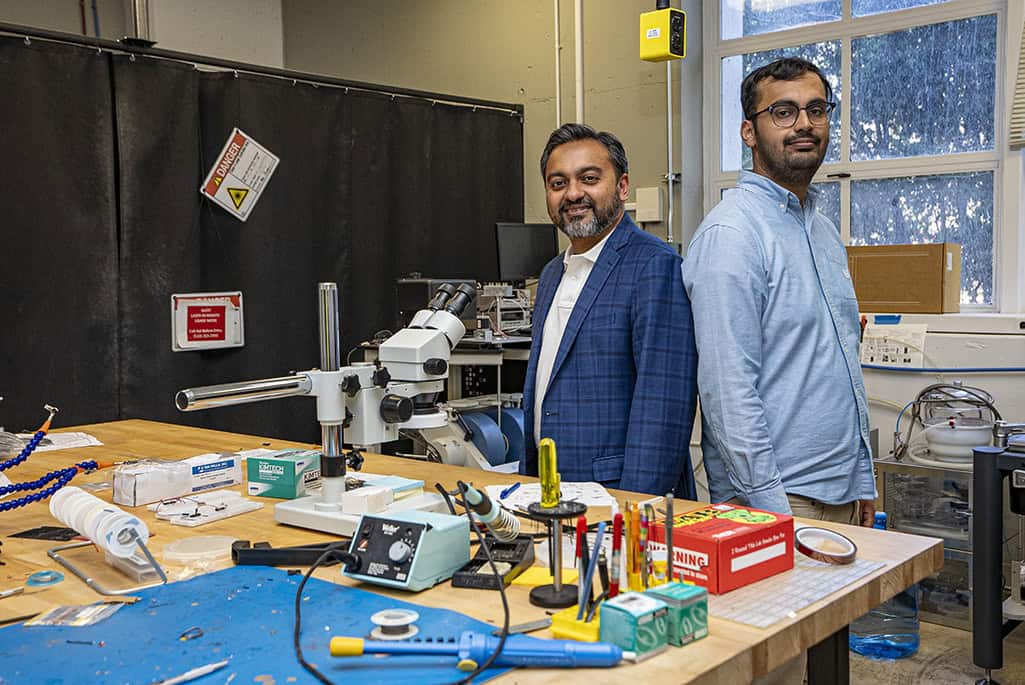

「エンジニアリングされた薄膜で作られたマイクロコンデンサに大量のエネルギーを蓄えることが可能であることを示しました。これは通常の誘電体では不可能なことです。さらに、この材料はマイクロプロセッサの上に直接加工することができるのです」と、プロジェクトを率いたBerkeley Labの上級科学者であり、UC Berkeleyの教授であるSayeef Salahuddin氏は述べている。

この研究は、Berkeley Labにおけるより小型で高速、かつエネルギー効率の高いマイクロエレクトロニクスのための新材料と技術の開発に向けた広範な取り組みの一部である。

コンデンサは電気回路の基本的なコンポーネントの一つであり、エネルギーを蓄えるためにも使用できる。バッテリーとは異なり、コンデンサは二つの金属板の間に配置された誘電体材料に確立された電場にエネルギーを蓄える。コンデンサは必要な時に非常に迅速に放電できるため、迅速に電力を供給することができ、繰り返しの充放電サイクルでも劣化しないため、バッテリーよりも長寿命だ。しかし、コンデンサは一般的にエネルギー密度がバッテリーよりもはるかに低いため、単位体積または重量あたりのエネルギー貯蔵量が少なくなり、この問題はオンチップエネルギー貯蔵のためにマイクロコンデンサに縮小しようとするとさらに悪化する。

ここで、研究者たちはHfO2-ZrO2の薄膜を慎重にエンジニアリングすることで、負の容量効果を達成し、記録的なマイクロコンデンサを実現した。通常、1つの誘電体材料を別の誘電体材料の上に積層すると、全体の容量は低下する。しかし、1つの層が負の容量材料である場合、全体の容量は実際に増加する。以前の研究では、Salahuddin氏とその同僚は、負の容量材料を用いて、従来のMOSFETトランジスタよりもはるかに低い電圧で動作するトランジスタを製造することを示した。ここでは、負の容量を利用して、より多くの電荷を蓄え、それゆえエネルギーを蓄えることができるコンデンサを製造した。

結晶薄膜は、HfO2とZrO2の混合物から原子層堆積により製造され、工業用チップ製造で使用されている標準的な材料と技術を用いている。2つの成分の比率に応じて、薄膜はフェロエレクトリック(結晶構造に内蔵された電気分極を持つ)またはアンチフェロエレクトリック(電場を適用することで分極状態に誘導される)となる。組成が適切に調整されると、キャパシタを充電することで生成される電場が、フェロエレクトリックとアンチフェロエレクトリックの秩序の間の転換点で薄膜を平衡させ、この不安定性が負のキャパシタンス効果を生み出し、材料が非常に小さな電場で分極されやすくなる。

「そのユニットセルは相転移中に分極したがっており、これが電場に応じて余分な電荷を生成するのを助けます。この現象は負の容量効果の一例ですが、通常よりもはるかに多くの電荷を捕捉する方法と考えることができます」と、Salahuddin氏のグループのポスドクであり、論文の主要著者の一人であるSuraj Cheema氏は述べている

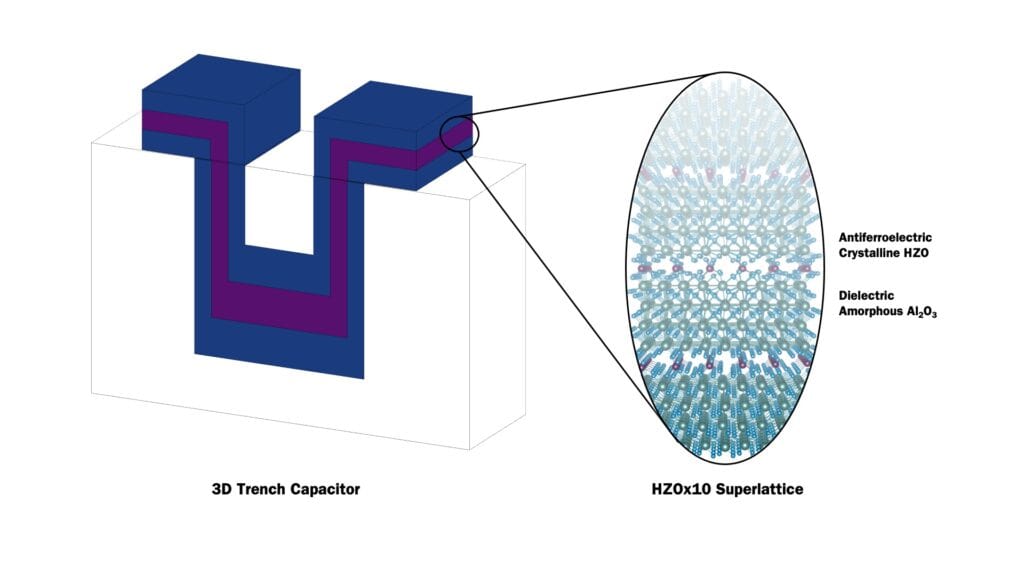

薄膜のエネルギー貯蔵能力をスケールアップするために、チームは薄膜の厚さを増やしつつ、アンチフェロエレクトリック-フェロエレクトリックのフラストレーション状態を維持する必要があった。HfO2-ZrO2の数層ごとに原子層のアルミナを挿入することで、望ましい特性を維持しながら薄膜を最大100 nmまで成長させることができた。

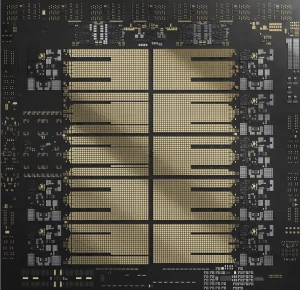

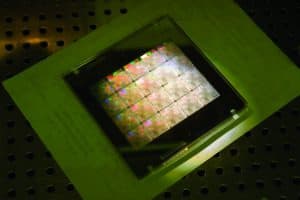

最後に、MIT Lincoln Laboratoryの協力者と共に、研究者たちは薄膜を3次元マイクロキャパシタ構造に統合し、アスペクト比が100:1に達するシリコンに切り出された深いトレンチ内に精密に積層された薄膜を成長させた。これらの3Dトレンチキャパシタ構造は、今日のDRAMキャパシタで使用されており、平面キャパシタに比べて単位フットプリントあたりのキャパシタンスをはるかに高くすることができ、より高い小型化と設計の柔軟性を実現している。得られたデバイスの特性は記録的であり、今日の最高の静電キャパシタと比較して、これらのマイクロキャパシタは9倍のエネルギー密度と170倍の電力密度(それぞれ80 mJ cm−2および300 kW-cm−2)を持っている。

「得られたエネルギー密度と電力密度は、我々の予想をはるかに上回っていました。負の容量材料を開発してきましたが、これらの結果には非常に驚かされました」と、Salahuddin氏は述べている。

これらの高性能マイクロコンデンサは、Internet-of-Thingsセンサー、エッジコンピューティングシステム、人工知能プロセッサなどのマイクロデバイスにおける効率的で小型化されたエネルギー貯蔵の需要を満たすのに役立つ可能性がある。研究者たちは現在、この技術をスケールアップし、フルサイズのマイクロチップに統合する作業を進めており、これらの薄膜の負のキャパシタンスをさらに改善するための基礎材料科学の進展を目指している。

「この技術を用いることで、非常に小さなサイズでオンチップエネルギー貯蔵と電力供給のシームレスな統合を実現することができます。これは、マイクロエレクトロニクスのための新しいエネルギー技術の領域を開く可能性があります」と、Cheema氏は述べている。

論文

参考文献

研究の要旨

誘電体静電キャパシタは、超高速充放電が可能であるため、高出力エネルギー貯蔵アプリケーションに適しています。超高速動作とともに、オンチップ集積化により、新たな自律型マイクロエレクトロニクスやマイクロシステム用の小型エネルギー貯蔵デバイスを実現することができる。さらに、最先端の小型電気化学エネルギー貯蔵システムであるマイクロスーパーキャパシタとマイクロバッテリーは、現在、安全性、パッケージング、材料、微細加工の課題に直面しており、オンチップ技術への対応を妨げている。ここでは、3つのアプローチにより、シリコンに集積されたHfO2–ZrO2ベースの薄膜マイクロキャパシタにおいて、我々の知る限り、記録的な高い静電エネルギー貯蔵密度(ESD)と電力密度を報告する。第一に、固有エネルギー貯蔵量を増加させるために、原子層堆積型の反強誘電体 HfO2–ZrO2 薄膜を電界駆動型強誘電体相転移近傍に設計し、負のキャパシタンス効果によって増幅された電荷貯蔵を示すことで、体積ESDを最もよく知られたバックエンド互換誘電体(115 J cm−3)を超えて向上させる。第二に、総エネルギー貯蔵量を増加させるために、反強誘電体超格子工学14は、HfO2–ZrO2ベースの(反)強誘電体15の従来の厚さの限界(100nm領域)を超えてエネルギー貯蔵性能を拡大する。第3に、フットプリントあたりの貯蔵量を増やすために、超格子を3次元キャパシタにコンフォーマル集積する。これにより、面内のESDは9倍に、面内の電力密度は最もよく知られた静電キャパシタの170倍に向上する:それぞれ80 mJ cm−2と300 kW cm−2である。この超高エネルギー密度と電力密度の同時実証は、静電-電気化学エネルギー貯蔵階層における従来の容量-速度トレードオフを克服するものである。さらに、超高密度・超高速充電薄膜をバックエンド・オブ・ライン互換プロセスで統合することにより、オンチップ・マイクロキャパシタ5をモノリシックに集積することが可能になり、電子マイクロシステムの実質的なエネルギー貯蔵と電力供給性能を引き出すことができる。

コメント