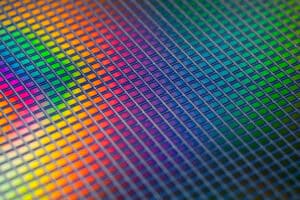

シリコンウェハーと言えば、円形で虹色に輝くディスクのようなイメージが一般的だが、マルチチップレットプロセッサが増えていき、ますます多くのトランジスタを収容することでプロセッサの肥大化が進むことに対応する為、TSMCでは長方形のパネル状基板を利用した先端パッケージング技術の開発が進められているとのことだ。

AIアクセラレータのサイズ肥大化が大きな方針転換を迫る

Nikkei Asiaは、6人の関係者の話を引用し、初期状態のこの研究について報じている。TSMCが取り組んでいる長方形基板は510mm×515mmの物となり、従来の直径300mmの円形ウェハーと比較して、約3.7倍の使用可能面積が得られるという。特に、円形ウェハーでは無駄になっていた端の部分が利用できることは大きい。

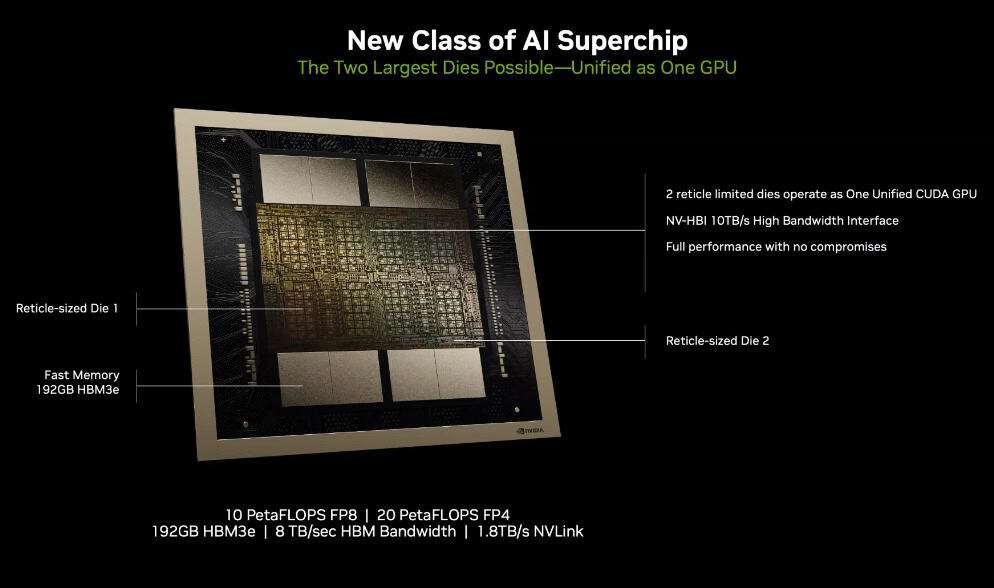

こうした移行は、特にAI向けGPU需要の増大によるところが大きいようだ。NVIDIAのH200やB200のようなAIアクセラレータでは、最先端プロセスこそ用いられていないが、先端パッケージング技術が重要になって来ている。特にこれらNVIDIAチップでは、TSMCのCoWoS(Chip on Wafer on Subsrate)と呼ばれる先端チップパッケージング技術が用いられている。例えばNVIDIAの次世代Blackwellアーキテクチャに基づく「B200」では、CoWoSにより2つのGPUダイと8つの高帯域幅メモリ(HBM)が接続され、一つのパッケージに収められている。これにより、高速データスループットと高度な演算性能を実現している。

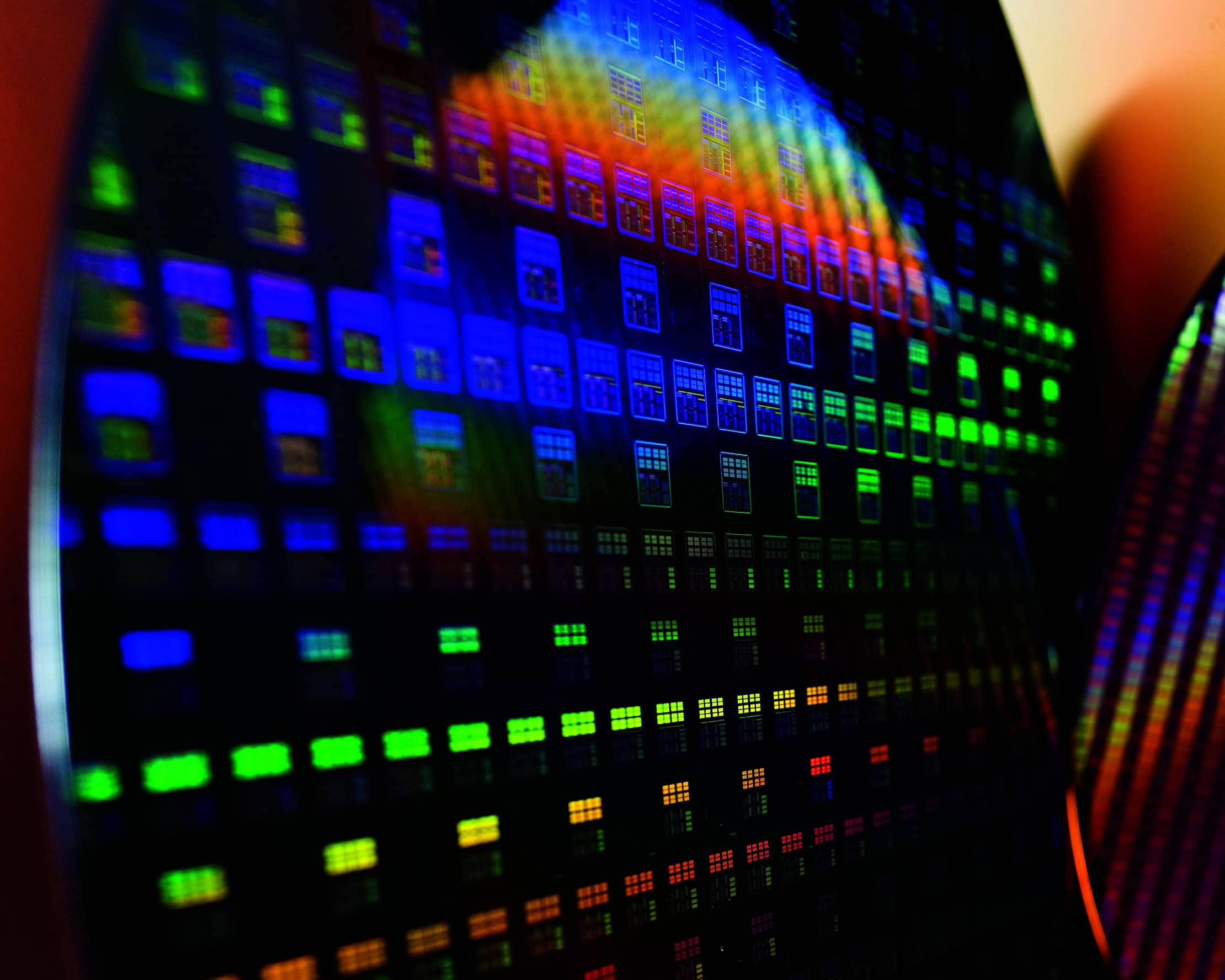

ただし、そうなると問題になるのがチップの肥大化だ。業界関係者によると、B200の場合、現在一般的な12インチウェハー(面積約70,685平方ミリメートル)1枚に構築できるのはわずか16セットだという。しかもこれは歩留まりが100%と仮定した場合と言う事で、実際にはこれよりも少ない収量となるだろう。Morgan Stanleyの推定によると、以前のH200とH100チップは1枚のウェハーに約29セットが取れたという。

ある半導体メーカーの幹部はNikkei Asiaに次のように語っている:「トレンドは確実です。AIデータセンター計算に使用されるチップからより多くの計算能力を引き出すにつれて、パッケージのサイズはますます大きくなるでしょう。しかし、これはまだ初期段階です。例えば、新しい形状の基板上での先端チップパッケージングにおけるフォトレジストの塗布は、ボトルネックの1つです。装置メーカーに装置設計を変更させるには、TSMCのような半導体メーカーの豊富な資金力が必要です」。

ただし、円形から長方形への移行は想像以上に困難を極めると見られ、計画の実現には5年から10年を要すると見られている。「この転換には、ロボットアームや自動材料処理システムのアップグレードなど、異なる形状の基板を処理するための設備の大幅な改修が必要になるでしょう」と、Bernstein Researchの半導体アナリスト、Mark Li氏は述べている。同氏によれば、AI向けチップがパッケージあたりますます多くのチップを必要とするため、今後TSMCは長方形基板を検討する必要が出てくるだろうとのことだ。

なお、Nikkei Asiaによると、IntelやSamsungを含む他のファウンドリーも、パネルレベル・パッケージングを模索している。 Powertech Technologyなどの企業や、BOE Technologyや台湾のInnolux などのディスプレイ・パネル・メーカーは、半導体産業への多角化のためにこの技術に投資していると言われている。

Sources

コメント