半導体業界で新たな革新的技術として注目を集めているガラス基板。台湾の半導体大手TSMCが、AIチップ市場で圧倒的シェアを誇るNVIDIAの要求に応じて、ガラス基板技術の開発を加速させていることが明らかになった。業界筋によると、この新技術を採用した初のチップが2025年から2026年にかけて登場する可能性があるという。

TSMCとNVIDIA、ガラス基板技術で新たな挑戦

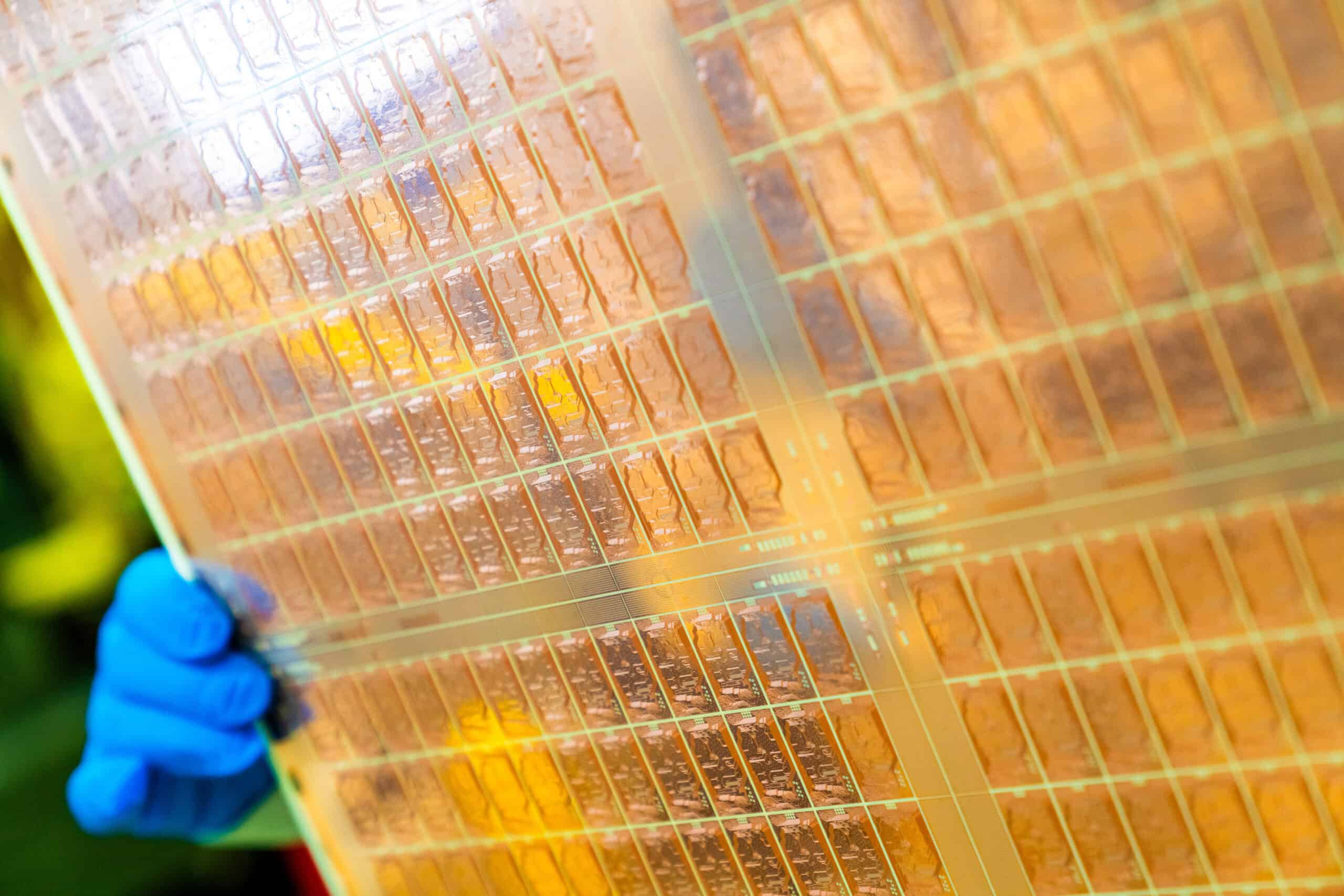

ガラス基板技術は、従来のパッケージング技術に代わる次世代の解決策として期待されている。この技術は、単一パッケージにより多くのトランジスタを集積することを可能にし、チップの性能と効率を大幅に向上させる潜在力を秘めている。

TSMCの魏哲家CEOは最近、同社がFOPLP(Fan-Out Panel Level Package)技術の開発を継続していることを明らかにした。さらに、業界関係者によると、TSMCはNVIDIAからの強い要請を受け、以前は一時中断していたガラス基板技術の研究開発を再開したという。

NVIDIAのAIチップ需要の急増に伴い、TSMCは高コストのCoWoS(Chip-on-Wafer-on-Substrate)技術の生産能力を大幅に拡大せざるを得なくなっている。しかし、それでも顧客の需要を完全に満たすには至っていない。このような背景から、ガラス基板技術は次世代のパッケージング・ソリューションとして、両社の注目を集めているのだ。

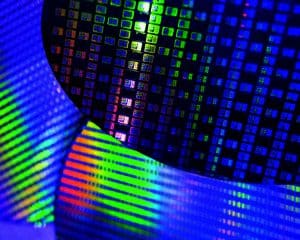

半導体業界におけるガラス基板技術の競争は、すでに熾烈を極めている。TSMCと並んで、Intel、Samsung Electronics、Huaweiなどの大手企業も、この技術の研究開発に多額の投資を行っている。特にIntelは、10年以上前からガラス基板技術の開発に取り組んでおり、現時点では量産能力を持つ唯一の企業だとされている。

ガラス基板技術の主な利点には、より高密度の配線能力、優れた信号性能、高い平坦度、高温・高電圧耐性などがある。これらの特性により、従来の有機銅箔基板に比べて、性能と信頼性の向上が期待できる。しかし、技術的な課題も存在する。特に、TGV(Through-Glass Via)と呼ばれる工程の速度が量産要件を満たしていないことが、技術の普及を妨げている要因の一つだ。

業界関係者によると、TSMCは今年9月初旬に開催される半導体展示会で、FOPLP技術の詳細を公開する予定だという。この発表で、ガラス基板のサイズ規格が統一される可能性があり、もしTSMCが515x510mmのサイズを採用した場合、他のOSAT(Outsourced Semiconductor Assembly and Test)企業のFOPLP技術における競争力が大きく低下する可能性がある。

ガラス基板技術の発展は、半導体業界全体に大きな影響を与えることが予想される。台湾の半導体設備メーカーは、この新たな市場機会を逃すまいと、すでに準備を進めているようだ。E&R Engineeringを中心に、「Glass Core」の核心製造プロセスを推進する「E-core System大連盟」が結成され、設備と材料の包括的なソリューションを提供する体制が整いつつある。

TSMCとNVIDIAの協力関係が、ガラス基板技術の実用化を加速させることは間違いない。2025年から2026年にかけて、この革新的な技術を採用した初のチップが市場に登場する可能性が高まっている。半導体業界は今、次世代のパッケージング技術をめぐる新たな競争の時代に突入しつつあると言えるだろう。

Sources

コメント