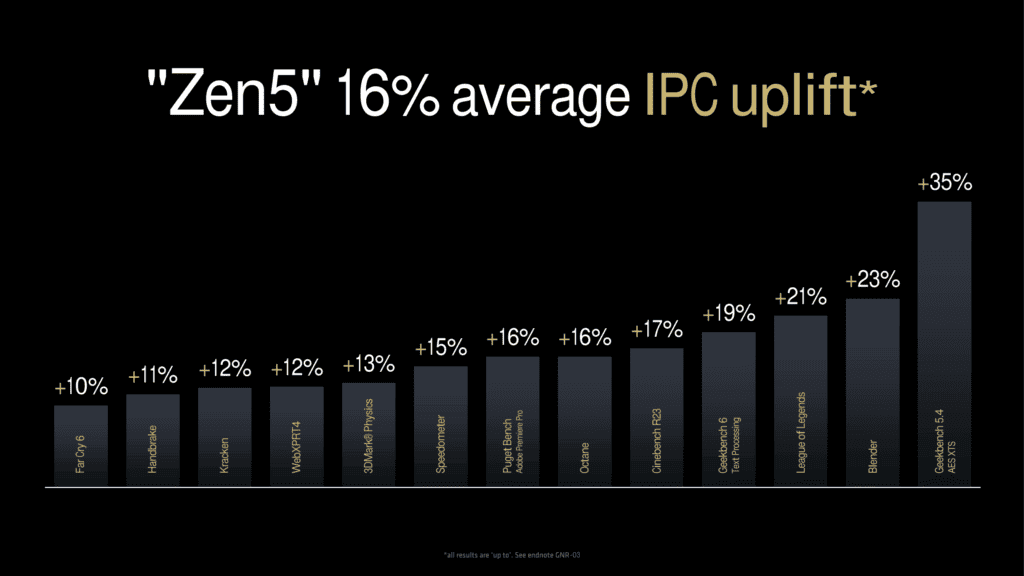

AMDは、Tech Dayイベントにおいて、次世代CPUマイクロアーキテクチャ「Zen 5」の技術的な詳細の一部を公開した。Computex 2024でのAMD CEO Lisa Su博士の基調講演で発表されたZen 5は、前世代のZen 4から平均16%のIPC(Instructions Per Clock)向上を実現し、デスクトップ向け「Ryzen 9000」シリーズとノートPC向け「Ryzen AI 300」シリーズに採用されるが、AMDはこれらのZen 5製品が7月31日から発売になることも合わせて正式に発表している。

Zen 5アーキテクチャの革新的な改良点と性能向上

AMDのZenコアアーキテクチャは、2017年にBulldozer比で52%のIPC向上でデビューし、以来、すべての世代で2桁のIPC向上を実現してきた。 Zen 5では、13のワークロードで測定したところ、IPCが平均16%向上しているとのことだ。

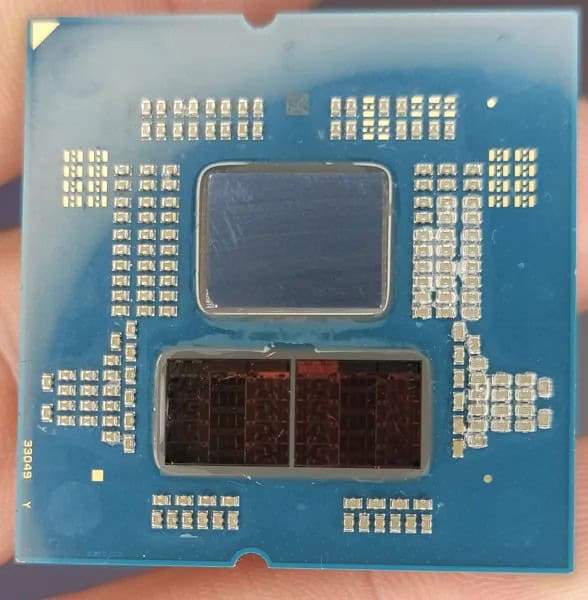

Zen 4プロセッサーと同様に、コアコンピュート・ダイ(CCD)は最大8コアで、中央に32MBの大容量共有L3コンプレックスを備えている。 2つのCCDは、Zen 4プロセッサーと同じ6nmのI/Oダイ(IOD)に接続されているため、このチップは同じグラフィックス・サポートと基本的な接続オプションを提供する。

ノートPC向け「Ryzen AI 300」プロセッサにZen 5コアと組み合わせられる省電力コア「Zen 5c」コアは、「標準的な」Zen 5パフォーマンス・コアよりもダイ上の消費スペースが小さい一方で、それほど負荷の高くないタスクには十分な性能を発揮するように設計されており、その結果、消費電力が節約され、従来よりも1平方ミリメートル当たりの演算能力が向上している。

IntelのEコアも同様のアプローチを取っているが、AMDのZen 5cは、標準的なZen 5コアと同じマイクロアーキテクチャを採用し、小型のコアで同じ機能をサポートしている。 これに対し、Intelの設計では、コアの種類ごとに異なるアーキテクチャと機能サポートを採用している。 より小さなZen 5cコアは、標準的なコアよりも低いクロックレートで動作し、ピーク性能は劣るが、より大きなGPUやNPUのような他の要素のためにダイ面積を確保することが出来る様になっている。

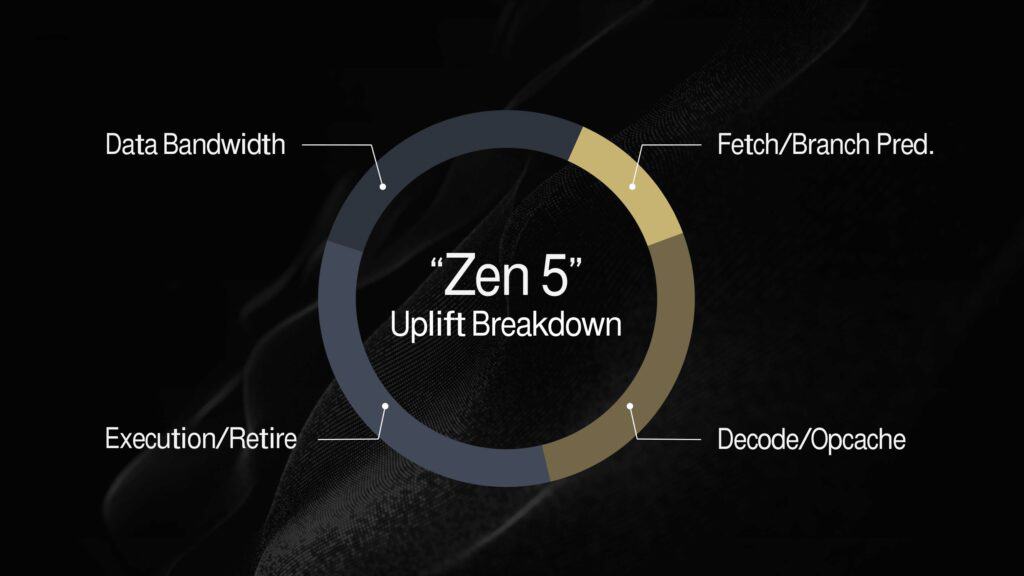

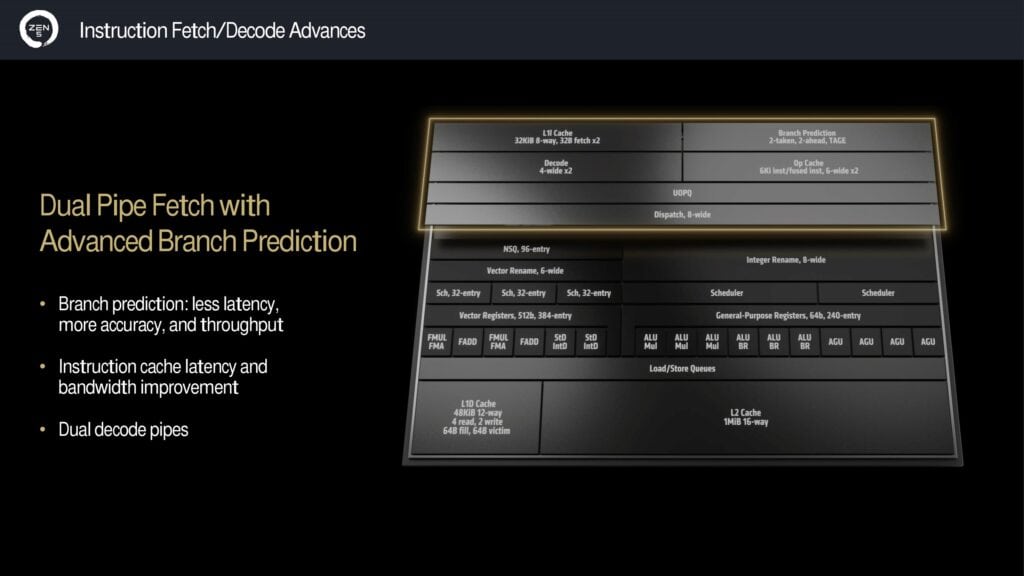

Zen 5アーキテクチャの最大の特徴は、フロントエンドからバックエンドまで、CPUコア全体にわたる包括的な改良にある。AMDのCTOであるMark Papermaster氏によると、フロントエンドの強化がIPC向上の約39%を占めているとのことだ。具体的には、デュアルパイプフェッチと高度な分岐予測機能を導入し、サイクルあたりの分岐予測数を増やしている。

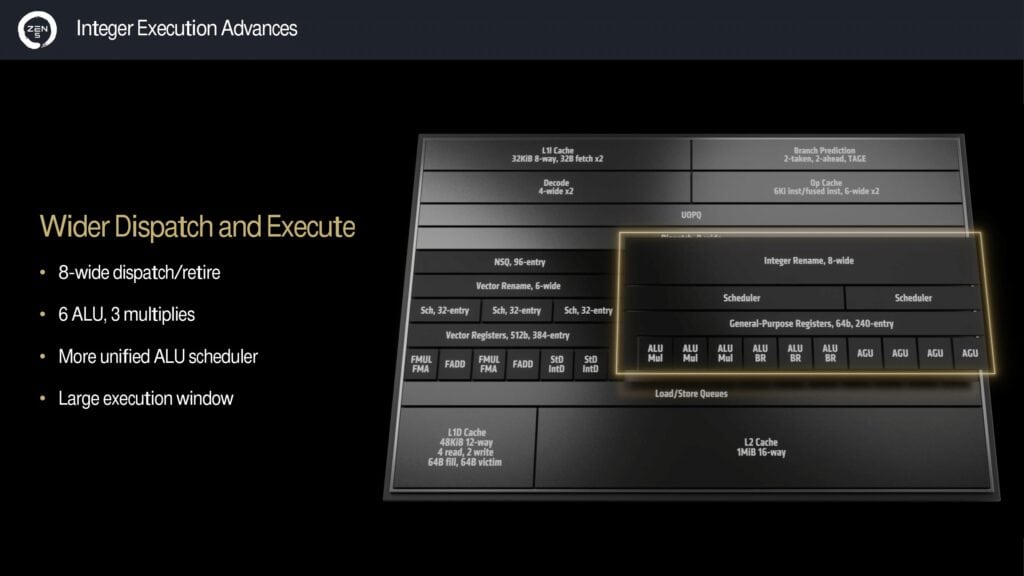

さらに、デュアルポート化された命令キャッシュ(i-cache)と操作キャッシュ(op-cache)により、レイテンシの削減と帯域幅の向上を実現している。これらの改良により、デュアル4ワイドデコードパスを通じてマイクロ操作キューに供給され、最終的に8ワイドのディスパッチを実現している。

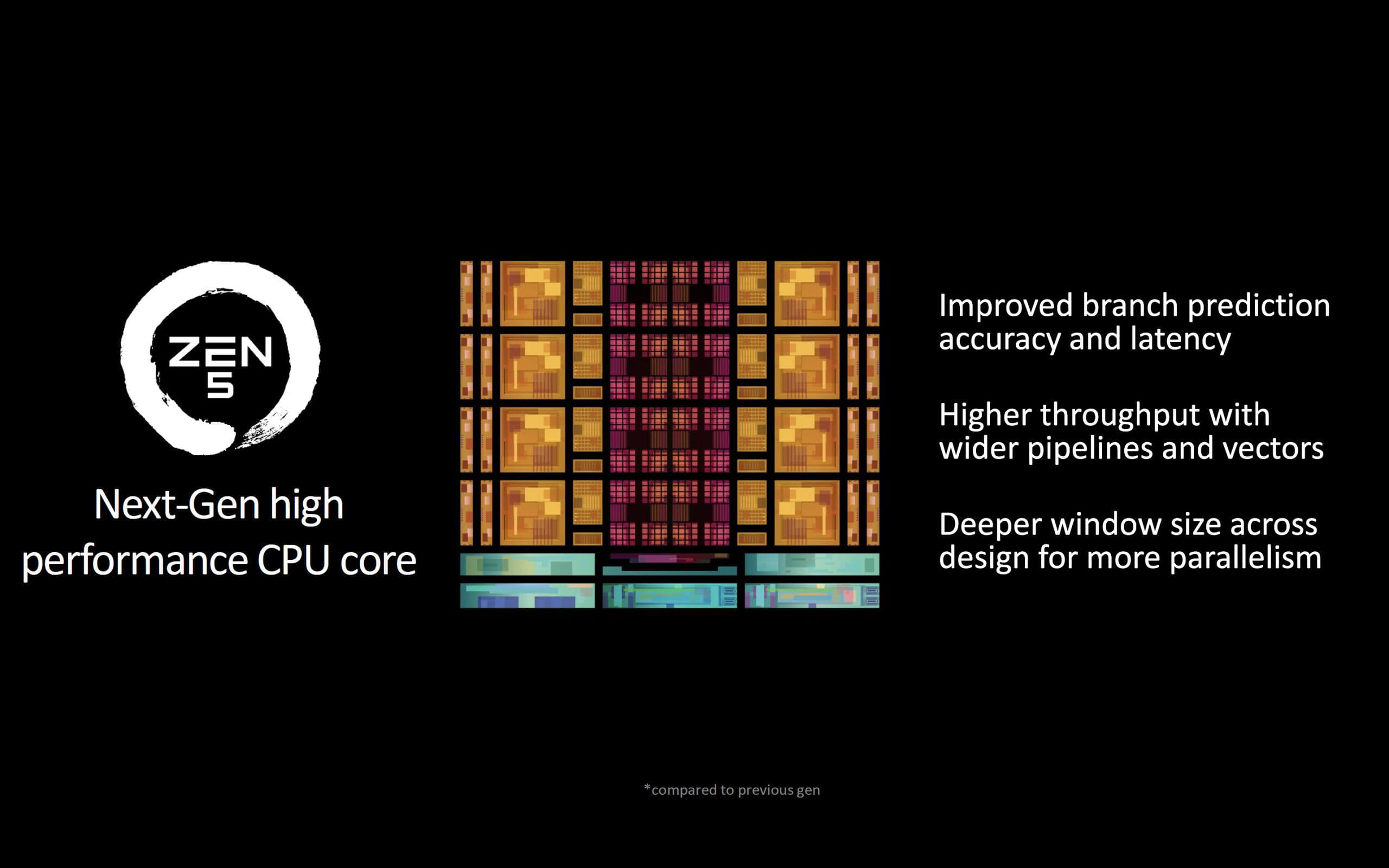

実行エンジンも大幅に強化された。Zenアーキテクチャでは長らくサイクルあたり6命令の実行と4つの算術論理ユニット(ALU)をサポートしてきたが、Zen 5ではサイクルあたり8命令のディスパッチとリタイアをサポートするよう拡張された。ALUも6つに増加し、統合ALUスケジューラの導入により実行効率が向上している。また、実行ウィンドウも40%拡大され、最大448の未処理操作をサポートできるようになった。これにより、より広いディスパッチと実行に伴う追加のミスを適切に処理できるようになっている。

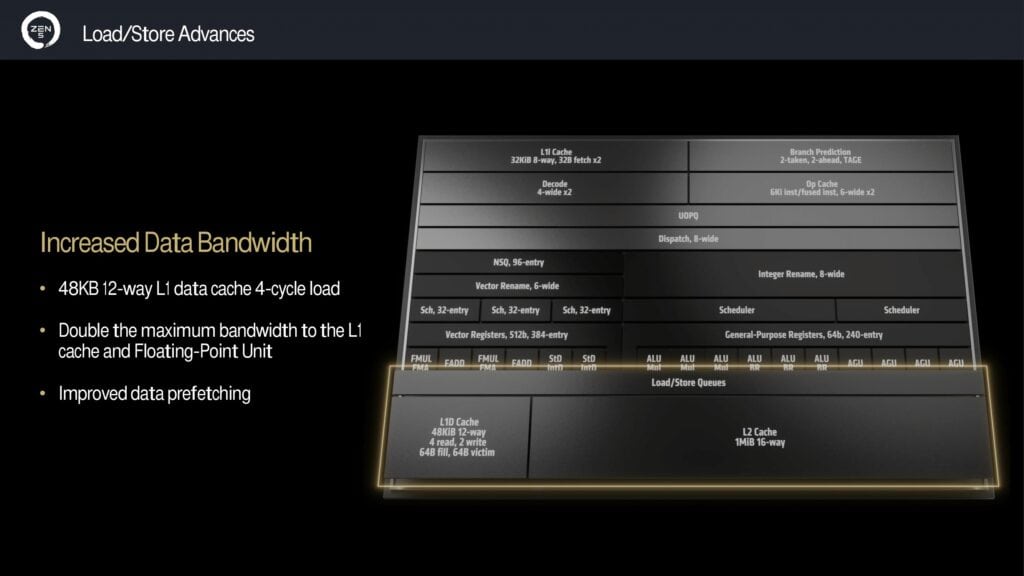

バックエンドでのデータ帯域幅の増加も、IPC向上の27%を占める重要な要因となっている。L1データキャッシュが32KBから48KBの12ウェイセットアソシアティブキャッシュに拡大された。さらに重要なのは、この容量増加にもかかわらず、4サイクルのロードレイテンシを維持していることだ。L1キャッシュと浮動小数点ユニットへの最大帯域幅が2倍になり、拡張されたAVXエンジンに対応している。

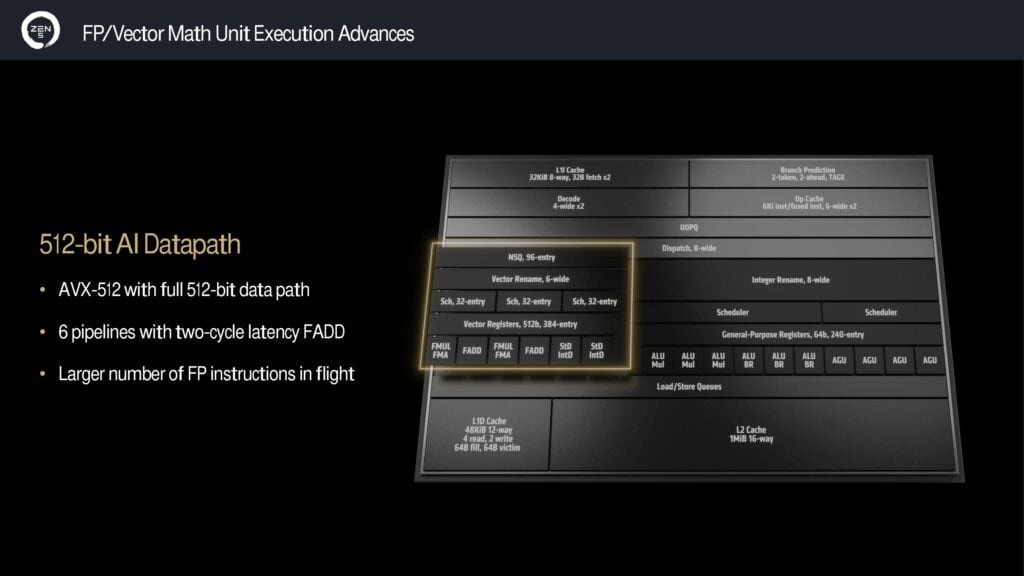

特筆すべきは、AVX-512ベクトル拡張の実装方法の変更だ。Zen 4では256ビットのデータパスを「ダブルポンプ」方式で使用していたが、Zen 5ではフル512ビットのデータパスを採用した。これにより、AVX-512とVNNIのスループットが2倍になり、AMDによれば、マルチコアワークロード時に周波数低下なしでAVX-512ワークロードを実行できるようになった。これはIntelのAVX実装とは対照的で、Intelの場合は深刻な周波数低下を引き起こすことがある。また、浮動小数点加算(FADD)のレイテンシを3サイクルから2サイクルに削減し、性能を向上させている。

ただし、ノートPC向けのStrix PointチップではTDPの制約から、引き続き「ダブルポンプ」方式のAVX-512を採用している。AMDのベクトル数学ユニットはモジュール式で、APU設計向けに256ビットの「ダブルポンプ」オプションも引き続きサポートしている。

製造プロセスに関しては、Zen 5コアがTSMCの4nmプロセスで、より電力効率の高いZen 5cコアがTSMCの3nmプロセスで製造される。これらの新コアは、デスクトップ向けRyzen 9000シリーズだけでなく、ノートPC向けのRyzen AI 300シリーズにも採用される。

Ryzen 9000シリーズは、最大で16コアと64MBのL3キャッシュを搭載し、従来のAM5プラットフォームを使用する。一部の噂ではRyzen 7 9700XのTDPが120Wになるのではないかと言われていたが、今回正式に65Wであることが発表され、この噂は明確に否定された。

一方、Ryzen AI 300シリーズ(コードネーム:Strix Point)は、4つのZen 5コアと8つのZen 5cコアを組み合わせ、50 TOPSのAI性能を持つXDNA 2 NPUを統合している。さらに、RDNA 3.5統合グラフィックスを搭載し、前世代のRDNA 3モバイルグラフィックスよりも優れたゲーム性能を提供する。

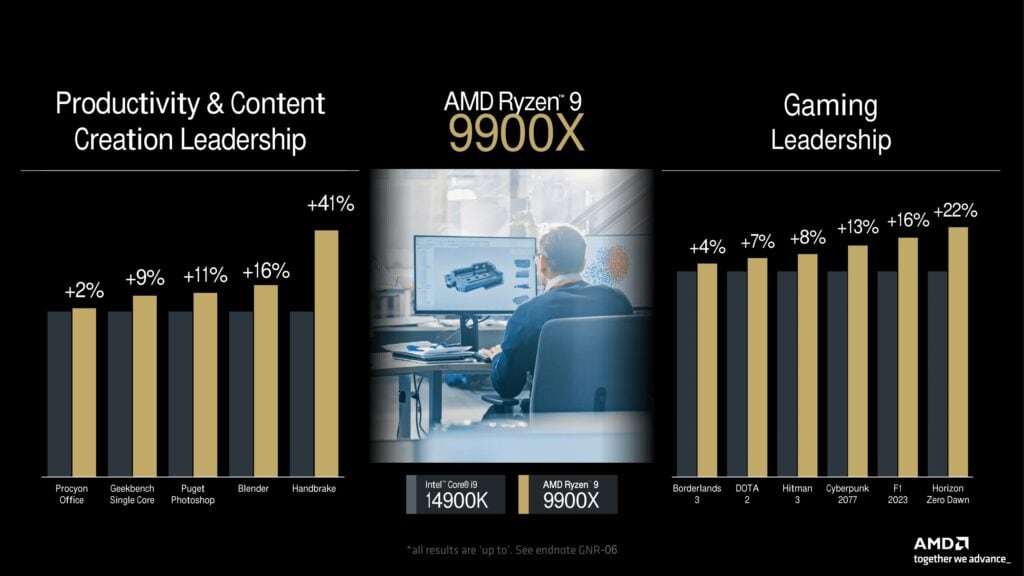

AMDはZen 5の性能向上を様々なベンチマークで示している。ゲームではIntelのCore i9 14900Kと比較して、AMDのRyzen 9 9900Xは『Cyberpunk 2077』は13%、『Horizon Zero Dawn』は22%の向上を達成。

また、Webブラウジング性能を示すSpeedometerでは15%の向上が見られた。特筆すべきは、Geekbench 5.4のAES-XTSテストでの35%という大幅な向上だ。これは、新しいAVX-512実装の効果を如実に示している。また、機械学習においては、シングルコア性能でZen 4比32%の向上を達成している。

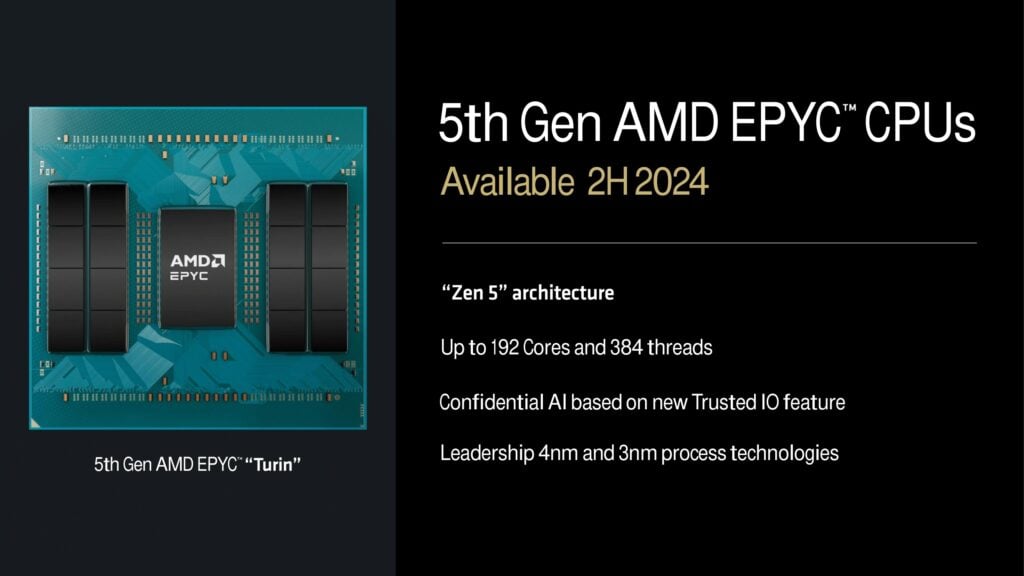

AMDは、Zen 5アーキテクチャが今後数世代にわたるマイクロアーキテクチャの基盤となると述べている。Zen 5の主任アーキテクトであるMike Clark氏は、これが次の数世代のマイクロアーキテクチャの基礎となると述べている。7月31日に最初のZen 5コアが市場に登場する予定だが、データセンター向け製品の登場にはもう少し時間がかかるようだ。データセンター向けの第5世代EPYC CPUは、コードネーム「Turin」として2024年後半に登場予定で、最大192のZen 5コアを搭載するという。

コメント