Ampere Computingはおよそ1年前、自社設計のArmサーバ・プロセッサ「AmpereOne」を発表したが、このプロセッサは搭載コア数が最大192コアという驚くべき物で、同社は当時業界最高のコア数を誇るこのプロセッサでクラウド市場を席巻した。

発表当時、CEOのRenee James氏は、「数十年ごとに、性能に求められる新たな基準を設定するような、性能を牽引するアプリケーションや用途が出現しています。現在の駆動用途は、AIとコネクテッド・エブリシング、そしてストリーミング・メディアの継続的な使用と欲求です。データセンターでは、電力をパフォーマンスの代用品として使い続けることはできません。Ampereでは、持続可能な電力でパフォーマンスを最大化するように製品を設計しているので、業界の未来を牽引し続けることができます」と、述べていたが、ここで気になるのが今後の製品計画だ。Ampereの最高製品責任者であるJeff Wittich氏はThe Next Platformの取材に応じ、将来世代の具体的ないくつかの詳細を共有している。

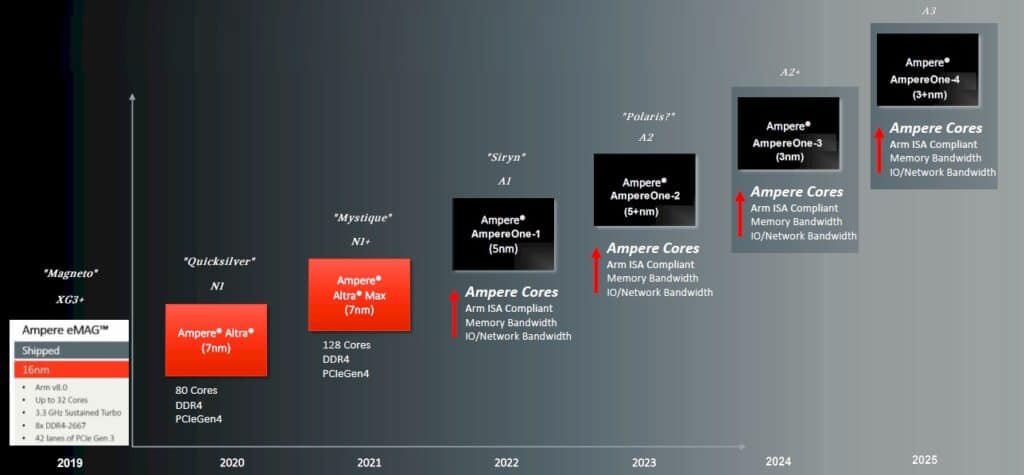

Wittich氏によれば、Ampereは第2世代のAmpereOneプロセッサを2024年後半にリリースする予定とのことだ。明らかになっているロードマップによると、AmpereOneの第2世代は5nm移行のプロセスで製造される予定のようだが、その具体的な製造プロセスは不明である。

AmpereOne-2は、12個のDDR5メモリコントローラを搭載し、メモリ帯域幅を50%向上させる事で性能向上を図るという。

だが、驚くべきはその次の世代となるAmpereOneプロセッサの第3世代だ。Wittich氏によれば、256ものコアを搭載し、TSMCの3nmプロセスで製造されるという。コアは2つのチップレット構成が計画されており、1チップレットあたり128コア、もしくは64コアの4チップレット構成になる計画もあるようだ。

我々は、コンピュート・サイドでかなり速く動いている。この設計には、その他多くのクラウド機能、つまりすべてのコアを最大限に活用するためのパフォーマンス管理に関するものが含まれています。各チップのリリースでは、一般的にCPUコアの世代交代とみなされるような変更を行う予定です。

また、この256コア設計ではチップレット・アプローチを採用しており、これも別のステップです。チップレットは、我々の全体的な戦略のかなり大きな部分を占めています。

AmpereOne-3はPCIe-Express 6.0と12個のDDR5メモリコントローラが搭載され、NVIDIAなどの競合他社と互角以上に競争する計画のようだ。

「我々は、コンピュート・サイドではかなり速く動いています。この設計には、すべてのコアを最大限に活用するためのパフォーマンス管理など、その他多くのクラウド機能が搭載されています。各チップのリリースにおいて、我々は一般的にCPUコアの世代交代とみなされるような変更を行うつもりです。すべての世代で多くのものを追加しています。そのため、より高い性能、より高い効率性、セキュリティ強化のようなより多くの機能を目にすることになりますが、これらはすべてマイクロアーキテクチャー・レベルで起こります。これらはすべてマイクロアーキテクチャレベルで実現されるものですが、私たちは、すべてのアンプレオンにわたって優れた性能の一貫性を確保するために多くのことを行ってきました。また、この256コア設計ではチップレット・アプローチを採用しており、これも新たな一歩です。チップレットは我々の全体的な戦略のかなり大きな部分を占めています」と、Wittch氏は述べている。

Ampereの取り組みにより、AI分野でのNVIDIA独占が少しでも崩れることで市場がより良い方向に進化していくことが望まれるところだ。

Source

- The Next Platform: AMPERE READIES 256-CORE CPU BEAST, AWAITS THE AI INFERENCE WAVE

コメント