本日、Armは、ハイパフォーマンスコアの「Cortex-X4」を発表した事と併せて、最新世代のビッグコアである「Cortex-A720」と、高効率な小型コアの最新世代「Cortex-A520」を発表した。

Cortex-A720

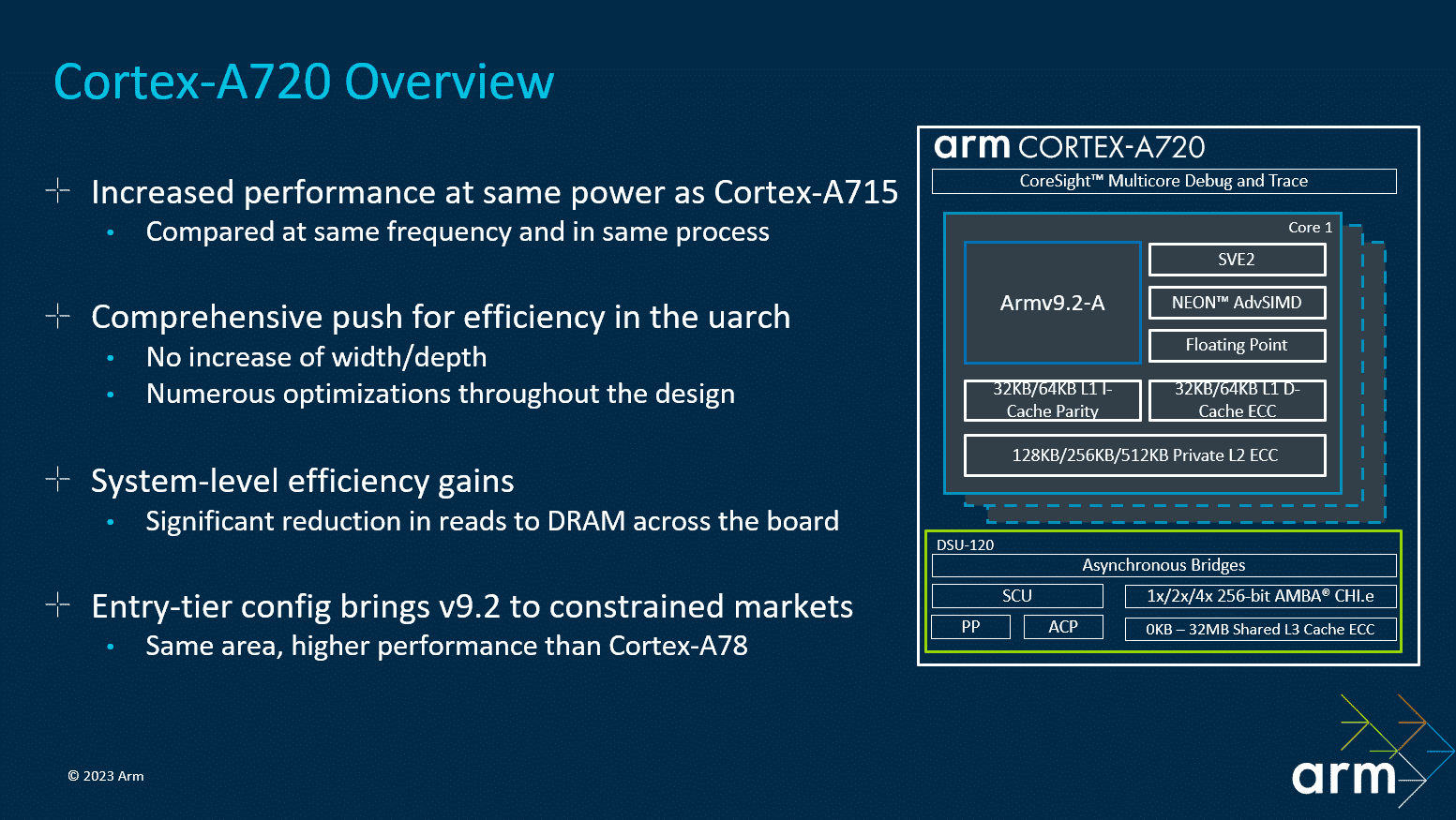

コードネームHunterと呼ばれるCortex-A720は、性能とエネルギー効率を向上させた新しいビッグコアを毎年発表しているArmの伝統を引き継いでいる。

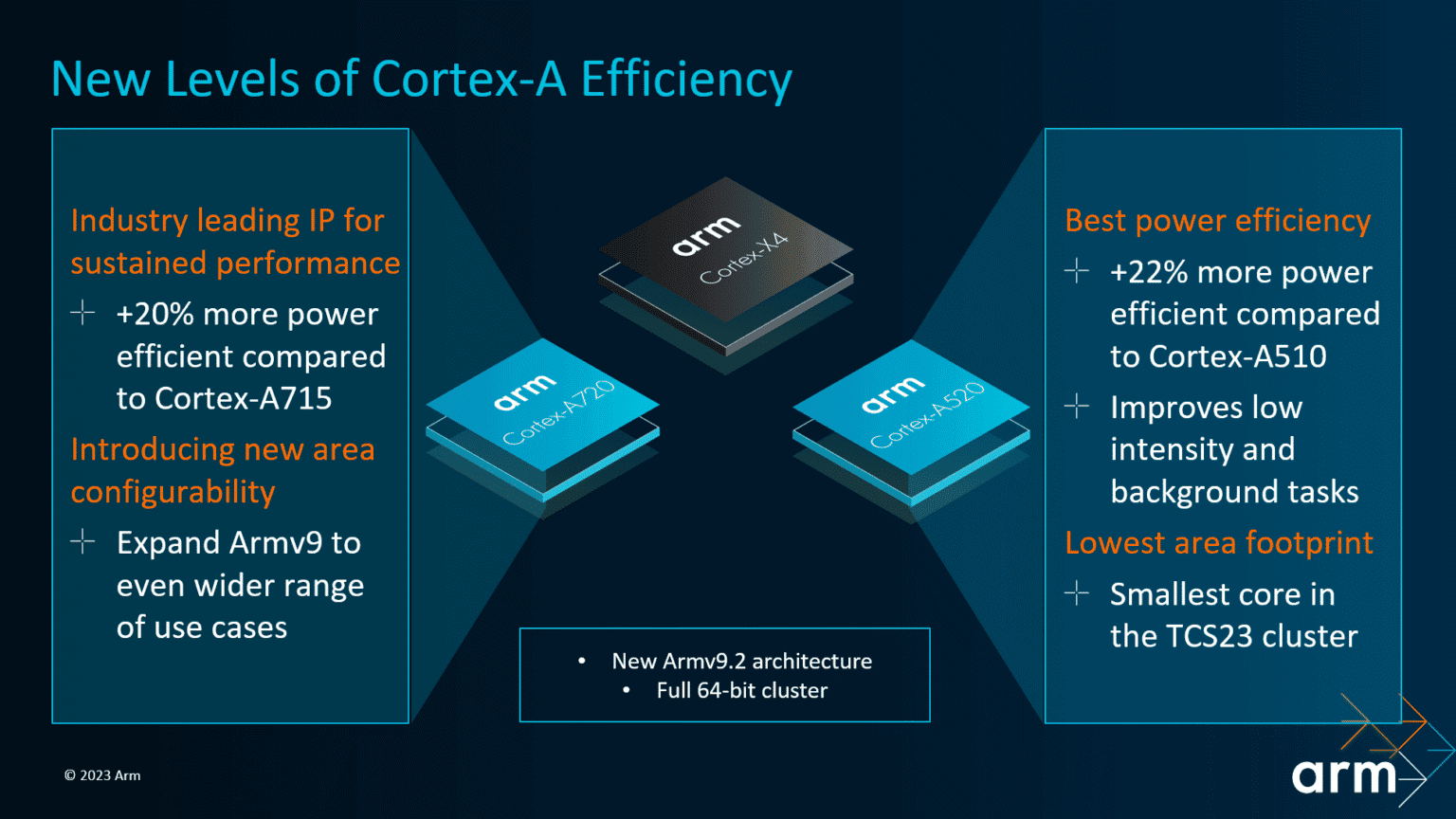

Cortex-A720は、同社の最も汎用性の高いパフォーマンスコアで、一般的なDSU構成ではビッグコアとして機能し、Cortex-A500シリーズのリトルコアと組み合わされることが多い。Armは、A715と比較して、新しいコアは電力効率を20%も向上させることができると述べている。

Armの1年ごとの更新では、デコード、パイプラインの幅と長さのような大規模なパイプラインの改善に焦点を当てる年、エネルギー効率と面積の改善に焦点を当てる年が交互に現れている。Cortex-A720は、Armv9.2 ISAをサポートし、32/64KiBのL1と128-512KiBのプライベートL2を備えている。前世代のCortex-A715では、Armが32ビットアーチのサポートを終了したため、デコードの大型化など様々な大型パイプラインの変更が行われたが、新しいCortex-A720では、深さや幅の面で大きな変更はなく、主に電力効率に焦点を当てた。

フロントエンド

Armは、A720のフロントエンドにさまざまな機能強化を施した。まず1つ目は、ミスプリディクトペナルティの削減だ。Armは、Cortex-A715の12サイクルから丸々1サイクルを削減したと述べており、これは実世界のアプリケーションに大きな利益をもたらすと言われている。2つ目の改良は、予測に関するものだ。Armは、過去数世代にわたって、Cortex-A7xxシリーズの分岐予測の改善にかなりの時間を費やしてきた。Cortex-A710では、大型コアは1サイクルあたり2つの無条件分岐を予測することができた。前世代では、それをさらに強化して、条件分岐も完全にサポートするようにした。今回、Cortex-A720では、Armは2回分の分岐予測をさらに改善した。Armによれば、効率を高めると同時に、性能に影響を与えずに電力を大幅に削減するために、構造的な最適化が行われた。

バックエンド

Cortex-A720のバックエンドでは、ArmによるとFDIV/FSQRTユニットをパイプラインに接続した。最終的には、大幅な性能向上を実現しながらも、面積に大きな影響を与えないようにしている。FP/Vectorユニットと整数ユニット間のデータ転送も最適化され、レイテンシが減少している。ベクターと汎用レジスタファイル間の転送速度も同様に最適化されている。また、Cortex-A720では、より早い提供開始により、ストアデータレイテンシが改善されている。

メモリ

メモリサイズについては、Cortex-A720はL2キャッシュのヒットレイテンシをCortex-A715の10サイクルから9サイクルに短縮した。プリフェッチャは、Armにとって継続的な改良の道である。Cortex-A720では、新しいL2空間プリフェッチエンジンが追加されたという。全体として、Armは既存のプリフェッチャに対して世代を超えた精度/カバレッジの改善を行なったと述べている。

新しいCortex-A720に搭載された興味深い変更点として、デュアルコンフィギュレーションがあります。Cortex-A720は、エリア最適化構成とフル構成がある。エリア最適化構成では、Cortex-A720はCortex-A78と比較して面積コストがかからず、10%の向上を実現している。フル構成では、Cortex-A720はCortex-A715と比較してエネルギー効率が最大で20%向上するが、面積コストは高くなる。

Cortex-A520

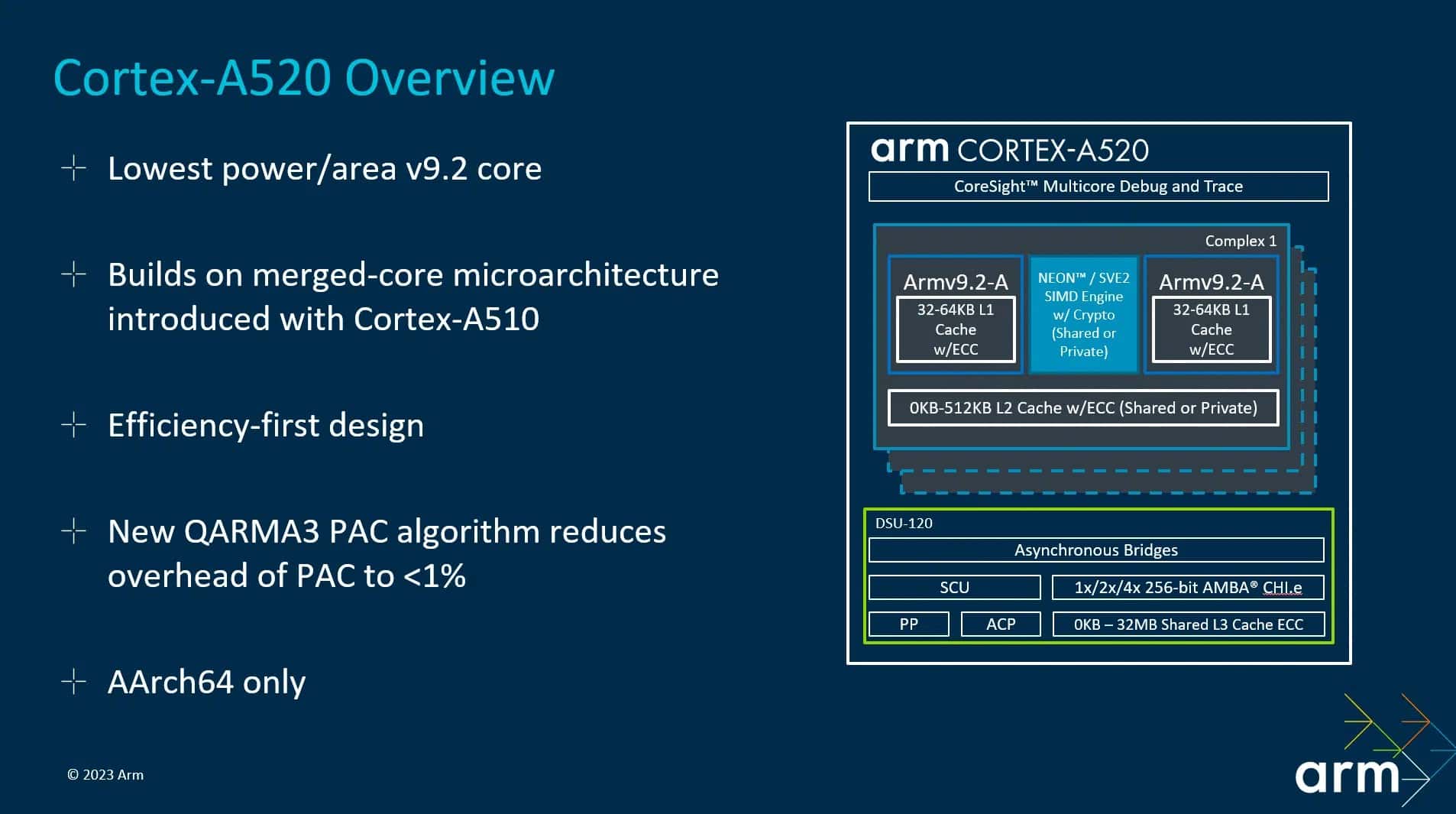

Armの、Cortex-A520は、2年前に新アーキテクチャとしてデビューし、昨年マイナーチェンジされたCortex-A510の後継となるものだ。

開発中は「Hayes」というコードネームで呼ばれていたCortex-A520は、一連のマイクロアーキテクチャの改善と最適化により、顕著な電力効率の向上を実現することが期待されている。

以前の小さなコアと同様に、Cortex-A520は、新しいDSU-120を使用して新しいCortex-A720とさまざまな構成で結合されることを目的としている。新しいA520の主な設計上の焦点は、コスト制約のあるデバイスのために、最小面積で最高のエネルギー効率レベルを実現することだ。

Cortex-A520は、A510マージドコア設計をベースとしている。A510はArmv9を完全にサポートしていたが、新しいA520の基礎となるISAサポートレベルはバージョン9.2に更新された。それに伴い、新しいコアはPAC(v8.8/v9.3に含まれる)機能の拡張をサポートしている。Armによると、アドレス認証のためにPEに実装された新しいQARMA3アルゴリズムは、PACのオーバーヘッドを1%未満に低減し、レイテンシもわずかに低減している。

Armは、Cortex-A520にさまざまな変更を加えたが、そのすべてがエネルギーと面積の効率を高めることに重点を置いている。性能向上の大部分は、分岐予測の改善とデータプリフェッチで行われ、コアパイプラインの変更に比べ、より低い電力コストでより優れた性能効率を実現する。

Cortex-A510に搭載されていたいくつかの性能は、他の領域でよりよく電力を活用するために、この反復では実際に削除されたり縮小されたりした。その最大の例は、ALUの削除だろう。以前のCortex-A510は、3つのALUを搭載していました。新しいCortex-A520では、ArmはALUを丸ごと1つ削除した。Armによれば、これにより、イシューロジックからリワード、フォワーディングに至るパイプライン全体で電力を節約する効果があったという。また、A510ではメモリシステムも再構築され、さらなる効率化が図られている。

全体として、Armは、新しいA520が同等の性能レベルで22%の電力削減を可能にする、あるいは、同等の電力レベルで約8%の性能向上を可能にすると述べている。

Sources

コメント