半導体製造技術の最前線を走るIntelが、IEDM(IEEE International Electron Devices Meeting)2024において、原子レベルの薄さを実現した2Dトランジスタ技術から革新的なチップ間接続技術まで、複数の画期的な研究成果を発表することを明らかにした。同社のIntel Foundry Technology Researchチームによる今回の発表は、半導体技術の新時代の幕開けを予感させる重要な一歩となっている。

次世代トランジスタ技術のブレークスルー

Intel Technology Researchチームが発表した次世代トランジスタ技術は、シリコンベースの進化とポストシリコン時代への準備という二つの重要な方向性を示している。

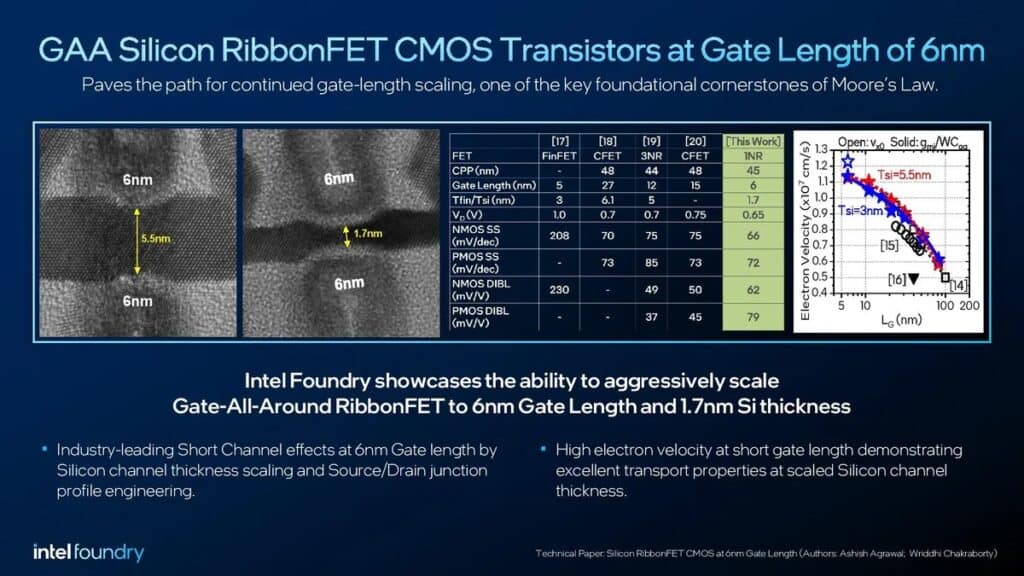

まず、シリコンベースのゲートオールアラウンド(GAA)トランジスタについて、同社は画期的な微細化を達成した。従来のFinFET構造では、フィンと呼ばれる突起状の構造の三方をゲートで囲む設計だったのに対し、GAAではナノシートと呼ばれる薄い層状の構造を完全にゲートで囲む設計を採用している。新たに開発されたGAAトランジスタでは、ゲート長を6ナノメートルまで縮小し、さらにナノリボンの厚さを1.7ナノメートルという極めて薄い寸法で実現している。これは従来のFinFET構造と比較して、フィン厚の約半分という驚異的な薄さである。この微細化により、短チャネル効果の抑制と性能向上を同時に達成している。

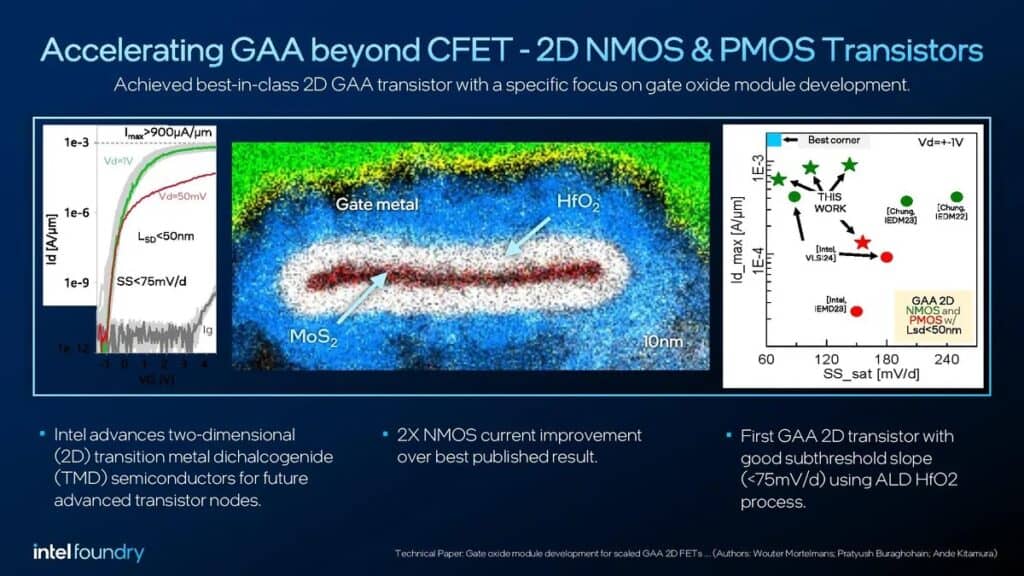

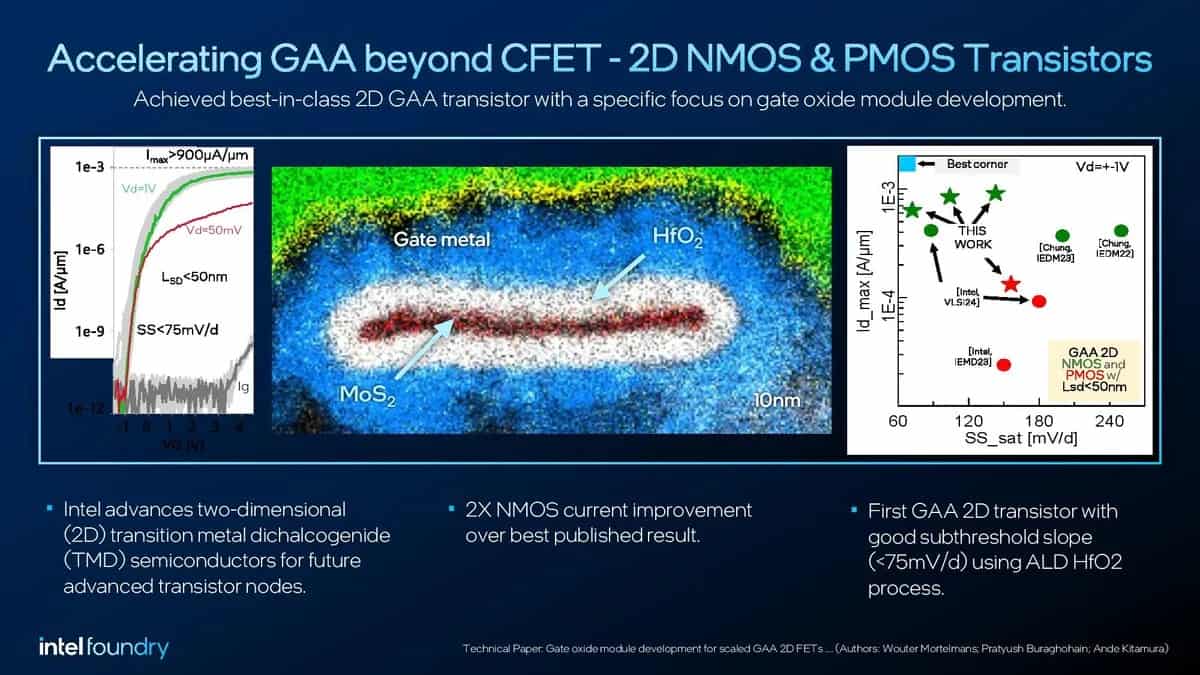

さらに注目すべきは、シリコンに代わる新材料として遷移金属ダイカルコゲナイド(TMD)を用いた2Dトランジスタの開発である。モリブデンをベースとした材料を使用し、ゲート長30ナノメートルのNMOSおよびPMOSトランジスタの作製に成功した。この2Dトランジスタは、これまでに報告された同種の研究と比較して2倍の駆動電流を実現している。原子レベルの薄さを持つ2D材料を用いることで、従来のシリコンでは達成できなかった究極の薄さと高性能を両立させている。

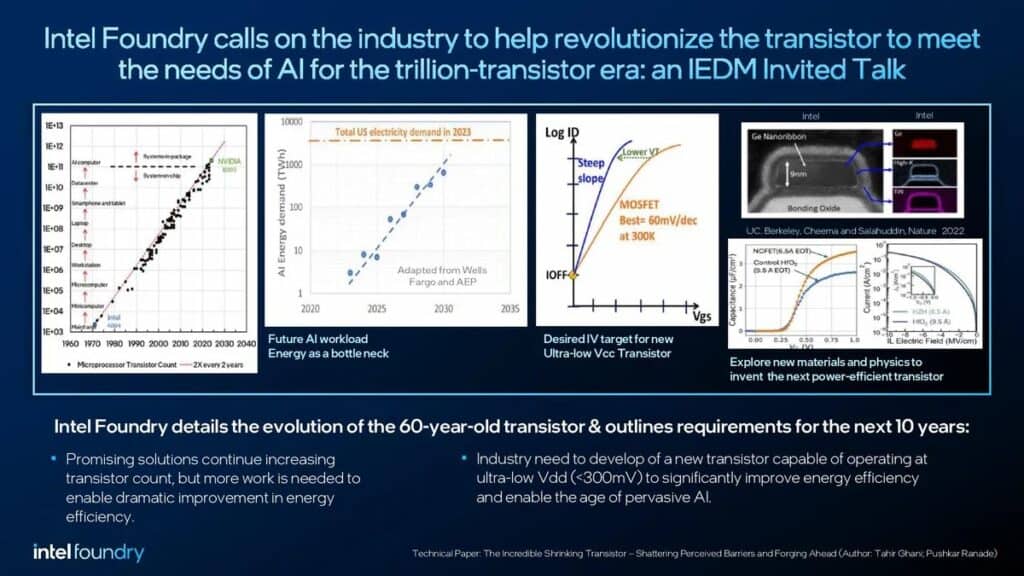

Intelはさらに、2030年代から2040年代に向けた野心的な目標として、現在の1ボルト程度から300ミリボルト未満という超低電圧での動作を実現する新しいトランジスタの開発を業界に呼びかけている。これは、半導体技術の発展における次の大きな技術的挑戦となるだろう。過去60年にわたるトランジスタ技術の進化を振り返りつつ、同社は次の60年に向けた技術革新の方向性を示している。この超低電圧動作の実現は、将来のコンピューティングデバイスの消費電力を劇的に削減する可能性を秘めている。

配線技術とパッケージングの革新

現代のプロセッサには、実に50マイル(約80キロメートル)もの配線が内蔵されており、これらの微細な配線がトランジスタ間の電力供給とデータ通信を担っている。Intelが今回発表した配線技術とパッケージングの革新は、この複雑な配線網の課題に対する画期的な解決策を提示している。

従来の銅配線プロセスでは、ダマシン法と呼ばれる加算的なプロセスが用いられてきた。この方法では、まず溝を作り、その上に拡散防止膜を形成し、さらにシード層を設けて銅めっきを行うという複雑な工程が必要であった。しかし、配線の微細化が進むにつれて、銅の体積に対する拡散防止膜とシード層の割合が増加し、抵抗値が指数関数的に上昇するという深刻な問題が生じていた。

これに対してIntelは、ルテニウムを用いた減算的なプロセスを開発した。この新技術は、従来のダマシン法とは異なるアプローチを採用し、エアギャップと呼ばれる技術も組み合わせている。エアギャップ技術は、絶縁膜の一部を空気で置き換えることで静電容量を低減する手法で、Intel はすでに14nmプロセスノードで導入していた技術である。新しいルテニウムプロセスでは、25ナノメートル未満という極めて狭いピッチでも、同じ抵抗値における静電容量を25%も低減することに成功している。特筆すべきは、この技術が高額な露光によるエアギャップ除外領域や、選択的エッチングを必要とする自己整合ビアフローを必要としない、実用的かつコスト効率の高いプロセスであるという点だ。

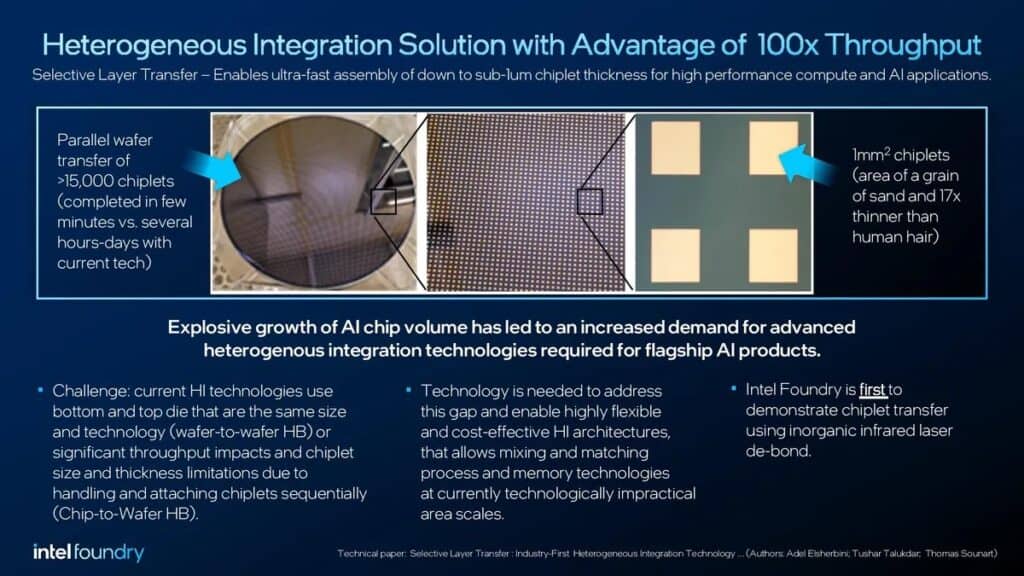

パッケージング技術においても、Intelは革新的な進展を示している。新たに開発されたSelective Layer Transfer(SLT)技術は、ウェハーレベルでのチップ接合を可能にし、チップ間の組み立てスループットを100倍に向上させる画期的な技術である。この技術は、無機赤外線レーザーデボンディングを用いて、一度に全てのダイを接合することができる。さらに、個々のダイを選択的に接合することも可能で、従来の手法では困難だった極めて薄いチップレットの実現や、より小さなダイサイズ、より高いアスペクト比の実現を可能にしている。

また、新たに発表されたEMIB-T(EMIB-TSV)技術は、Intelの既存のEMIB(Embedded Multi-Die Interconnect Bridge)技術を進化させたものである。従来のEMIBがブリッジの周りを信号が迂回する設計だったのに対し、EMIB-Tではブリッジを貫通するTSV(Through-Silicon Via)を用いて信号を伝送する。この革新により、チップ間の接続がより効率的になり、より高性能なマルチチップパッケージの実現が期待できる。

Xenospectrum’s Take

今回のIntelの発表群は、半導体技術の限界に挑戦する同社の野心的な姿勢を如実に示している。特に注目すべきは、現行技術の改良と次世代技術の開発を並行して進めているという点だ。2Dトランジスタ技術とルテニウム配線の組み合わせは、「ムーアの法則の終焉」が叫ばれる中で、新たな技術的ブレークスルーの可能性を示唆している。

しかし、これらの革新的な技術の実用化には依然として多くの課題が残されている。特に、TMD材料やルテニウムといった新材料の導入は、製造プロセスの複雑化とコスト上昇を招く可能性がある。また、300ミリボルト未満という超低電圧動作の実現には、材料科学から回路設計まで、幅広い分野での技術革新が必要となるだろう。

とはいえ、Intel Technology Researchチームが示した技術的な方向性は、半導体産業全体にとって重要な指針となる。今後は、これらの基礎研究の成果が、いかに効率的に量産プロセスへと昇華されていくかが注目される。

コメント