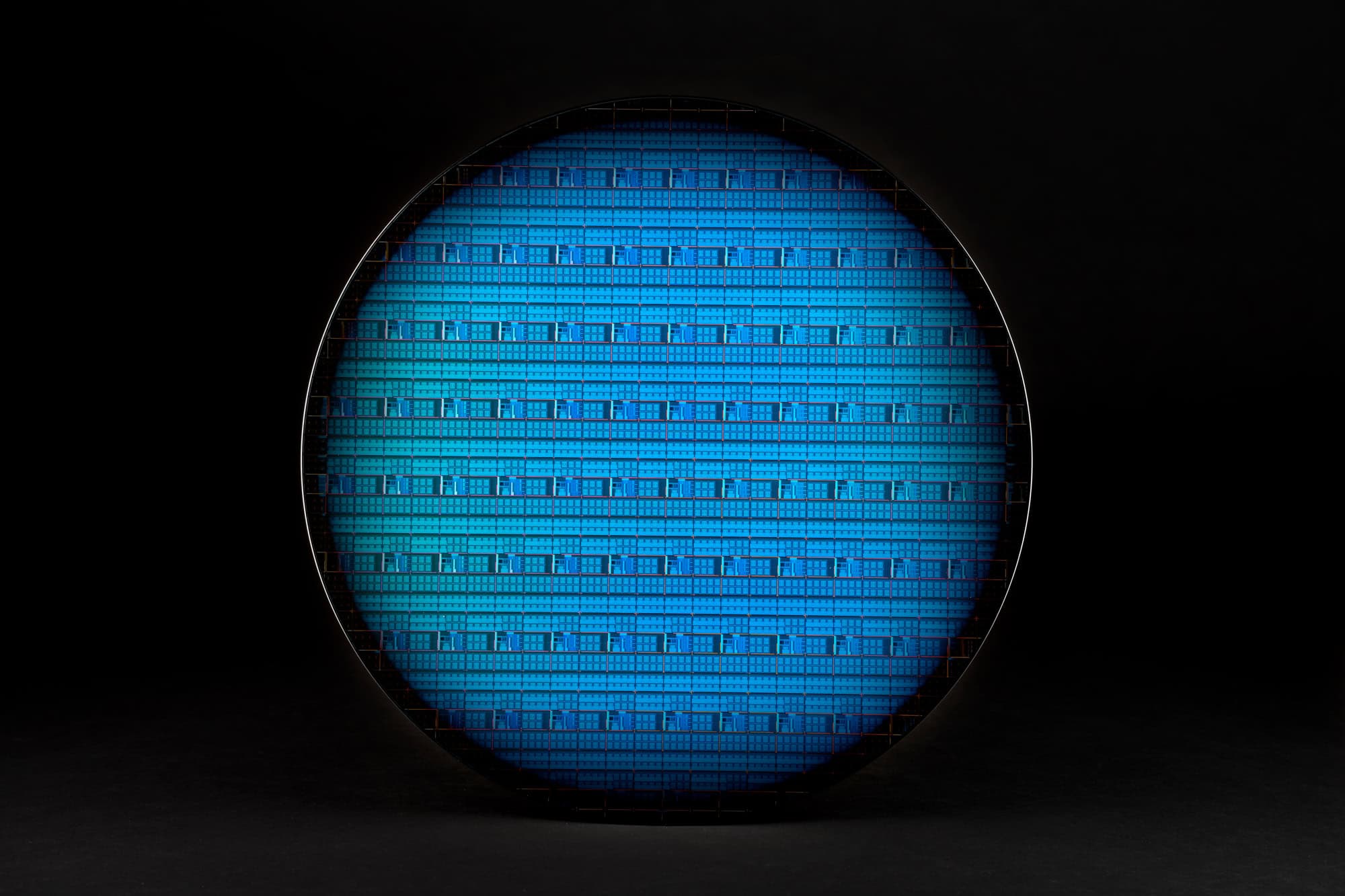

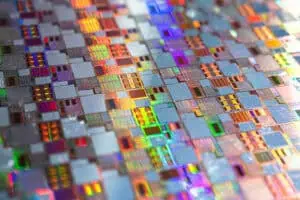

IntelのFoundry Technology Researchは、ウェハー全体でスピン量子ビット・デバイスを評価するための300ミリメートル(mm)の極低温プロービング・プロセスを開発した。このプロセスは、スピン量子ビットの均一性、忠実性、測定統計量を実証し、スピン量子ビット・デバイスの大量データを提供するものだ。

Intelの研究者によるブログ記事では、この『Nature』誌に掲載された研究成果は、量子コンピューター業界にとって重要な一歩であり、シリコンベースの量子プロセッサーの大量生産と継続的なスケーリングへの道を開くものであるとされている。

「Intelは、量子ビット密度、均一な量子ビットの再現性、大量テストによる測定統計の3つの要素を改善することで、フォールト・トレラントな量子コンピューターの構築に向けて一歩を踏み出しています」と、Intel Foundry Technology Researchの量子コンピューティング・リサーチ・エンジニアであるSam Neyens氏は述べている。

量子ビットデバイスのテストと製造の強化

Intelの300mm極低温プロービングプロセスは、ウェハー全体にわたるテストを可能にすることで、スピン量子ビットデバイスのテストを飛躍的に進歩させる物だという。研究者らは、単一電子デバイスがスピン量子ビットとして非常に優れた性能を発揮することを実証し、CMOS製造を通じて99.9%の忠実度を達成した。高忠実度とデバイスの歩留まりは、製造からスピン量子ビットの研究への道筋を合理化し、量子コンピュータのスケーリングにおける重要な進展となる。

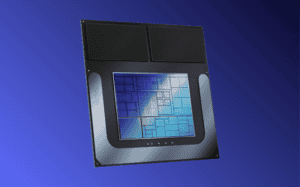

スピン量子ビットは約100ナノメートルと小さいため、超伝導量子ビットなど他の量子ビットよりも高密度である。もし1つのチップがより多くの量子ビットを搭載できれば(量子ビットの密度が高いため)、より多くの量子計算を実行することができ、チップはより強力で効率的になる。

Intelの最新の研究は、量子コンピューティングの進歩に不可欠な3つの重要分野、すなわち量子ビットの密度、再現性、大量テストに取り組んでいる。同社のシリコン・スピン量子ビットは、超伝導やイオントラップ型量子ビットを含む他のタイプよりも小さく、高密度である。この密度は、IntelのEUVリソグラフィによって可能になったもので、大量生産と相まって大規模生産を支えている。また、Intelの300mm CMOS製造方法は、数百万個の均一な量子ビットを製造するために必要な再現性と信頼性を保証するという。

極低温プロービング・システムは、従来の単一デバイス・テストよりもはるかに高速にデータを収集するプロセスを提供することで、テストを加速する。

「アライメントからデバイス測定まで、Intelのテストプロセス全体は完全に自動化され、プログラム可能であるため、クライオスタット内での単一デバイスの測定と比較して、デバイスデータの収集が数桁高速化されます」と、Neyens氏は述べている。

Bluefors社とAEM Afore社とのコラボレーションにより、300mmウェハーをチャックで1ケルビンまで冷却できるクライオ・プローバーが完成し、ウェハー全体のスピン量子ビット・デバイスの包括的なテストが可能になった。ウェハー・プローブは、2時間でデバイスをベース温度1Kまで冷却することができ、一貫した包括的なフィードバックを提供するという。

Intelの製造プロセスにより、電荷ノイズ、ドット間結合、全体的な乱れが改善され、安定したスピン量子ビットの動作に不可欠であると研究者らは強調している。

研究者たちはまた、ウェハー全体で12QDデバイスをテストし、オーミックコンタクト、ゲート、量子ドット、完全なデバイスの歩留まりを分析することで、プロセスを最適化した。この最適化により、最先端技術ノードに匹敵する高い歩留まりと低いばらつきが実現した。

同社は更に次のように述べている:「これらの知見を基に、Intelは、これらの技術を利用してインターコネクト層を増やし、量子ビット数と接続性を向上させた2Dアレイを作製すること、また、高忠実度の2量子ビットゲートを業界製造プロセスで実証することを引き続き進めていく予定です。しかし、主な優先事項は、量子デバイスのスケーリングと次世代量子チップの性能向上であり続けるでしょう」。

論文

参考文献

研究の要旨

コメント