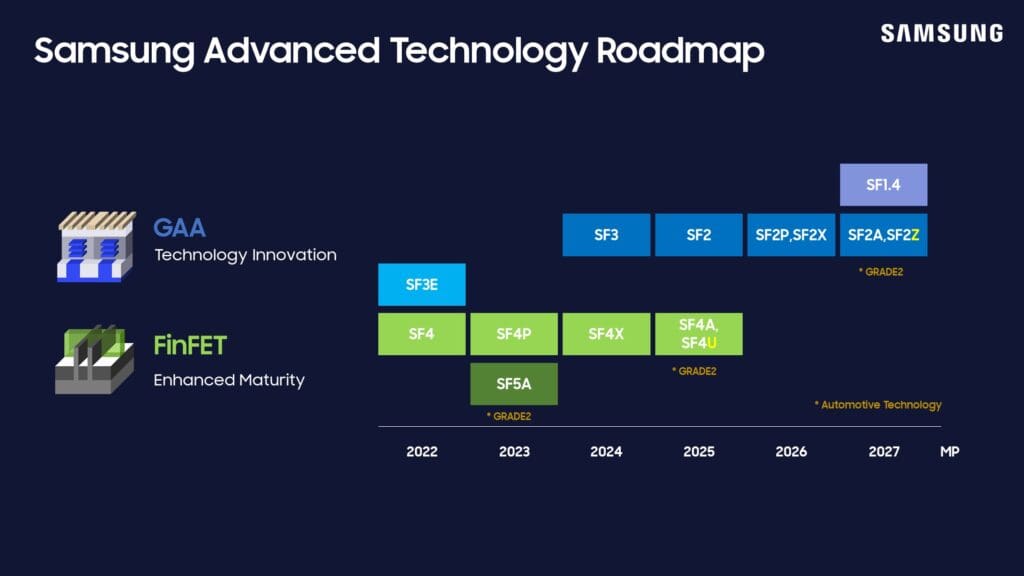

Samsungの半導体部門Samsung Semiconductorは、「Samsung Foundry Forum」において、今後数年間の製造計画に関する詳細や、2nmおよび3nmチップのプロセスロードマップ、そしてAIおよび自動車用チップのための特殊ノードの計画を発表した。

2025年に2nm、2027年には1.4nmチップを計画

Samsungによれば、2025年に2nmチップを、2027年に1.4nmチップを製造する計画だという。

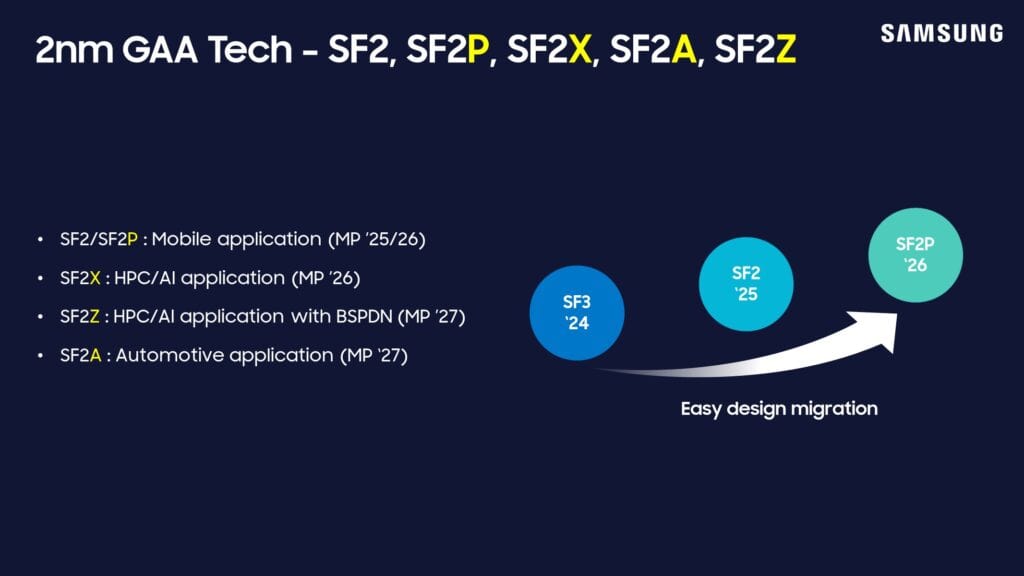

加えて、同社は、2025年にモバイルデバイス向けの2nmチップの量産を開始する準備が整うことを明らかにしており、初代2nmプロセスである「SF2」(以前はSF3Pと呼ばれていた)は2025年に準備が整い、改良版の2nmプロセスである「SF2P」は2026年に準備が整う予定とのことだ。

SF2PはSF2より高速だが密度が低いトランジスタを特徴とする。これは、業界では通常のトレードオフである、密度を少し下げながら速度を向上させる方向へのシフトを示している。

AIおよび高性能コンピューティング(HPCおよびサーバー)チップ向けに設計された2nmプロセスの特殊バージョンであるSF2Xは、2026年に、自動車用チップ向けの2nmプロセスであるSF2Aは、2027年に量産が開始される予定だ。

2nmプロセスでは、これまでに明らかになっている「SF2」、「SF2P」、「SF2X」、「SF2A」に加えて、新たに第4世代2nmプロセス「SF2Z」が発表された。

SF2Zでは、Samsungはバックサイドパワーデリバリーネットワーク(BSPDN)を採用する予定だ。BSPDNの導入によって、性能向上とトランジスタ密度の向上を可能にする。BSPDNについては、IntelはIntel 20Aでの導入を計画しており、TSMCはA16プロセスにおいて導入することを明らかにしている。

各社のBSPDNはそれぞれ技術的に異なっており、TSMCのSuper Power Rail(SPR)は、IntelのPowerViaよりも統合の面で一歩進んでいる。SamsungがSF2ZのためにどのようなBSPDNの実装を計画しているかは不明であるが、SF2に対してSF2Zは電力効率、性能、面積(PPA)の大幅な改善を提供することが期待されている。特にHPC(高性能計算)チップがその恩恵を受けるであろう。SF2Zの量産は2027年に予定されている。

| HVMスタート | 2023 | 2024 | 2025 | 2026 | 2027 | |

|---|---|---|---|---|---|---|

| Intel | プロセス | Intel 3 | Intel 20A | Intel 18A | Intel 14A | Intel 10A |

| FET | FinFET | RibbonFET (GAAFET) | ||||

| 電源供給 | 表側 | PowerVia (BSPDN) | ||||

| EUV | 0.33 NA EUV | 0.55 NA EUV + DSA | ||||

| Samsung | プロセス | SF3E | SF3 | SF2 | SF2P/SF2X | SF2Z/SF1.4 |

| FET | GAAFET | |||||

| 電源供給 | 表側 | BSPDN? | ||||

| EUV | 0.33 NA EUV | ? | ? | ? | ||

| TSMC | プロセス | N3E/N3P | N3S/N3X | N2 | A16 | A14 (?) |

| FET | FinFET | GAAFET | ||||

| 電源供給 | 表側 | Super Power Rail (BSPDN) | ||||

| EUV | 0.33 NA EUV | ? | ||||

Samsungは、Gate All Around (GAA) トランジスタが性能と歩留まりの両面で継続的に成熟していると述べており、GAAは、同社の3nmプロセスで導入され、2nmプロセスにも適用される予定である。ただし、具体的な歩留まりは明らかにしていない。

もう一つの新しいプロセスノードはSF4Uである。これはSamsungによると、特に高いボリュームに対応した4nmプロセスの特殊バージョンだ。光学的シュリンクを取り入れることにより、PPAの改善も見込まれている。SF4Uの量産は2025年に予定されている。

Samsungによると、最初のサブ2nmセグメントのプロセスノードであるSF1.4も予定通り進行している。性能と歩留まりは予想範囲内にあり、量産は2027年に開始できると予想されている。

ただし、前述のSF2Zとは異なり、SF1.4にはBSPDNが搭載されないため、Samsungは、2nmクラス(20A)と1.6nmクラス(A16)のノードでBSPDNを導入する同業他社のIntelやTSMCとは一線を画している。SamsungがSF1.4でBSPDNを省略した理由は不明だが、同社がこの生産ノードをもう少しコスト効率の良いものにしたかった可能性がある。

今年はまず、第二世代SF3プロセスの量産が予定されている。これは年後半に開始される見込みだ。SF3は、Samsungが初めてGAA(Gate-all-around)トランジスタを採用したプロセスであり、基本的にはすでに3年間製造されている。しかし、SF3E/3GAEは初めは比較的単純な暗号通貨マイニングチップの契約しか獲得できなかった。また、長い間、SamsungのSF3プロセスの歩留まりが非常に低いと噂されていたが、最近になってこの状況が大幅に改善されたため、SamsungもTSMCの代替として頻繁に言及されるようになった。一部の報告によると、Samsung自身のExynos W1000がこの技術を使用する最初のチップとなる予定だ。

今年後半には、Galaxy S25シリーズ向けの次世代Exynosスマートフォンチップセットの量産も開始される可能性がある。このチップセットもSF3プロセスを使用し、来年初めに発表される可能性がある。

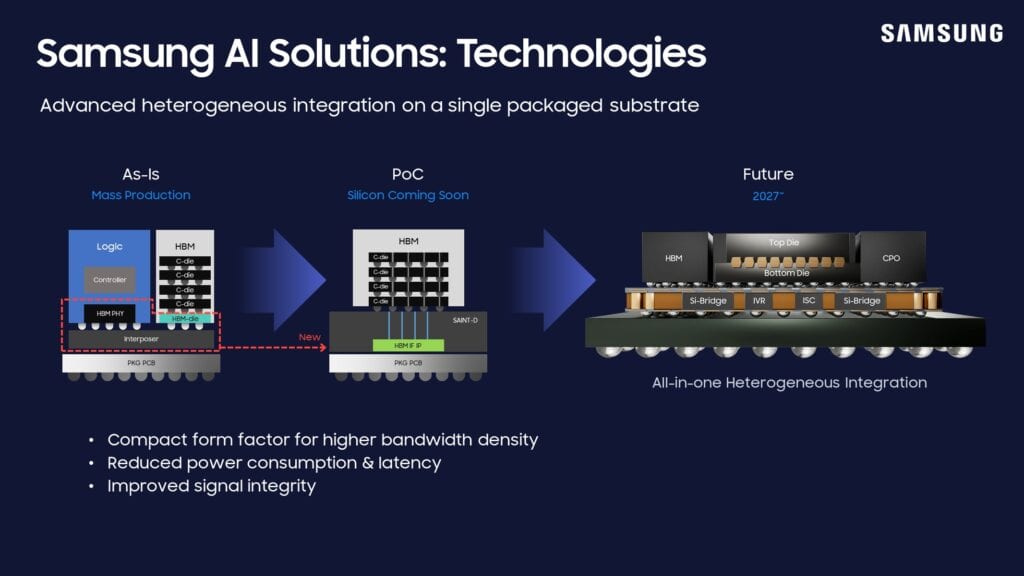

パッケージングはAIアクセラレータに集中

SamsungがFoundryビジネスにおいて今後再び大口顧客を迎えるかどうかは、SF2Zおよび他のプロセスの発展次第である。しかし、パッケージングにおいても遅れをとらないようにし、複数のチップを垂直に基板上に統合する現在の方法に加え、新しい技術にも取り組んでいる。

次のステップとして、メモリーチップなどの個々のコンポーネントを基板に直接統合することを見据えている。これにより、信号の整合性と性能密度、すなわち帯域幅を大幅に向上させることができる。将来的には、さまざまな2.5Dおよび3Dの形態での複雑な統合を伴うパッケージングも計画されている。

Source

- Samsung Semiconductor: Samsung Showcases AI-Era Vision and Latest Foundry Technologies at SFF 2024

コメント