Samsungは、世界最大のメモリチップメーカーとして、来年に先進的な三次元(3D)チップパッケージング技術を発表する予定だ。この技術は、台湾のTSMCのパッケージング技術「CoWoS」と競合するもので、「SAINT(Samsung Advanced Interconnection Technology)」と名付けられ、これによりSamsungは、AIチップを含む高性能チップに必要なメモリとプロセッサを、より小さなサイズで統合する事を目指している。

Samsung初の3Dパッケージング技術

Samsungが提供する3Dパッケージング技術「SAINT」には、以下の3種類がある:

- SAINT S – SRAMメモリチップとCPUの垂直スタック用

- SAINT D – CPU、GPU、DRAMなどのコアIPの垂直パッケージング用

- SAINT L – アプリケーション・プロセッサ(AP)のスタック用

現在の2.5Dパッケージング技術は、ほとんどの場合、異なるタイプのチップを横に並べて組み立てる。Samsungは、既にSAINT Sについては検証テストを終えており、今後クライアントとのさらなるテストの後、来年に商業サービスを開始する予定のようだ。

半導体製造の最終段階の一つであるパッケージングは、チップを保護ケースに収め、腐食を防ぎ、既製のチップを組み合わせて接続するインターフェースを提供する技術だ。TSMC、Samsung、Intelなどの主要なチップメーカーは、異なる半導体を統合したり、複数のチップを垂直に接続する先進的なパッケージング技術で激しく競い合っている。先進的なパッケージングは、複数のデバイスを単一の電子デバイスとして統合し、パッケージ化することを可能にする。

パッケージングは、技術的に難しく、時間がかかる超微細加工を行わずに半導体の性能を向上させることができるものだ。コンサルティング会社のYole Intelligenceによると、世界の先進チップパッケージング市場は、2022年の443億ドルから2027年には660億ドルに成長すると予測されている。660億ドルのうち、3Dパッケージングは約4分の1、つまり150億ドルを占めると見込まれている。

TSMCは、ChatGPTなどの生成AIの成長に伴い、急速に増加している技術の現在の主流である2.5Dパッケージングをリードしている。この技術は、データのボトルネックを減らすために、できるだけ近くにチップを配置する事を可能にする。世界No.1の受託チップメーカーであるTSMCは、AppleやNVIDIAを含むクライアントのために、3Dチップ間スタッキング技術SoICをテストし、アップグレードするために大規模な投資を行っている。TSMCは7月、新しい国内先進パッケージング工場に900億台湾ドル(約4222億円)を投資すると発表した。

今月初め、世界第3位のファウンドリである台湾のUMCは、シリコンスタッキング技術を使用してメモリとプロセッサを効率的に統合するための最先端ソリューションをクライアントに提供するために、ウェーハー対ウェーハー(W2W)3D ICプロジェクトを開始した。UMCは、ASE、Winbond、Faraday、Cadence Design Systemsなどのパッケージング企業と協力して、3Dチップ統合技術を活用し、エッジAIアプリケーションの特定の要件に対応する野心的な取り組みを行っている。Intelは、次世代の3Dチップパッケージング技術Foverosを使用して、先進的なチップを製造している。

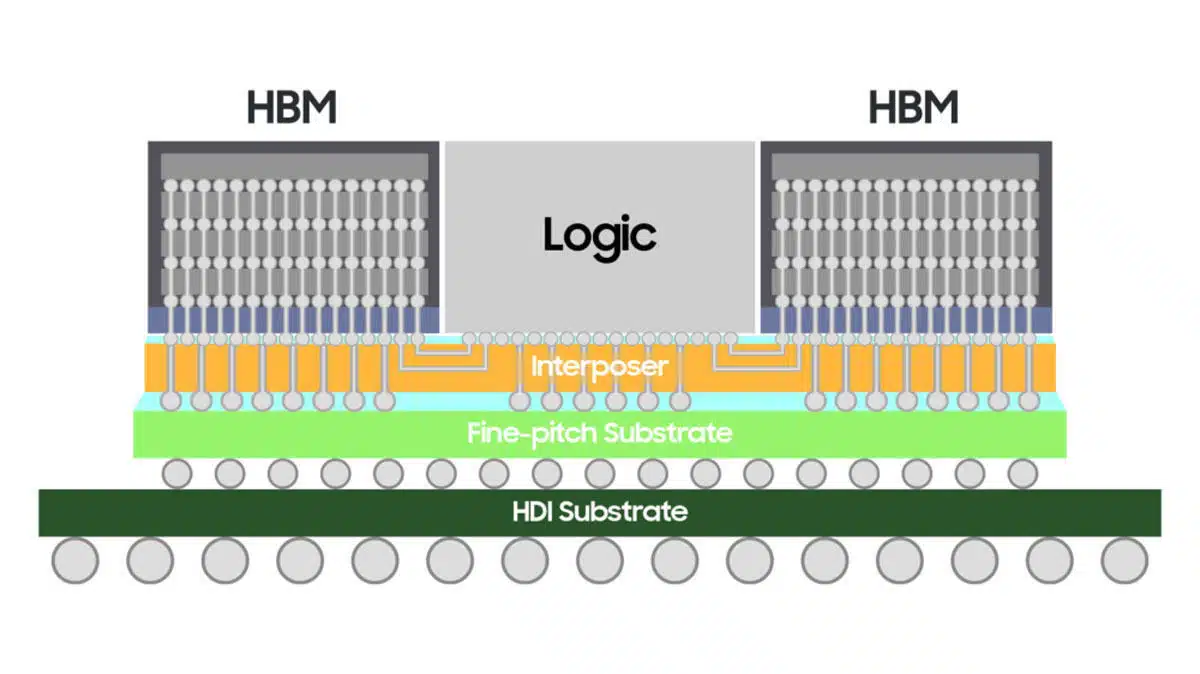

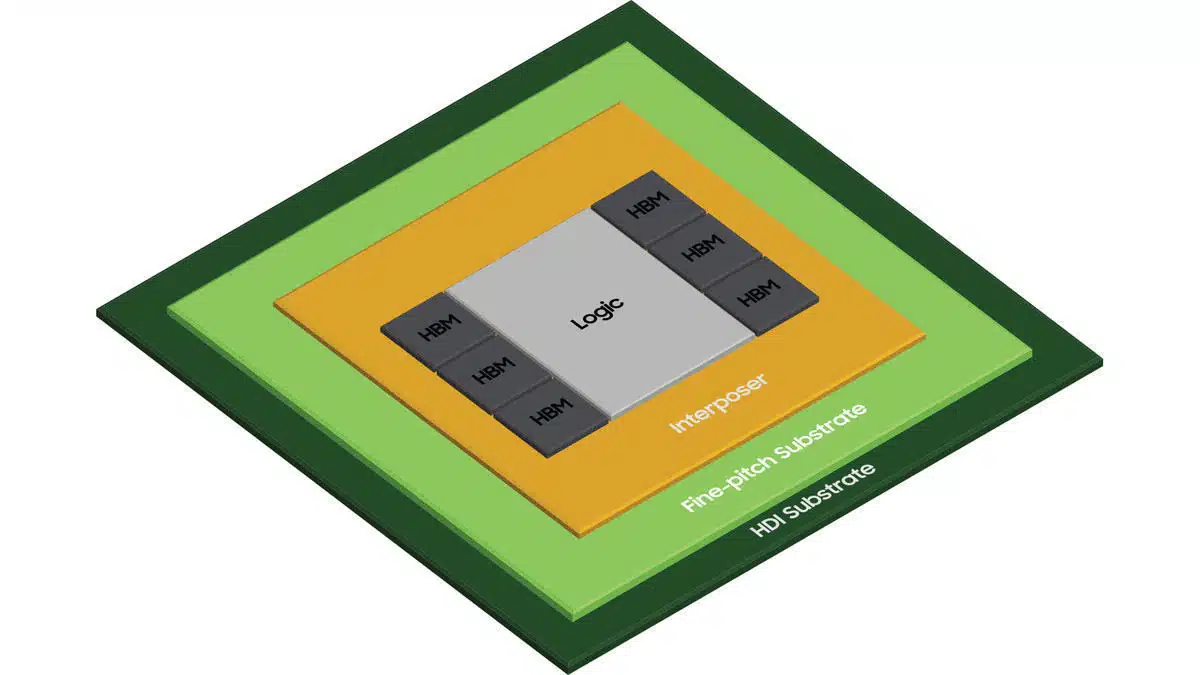

Samsungは、世界第2位のファウンドリ企業として、2021年に2.5Dパッケージング技術H-Cubeを発表して以来、チップパッケージング技術の開発を加速している。2.5Dパッケージング技術は、ロジックチップや高帯域幅メモリ(HBM)をシリコンインターポーザの上に積み重ねることができる。Samsungは4月、チップ製造からパッケージング、テストまでの全プロセスを取り扱うパッケージングターンキーサービスを提供していると発表した。新しいSAINT技術を用いて、Samsungはデータセンター用のAIチップや、オンデバイスAI機能を備えたモバイルAPの性能向上を目指している。

Sources

コメント