チップパッケージング– tag –

-

TSMCとAmkor、米国での先端パッケージング技術の提供で提携

台湾のTSMCと米国の半導体企業Amkor Technologyが、米国での先進的なチップパッケージング技術の提供に向けて提携することを発表した。この提携は、米国の半導体サプライチェーンを強化し、世界市場での地位を向上させるという、CHIPS法の主要目標を支援す... -

TSMCが2027年までに革新的CoW-SoW技術で巨大AIチップ量産へ

TSMCが2027年までに革新的なCoW-SoW(System-on-Wafer)パッケージング技術の量産を計画していることが明らかになった。この技術は、巨大なチップの開発を可能にし、これまで以上に高性能なAIチップの登場を約束する画期的な動きとなるだろう。 TSMCが描く... -

Google、次世代Tensor G5はTSMCの3nmプロセスとInFO-POPパッケージングを採用する

Googleが次世代スマートフォン用チップセット「Tensor G5」の開発を加速させている。最新の報道によると、GoogleはTensor G5の製造をTSMCに委託し、同社の最先端3nmプロセスを採用する方針を固めたという。この戦略的決定は、GoogleがAIスマートフォン市場... -

TSMC、3nmと5nmプロセスを最大8%値上げ、CoWoSパッケージングの値上げも計画中と伝えられる

世界最大の半導体ファウンドリであるTSMCが、最先端の3nmと5nmプロセスの価格を最大8%引き上げる計画であることが明らかになった。この値上げは、高い需要と市場での優位な立場を背景に、TSMCが利益率を維持しつつ、増加するコストに対応するための戦略的... -

NVIDIA、TSMCに専用のCoWoSパッケージング製造ラインを要請するも断られる

NVIDIAのCEO、Jensen Huang氏がTSMCに専用のチップパッケージング製造ラインの設置を要請したものの、断られたことが台湾メディアによって伝えられている。半導体業界で重要性を増すパッケージング技術をめぐり、AI市場をリードするNVIDIAと世界最大の半導... -

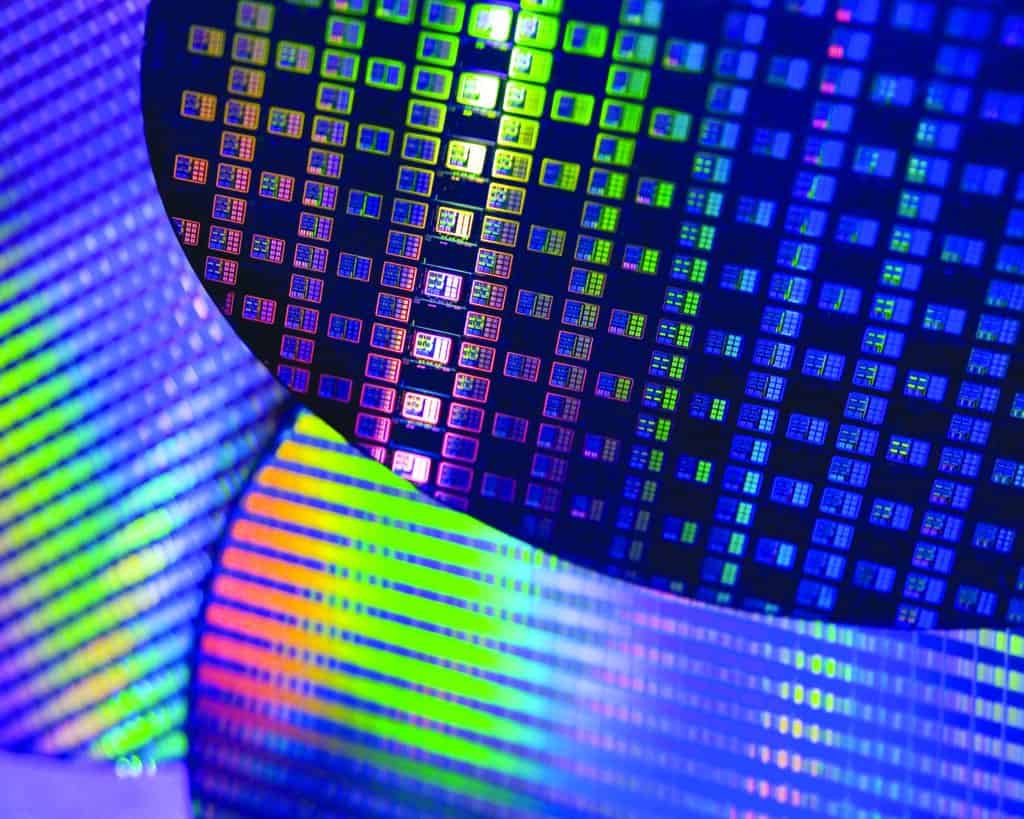

TSMC、510x515mmの長方形シリコンウェハーの使用を検討中か

シリコンウェハーと言えば、円形で虹色に輝くディスクのようなイメージが一般的だが、マルチチップレットプロセッサが増えていき、ますます多くのトランジスタを収容することでプロセッサの肥大化が進むことに対応する為、TSMCでは長方形のパネル状基板を... -

TSMC、極めて高い需要により3nmプロセスやCoWoSパッケージング等の値上げを検討と報じられる

TSMCの先端プロセスは、SamsungやIntelと言った他ファウンドリと比較して旺盛な需要により、生産能力はフル稼働状態にあるが、こうした需要の高い先端プロセスについて、同社は海外展開と電力価格の上昇によるコスト圧力から、値上げを検討している様だ。 ... -

Samsung、CPUやGPUの上にHBM4を積層する「SAINT」3Dパッケージングを2025年までに導入へ

SamsungはAI特需に湧く業界の中で、HBM(高帯域幅メモリ)の供給では後れを取っているが、早くも次世代のHBM4での革新に目を向けており、そこでは革新的な3Dパッケージングテクノロジーを導入する計画のようだ。 3Dパッケージングテクノロジー開発競争も激... -

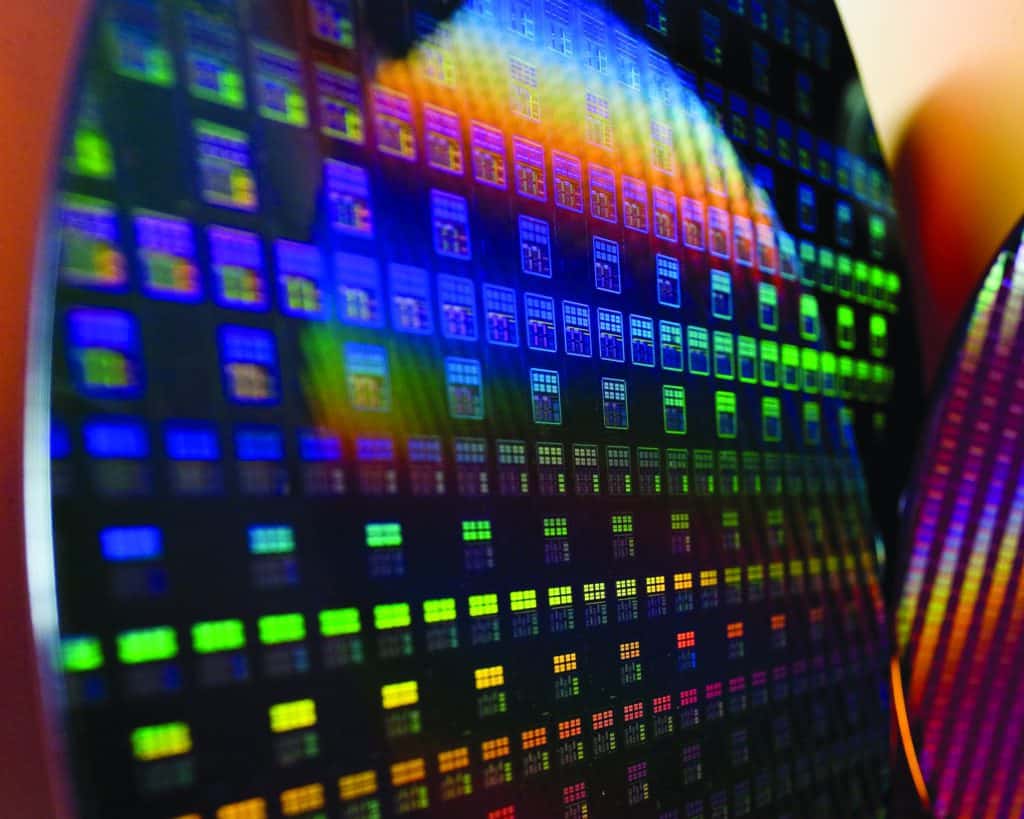

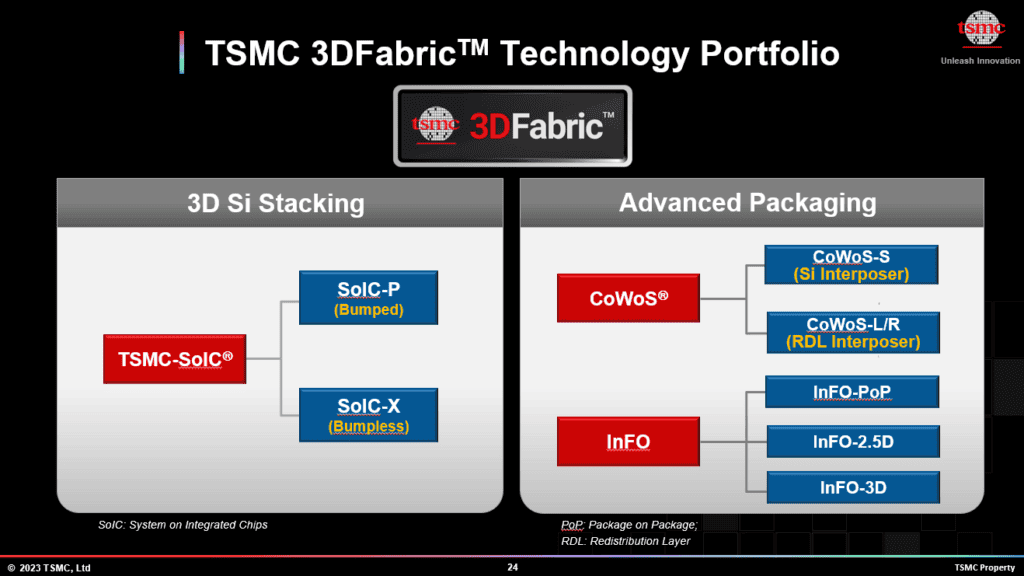

TSMC、3D積層SoICパッケージテクノロジーの進化により数年以内に1.6nmと2nmダイを積層させることも可能に

TSMCは現在全世界でテクノロジーシンポジウムを開催中だ(6月28日には日本でも開催される)。2nmや1nm世代と言った、最先端プロセスが注目されがちではあるが、同社はInFO、CoWoS、TSMC-SoIC等の先進パッケージング技術についても急速に技術開発を進めてお... -

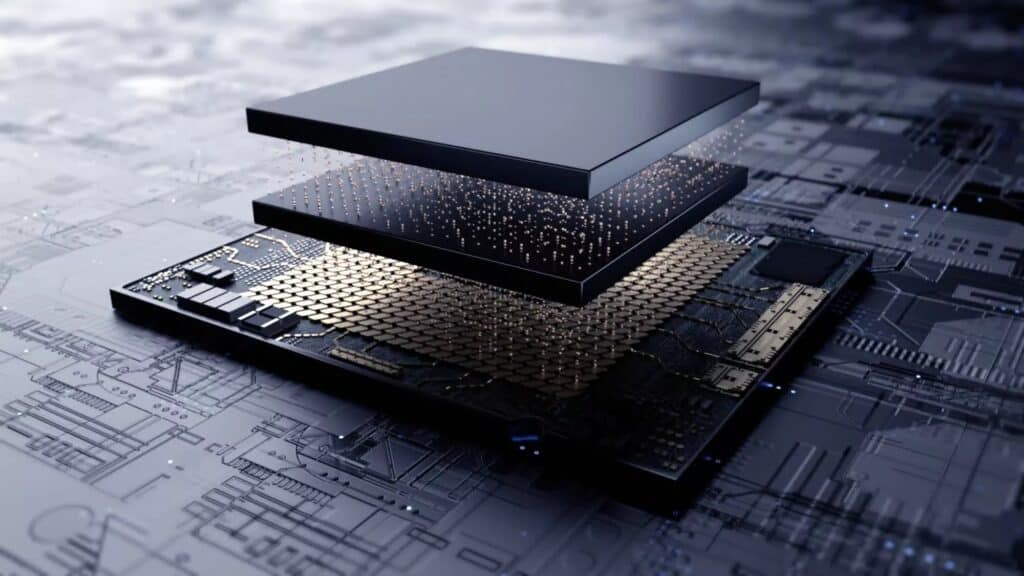

TSMC、3D積層による新しいシステム・オン・ウェハー・プロセスを発表

TSMCは北米技術シンポジウムで、同社の今後の半導体技術とチップパッケージング技術の両方の取り組みについて詳述している。 TSMCがリリースする予定の、BSPDNを採用するA16製造ノードについてはすでに取り上げた。同社はまた、System-on-Wafer(SoW)と名...

12