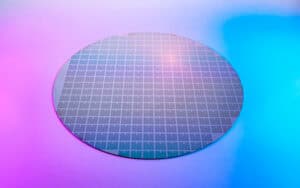

台湾の半導体製造大手TSMCが、次世代の2nm(N2)プロセスの試験生産ラインの構築を開始した。同社は2026年末までに月産13万枚という大規模な生産体制の確立を目指している。

段階的な生産能力の拡大計画が明らかに

TSMCが2025年第1四半期から、新竹の寶山工場(Fab 20)の2nmプロセス試験生産ライン(Engineering line)において生産を開始する計画である事がサプライチェーンからの情報によって明らかになったとMoneyDJが報じている。初期段階での月産能力は3,000~3,500枚に設定されており、製造プロセスの確立と最適化に向けた取り組みが進められている。

同社の生産能力拡大は、新竹と高雄の2つの主要拠点で並行して展開される。新竹寶山工場では、2025年第4四半期までに月産能力を2~2.5万枚まで引き上げる計画だ。その後さらなる増強が進められ、2026年末から2027年初頭にかけては月産6~6.5万枚という大規模な生産体制が整えられる見通しとなっている。

一方、高雄工場では2つのフェーズに分けた展開が計画されている。まずP1(第1工場)が2025年第2四半期から小規模な試験生産を開始し、続いてP2(第2工場)が2025年末から2026年初頭にかけて稼働を開始する。高雄工場全体では2025年末時点で月産2.5~3万枚の体制を整え、その後2026年末から2027年第1四半期にかけて月産6~6.5万枚まで生産能力を拡大する計画だ。

これら2つの製造拠点における段階的な能力増強により、TSMCの2nmプロセス全体の生産能力は2025年末時点で月産5万枚を超え、2026年末には最大で月産12~13万枚という大規模な生産体制が確立される見込みとなっている。この急速な生産能力の拡大は、次世代プロセスに対する主要顧客からの旺盛な需要を反映したものといえる。

この生産能力の拡大計画において特筆すべきは、新竹と高雄の両工場で同時並行的に能力増強が進められる点である。これはTSMCの製造技術の成熟度の高さを示すとともに、地理的なリスク分散の観点からも重要な意味を持つ取り組みといえる。

高性能化と省電力化を両立した次世代プロセス

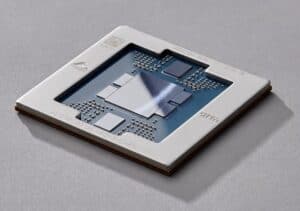

TSMCが IEEE国際電子デバイス会議(IEDM)で公表したデータによると、2nmプロセス技術は前世代の3nmプロセスと比較して顕著な性能向上を実現している。同じ動作電圧条件下において、消費電力を24~35%削減できる特性を持つ一方で、消費電力を維持したまま演算性能を15%向上させることも可能だ。さらに、単位面積あたりのトランジスタ密度は3nmプロセス比で1.15倍に向上しており、より高度な集積化による省スペース化も達成している。

この技術的進展を実用面から見ると、モバイルデバイスにおけるバッテリー持続時間の大幅な改善や、データセンター向けプロセッサの電力効率向上につながることが期待される。特に注目すべきは、AppleのiPhone 18向けに開発されるA20チップでは、この2nmプロセスと新しいWMCM(多チップモジュール)封装技術が組み合わされる点だ。WMCMは、従来のInFo-PoP技術に代わる新しい実装方式として採用され、DRAMとロジックICの平面実装にRDL(再配線層)を活用することで、より効果的な放熱性能の実現を目指している。

TSMCの会長であるC.C. Wei氏は、2nmプロセスへの需要が3nmプロセスを上回る水準にあることを明らかにしている。この強い需要は、同プロセスがもたらす性能向上と省電力化の恩恵が、次世代のコンピューティング要件に合致していることを示唆している。実際に、AppleをはじめとしてMediaTek、Qualcomm、Intel、NVIDIA、AMD、Broadcomといった半導体業界の主要企業が、この次世代プロセスの採用を計画している。

この新プロセスの工業化に向けて、TSMCは新竹の寶山工場に専用の先進パッケージング施設を設置することも計画している。これは特にAppleのA20チップ向けに「専用工場」として運用される予定で、高度な封装技術と最先端プロセスの統合による付加価値の創出を目指している。このような垂直統合的なアプローチは、チップの性能と信頼性をさらに向上させる可能性を秘めている。

Xenospectrum’s Take

TSMCの2nmプロセス展開では、Appleが最初の顧客として名を連ね、その後にMediaTek、Qualcomm、Intel、NVIDIA、AMD、Broadcomといった半導体業界の主要プレイヤーが続くという構図が従来通り行われそうだ。これは、同社の技術的優位性と産業における不可欠な存在感を如実に示している。

特筆すべきは、スマートフォン向けのWMCM封装技術の採用だ。これはCOW(チップスタッキング)とInFoの技術を統合し、DRAMとロジックICを平面実装する新しいアプローチである。熱問題に対する解決策として期待されるが、同時に製造の複雑性も増すことになる。TSMCがこの技術的課題をいかに克服するか、業界の注目が集まっている。

Sources

コメント