TSMCは米国サンフランシスコで開催されたIEEE International Electron Device Meeting (IEDM)において、次世代の2nmプロセス技術(N2)の詳細を明らかにした。同社初となるゲートオールアラウンド(GAA)ナノシート・トランジスタ技術の採用により、現行の3nmプロセスと比較して最大30%の電力効率向上または15%の性能向上を実現しているとのことだ。

革新的なナノシート・アーキテクチャがもたらす飛躍的進化

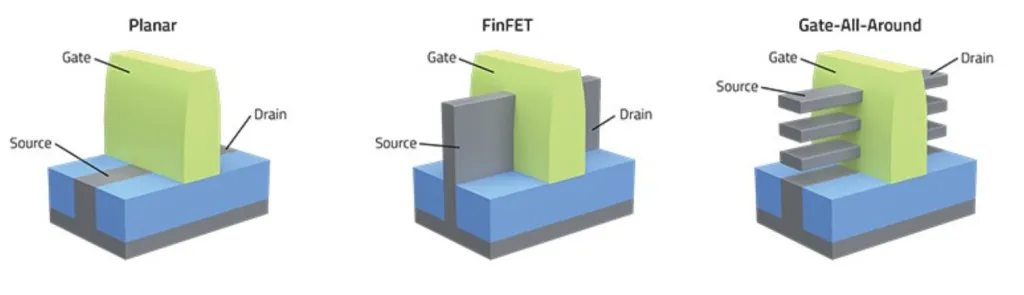

TSMCのR&D担当副社長Geoffrey Yeap氏が「4年以上の努力の結晶」と表現したN2プロセスは、同社の半導体製造技術における重要な転換点を示している。この技術革新の核心は、従来のFinFETアーキテクチャから、ゲートオールアラウンド(GAA)ナノシート・トランジスタへの移行にある。

従来のFinFETトランジスタは、シリコン基板から垂直に突き出た「フィン」と呼ばれる構造を持ち、このフィンの三面をゲート電極が取り囲む設計だった。一方、新たなナノシート・トランジスタは、薄いシリコンリボンを複数層重ねた構造を採用し、これらのリボンの全周をゲート電極が完全に包み込む形となっている。この構造的な革新により、電流の流れに対する制御性が劇的に向上した。

さらに注目すべきは、TSMCが「N2 NanoFlex」と名付けた革新的な設計技術である。従来のFinFETでは、トランジスタの性能を調整する際、フィンの本数を1本、2本、3本というように整数単位でしか変更できなかった。これに対しN2 NanoFlexでは、ナノシートの幅を自由に調整することで、従来では実現不可能だった中間的な性能値(例えば1.5本分のフィンに相当する性能)を実現できるようになった。

この柔軟性は、チップ設計に革新的な可能性をもたらしている。例えば、同一チップ上で汎用ロジック回路には細いナノシートを、高性能が求められるCPUコアには幅広のナノシートを使用するといった、より細やかな最適化が可能となった。TSMCによれば、この設計の自由度の向上により、チップ全体の性能と電力効率のバランスを、これまでにない精度で最適化できるようになったという。

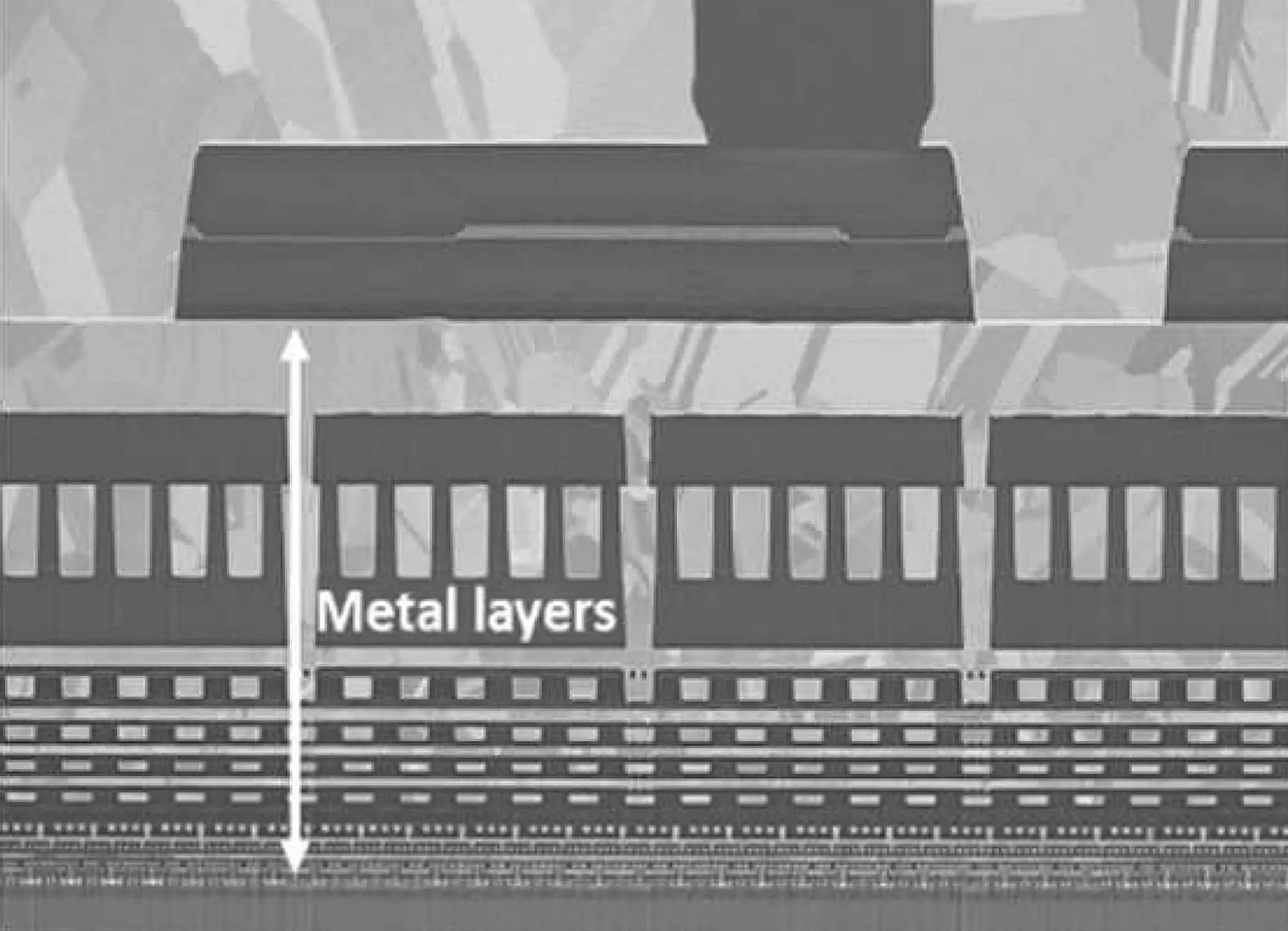

さらに、この新アーキテクチャは製造プロセスの効率化にも貢献している。TSMCは新たに「1P1E」(1回の露光と1回のエッチング)による最初の金属層(M1)の形成を実現し、製造工程の複雑さを低減させることに成功。これにより、標準セルの寄生容量を約10%削減し、複数のEUVマスクを節約することが可能となった。このような製造プロセスの革新は、将来的なコスト削減の可能性も示唆している。

TSMCは、2nmプロセスの性能が15%向上し、消費電力が最大30%削減され、ノード効率が大幅に向上したことを明らかにした。 さらに、NanoFlexの採用により、トランジスタ密度は1.15倍に向上したという。

SRAMの密度向上がプロセッサ設計に新たな可能性

プロセッサの性能を左右する重要な要素であるSRAM(Static Random Access Memory)は、ここ数世代にわたり微細化の壁に直面してきた。6つのトランジスタで構成される基本的なSRAMセルは、その構造的な制約から、他のロジック回路と比較して微細化が困難とされてきた。しかし、TSMCの2nmプロセスは、この長年の課題にも革新的なブレイクスルーをもたらしている。

N2プロセスは、平方ミリメートルあたり38メガビットという、過去最高密度のSRAMセルを実現したとのことだ。これは前世代のN3プロセスと比較して11%の密度向上を示しており、特に注目すべきは、N3プロセスが前世代から実現した6%の向上率を大きく上回っているという点である。この飛躍的な進歩は、ゲートオールアラウンド構造の本質的な優位性を如実に示している。

さらに、TSMCはSRAMの電力効率も大幅に改善している。ナノシート・トランジスタの採用により、しきい値電圧のばらつき(Vt-sigma)が低減され、その結果、High Current(HC)マクロでは約20mV、High Density(HD)マクロでは30〜35mVの最小動作電圧(Vmin)低減を達成した。これにより、約0.4Vという極めて低い電圧でも、安定した読み書き動作が可能となっている。

この技術革新の意義は、単なる密度向上にとどまらない。現代のプロセッサ設計において、SRAMはキャッシュメモリとして重要な役割を果たしており、その容量と配置は演算性能に直接的な影響を与える。特に、機械学習やAIワークロードでは、大容量のオンチップメモリが不可欠となっている。N2プロセスによって実現された高密度SRAMは、同じシリコン面積でより大容量のキャッシュメモリを実装できることを意味する。

加えて、TSMCは高性能コンピューティング(HPC)向けに、約200fF/mm²の容量を提供するスーパーハイパフォーマンスMiM(SHP-MiM)キャパシタも導入している。これは過渡的な電圧降下を抑制し、より高い最大動作周波数(Fmax)の実現を可能にする。さらに、新しいCu RDLオプションと4.5μmのSoICボンドピッチを最適化することで、AI、HPC、そしてモバイル設計における3D積層の可能性も広がっている。

これらの技術的進歩は、次世代プロセッサの設計に新たな可能性を開くものである。高密度かつ低電力なSRAMの実現は、より複雑な演算処理や大規模なキャッシュを必要とする次世代アプリケーションの発展を支える重要な基盤となるだろう。

Xenospectrum’s Take

TSMCの2nmプロセスの発表は、半導体業界における重要な転換点を示している。Samsung、Intelともに同様のGAAトランジスタ技術の開発を進めているが、TSMCが示した具体的な性能指標と量産時期(2025年後半)は、同社の技術的優位性を改めて印象付けるものとなった。

特に注目すべきは、これまで微細化の足かせとなっていたSRAM密度の向上である。AIワークロードの増大により、オンチップメモリの重要性は年々高まっている。この ブレークスルーは、次世代プロセッサの設計に新たな可能性をもたらすだろう。

ただし、これらの技術的進歩には相応のコストが伴う。N2プロセスのウェハー価格は、現行の3nmプロセスと比較して10%以上の上昇が見込まれている。この「技術の民主化」と「コスト」のバランスは、今後の半導体業界の重要な課題となるだろう。

Sources