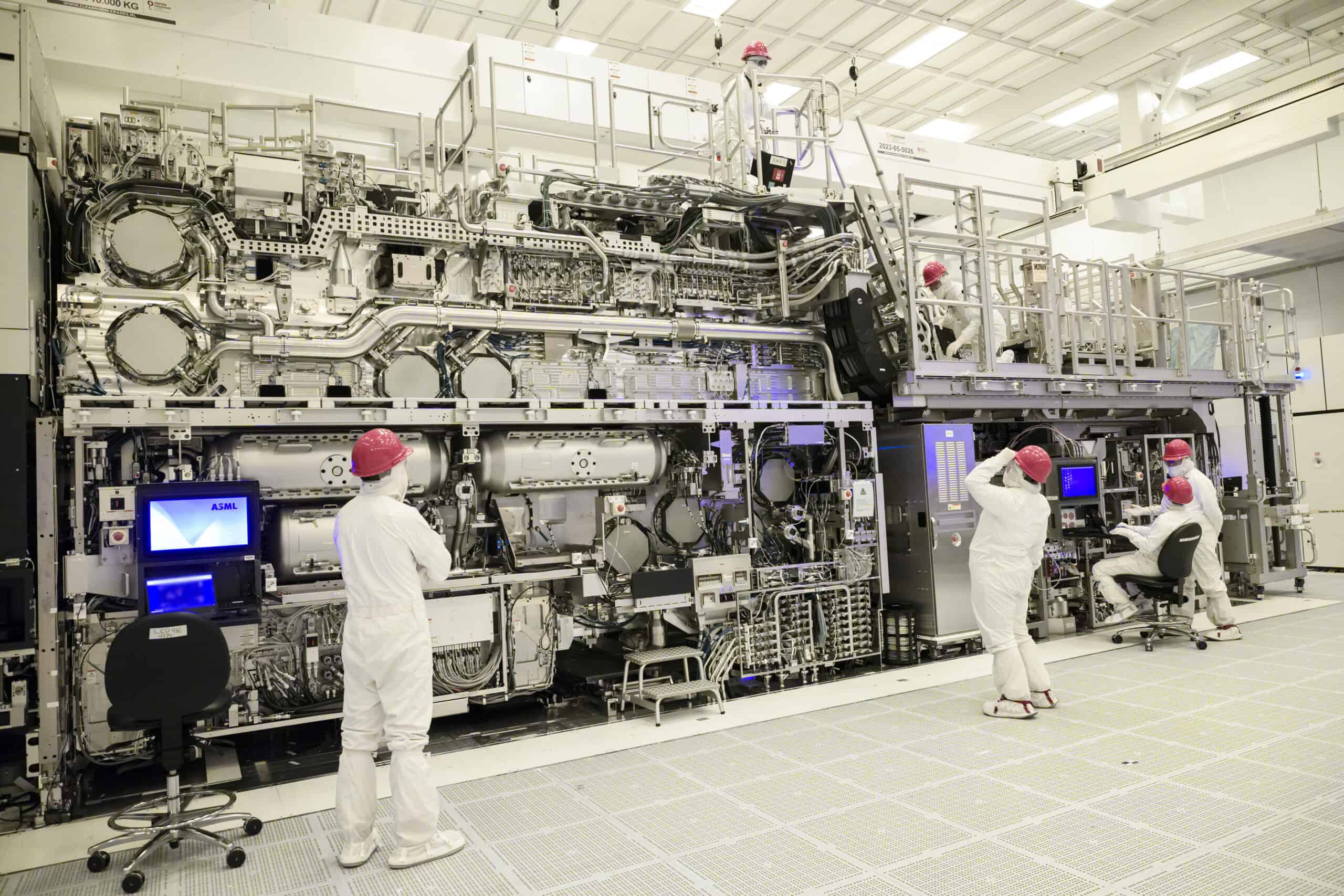

世界最大のファウンドリーであるTSMCが2024年末までに、オランダASML社の次世代リソグラフィ装置「High NA EUV」を導入することが明らかになった。Nikkei Asiaの報道によると、1台あたり3.5億ドル(約520億円)という巨額投資となる同装置は、TSMCの新竹にある研究開発センターに設置される予定である。この動きは、次世代半導体製造技術の開発競争が新たな段階に入ったことを示すものだ。

革新的技術がもたらす製造プロセスの進化

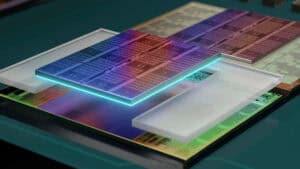

ASMLが開発したHigh NA EUV装置「Twinscan EXE:5000」は、半導体製造技術の革新的な進歩を象徴する製品である。8nmの高精細な解像度と13.5nmのEUV光波長を実現した本装置により、チップメーカーは従来比で最大2.9倍のトランジスタ密度を達成することが可能となる。この飛躍的な性能向上は、より高性能なプロセッサーやAIチップの開発を可能にし、次世代のコンピューティング技術の基盤となることが期待されている。

High NA EUV装置の導入を巡っては、すでに世界的な競争が始まっている。Intelは2024年に入って早々にオレゴン州の施設で1号機を稼働させ、第2四半期には2号機の導入も完了させた。ASMLによれば、3号機は現在「別の主要顧客」向けに出荷中であり、さらにSamsung Electronicsも2025年第1四半期までの導入を計画している。各社の積極的な投資は、半導体製造技術における主導権争いの激化を如実に示している。

TSMCの野心的な技術開発ロードマップ

TSMCは本装置を、次世代製造プロセスである1.4nm(A14)の開発に投入する計画を明らかにしている。2027年の量産開始を目標とする同プロセスは、現在開発中の2nmノードから約2世代先を行く最先端技術となる。特にAI関連製品の需要増加を見据え、High NA EUV装置の導入によって競争力を一層強化する狙いがある。この投資判断は、TSMCの長期的な技術優位性維持への強い決意を示すものといえる。

しかし、High NA EUV装置の導入には複数の技術的ハードルが存在する。従来のEUV装置と比較して撮像視野が小さくなることから、チップ設計の大幅な見直しが必要となる。また、装置自体の大型化に伴い、既存の製造ラインの再編成や、場合によっては新工場の建設も検討しなければならない。これらの課題に対する解決策の確立が、実際の量産化への重要な鍵を握っている。

Xenospectrum’s Take

半導体産業は今、重要な転換点を迎えている。High NA EUV装置の導入は、単なる製造技術の進化にとどまらず、グローバルな半導体サプライチェーンの再編にも大きな影響を与える可能性がある。ASMLの年間生産能力が5-6台程度に限られる中、早期の装置確保は各社の将来的な競争力を左右する重要な要素となっている。

1台3.5億ドルという投資規模は、半導体製造における参入障壁の高さを改めて示すものであり、この産業における寡占化がさらに進む可能性も示唆している。特に中国企業が国際的な規制によってASMLの最新技術にアクセスできない状況は、グローバルな技術格差をさらに広げる要因となるだろう。

今後は、巨額投資に見合う製品展開戦略や、効率的な装置活用による投資回収が各社の重要な経営課題となる。特にAI関連製品の需要拡大を見据えた製造能力の確保は、市場での優位性維持に直結する重要な要素となるだろう。TSMCの今回の投資判断は、こうした産業構造の変化を見据えた戦略的な一手として評価できる。次世代半導体製造技術の本格的な実用化に向けて、業界の動向から目が離せない状況が続くことになりそうだ。

Source

コメント