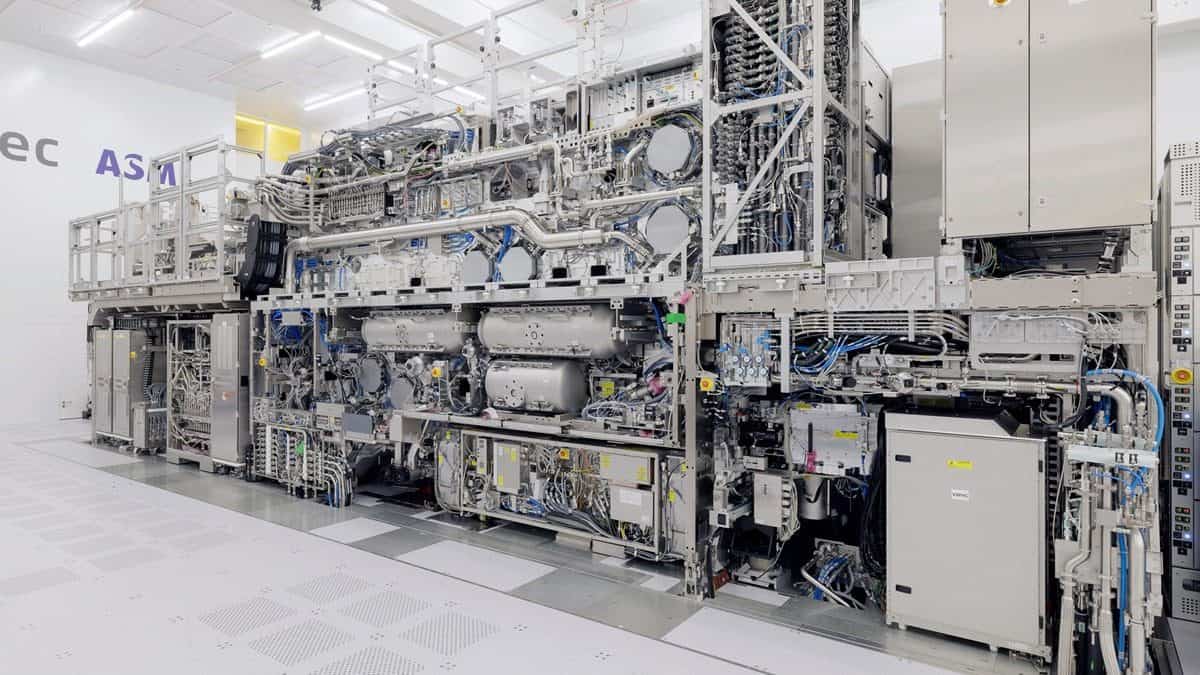

オランダの半導体製造装置メーカーASMLは、米・大手チップメーカーIntelに続き、2台目のHigh-NA EUVリソグラフィ装置を別の顧客に出荷開始したと発表した。なお、顧客の名前は明らかにされていない。

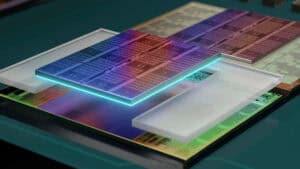

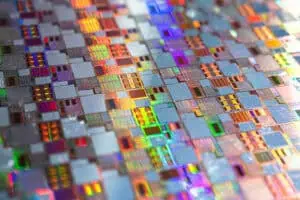

ASMLのHigh-NA EUVリソグラフィ装置は、現在TSMCやSamsungなどで利用されているLow-NA EUVリソグラフィ装置で可能なものよりも、さらに高密度なチップの製造を可能にする物だ。今回のReutersの報道は、次世代の半導体製造に繋がる最新技術が徐々に採用されつつあることを示唆する物だろう。

ASMLの最高経営責任者(CEO)であるChristophe Fouquet氏は、同社の決算説明会で、「High-NA、すなわち0.55 NA EUVに関しては、最初のシステムを顧客に出荷し、このシステムは現在設置中です。今月、2番目のシステムの出荷を開始し、その設置も始まろうとしています」と、述べている。

ASMLは、最初のHigh-NA EUVリソツールであるTwinscan EXE:5000を2023年末にIntelに出荷し始めた。2024年初頭にはオレゴン州ヒルズボロにあるIntelの施設に設置されている。Intelは、これによって最先端装置を駆使することを学び、次世代Intel 14AノードにおいてHigh-NA EUVリソグラフィ装置を量産に投入する予定である。High-NA EUVベースのプロセス技術に早期に着手することで、Intelは他社に先んじることが出来るだろう。

ASMLはHigh-NA EUVリソグラフィ装置を購入した企業の名前を伏せており、どこであるかは推測の域を出ないが、ReutersはIntel、TSMC、Samsungが明らかな候補であると指摘している。TSMCとSamsungは既に、ASMLのHigh-NA技術の採用を希望していることを確認している。

しかし、最先端ハードウェアを受け取る可能性があるのは、半導体トップ3社だけではない。12月には、IBMやMicronを含む企業が運営する予定の半導体施設が、ASMLのHigh NA EUVマシンを1台導入すると噂されており、これが史上2台目の導入となる可能性もある。

「このシステムは、当社のロジックおよびメモリの両顧客が、ロードマップにHigh-NAを挿入する準備をするのに役立つため、当社の[High-NA]システムラボに対する顧客の関心は高いです。0.33NAと比較して、0.55NAのシステムはより微細な解像度を提供し、サブ2nmロジックおよびサブ10nm DRAMノードをサポートするために、同等の生産性でトランジスタ密度をほぼ3倍向上させることができます」と、Fouque氏は述べている。

ASMLは更に開口数0.7を超える投影光学系を備えたHyper-NA EUVリソグラフィ装置の開発も模索しているようだ。

Source

コメント