Intelが次世代プロセス「Intel 18A」の詳細を、半導体技術の国際会議「VLSI Symposium 2025」で発表した。革新的なトランジスタ構造「RibbonFET」と裏面電力供給技術「PowerVia」を導入し、現行のIntel 3プロセスと比較して30%以上の密度向上とフルノードに相当する性能改善を達成したという。

Intel 18Aとは:次世代を切り拓く革新技術

Intel 18Aは、Intelが「5ノード4年計画 (5N4Y)」の最終目標として掲げる最先端プロセス技術だ。オングストローム(Å、1Å = 0.1nm)時代を見据えたこのプロセスは、ムーアの法則の継続に挑戦するIntelの意気込みを示すものであり、その核心には、RibbonFETとPowerViaという2つのブレークスルー技術が存在する。

RibbonFET (GAA):トランジスタ構造の新たな地平

Intel 18Aで採用される「RibbonFET」は、Gate-All-Around (GAA) と呼ばれるトランジスタ構造の一種である。従来のFinFET構造では、ゲートはチャネルの3面を囲んでいたが、RibbonFETではゲートが電流の流れるチャネル(リボン状のナノシート)の周囲4面すべてを完全に囲む構造となる。

これにより、ゲートによる電流制御能力が大幅に向上し、同じ駆動電流をより低い電圧で実現できる、あるいは同じ電圧でより多くの電流を流すことが可能になる。結果として、トランジスタの高速化と低消費電力化に大きく貢献する。また、リーク電流(待機時に漏れ出す電流)の抑制にも効果があり、電力効率の改善にも繋がる。これは、微細化が進むにつれて顕著になる課題への重要な解答だ。

PowerVia (BSPDN):電力供給の常識を変える裏面配線

もう一つの柱である「PowerVia」は、Intel独自の裏面電力供給ネットワーク (BSPDN: Backside Power Delivery Network) 技術である。従来の半導体チップでは、トランジスタへの電力供給線と信号線の両方がウェハーの表面(前面)に多層構造で形成されていた。微細化が進むにつれて、これらの配線は非常に複雑化・高密度化し、信号遅延や電力損失(IRドロップ)、配線間の干渉といった問題を引き起こしていた。

PowerViaは、電力供給専用の配線をウェハーの裏面に形成し、トランジスタに直接電力を供給する画期的なアプローチである。これにより、前面の配線層は信号線専用となり、配線の混雑が大幅に緩和される。信号線はより最適な経路で配線でき、信号遅延の短縮やクロストーク(信号干渉)の低減が期待できる。

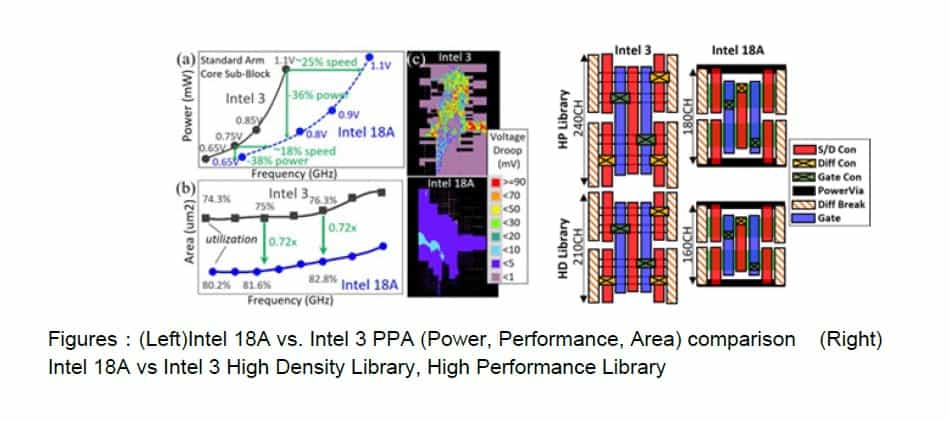

電力線が裏面に移動することで、電力供給経路も短縮・最適化され、IRドロップを抑制し、より安定した電力供給が可能となる。これは特に高性能コンピューティング (HPC) など、大量の電力を消費するアプリケーションにおいて大きなメリットとなる。VLSI Symposium 2025で示された資料には、Intel 18Aにおける電圧降下(Voltage Droop)がIntel 3と比較して大幅に改善されている様子が示されており、PowerViaの効果を裏付けている。

Intel 3からの飛躍的な性能向上:PPAと密度の進化

VLSI Symposium 2025で発表されたデータは、Intel 18AがIntel 3から著しい進化を遂げていることを示している。

PPA (Power, Performance, Area) の大幅改善

PPAは半導体プロセスの性能を示す重要な指標だ。公開された資料によると、標準的なArmコアのサブブロックを用いた比較において、Intel 18AはIntel 3に対して以下の改善を達成している。

- 性能: 同じ1.1Vの電圧で動作させた場合、約25%の速度向上を実現。あるいは、同じ性能であれば、より低い電圧で動作可能であることを示唆する。

- 電力: 同じ1.1Vの電圧で動作させた場合、消費電力を約36%削減。電力効率の大幅な向上を示す結果である。

- エリア: グラフからは、周波数向上に伴うエリア効率(Utilization)もIntel 18AがIntel 3を上回っており、より小さな面積で高い性能を発揮できる可能性を示している (0.72xの面積で同等の周波数を達成、あるいは同面積でより高い周波数を達成)。

これらの結果は、RibbonFETによるトランジスタ性能の向上と、PowerViaによる電力供給効率の改善が複合的に作用した結果と考えられる。特に「フルノードの性能向上」という表現は、単なるマイナーチェンジではなく、プロセス世代として明確な進歩があったことを示している。

30%超の密度スケーリング

Intel 18Aは、Intel 3と比較して30%以上の密度スケーリング(集積度の向上)を達成している。これは、RibbonFETによるトランジスタ自体の微細化に加え、PowerViaによって前面配線層のスペースに余裕が生まれたことも貢献していると考えられる。

VLSI Symposium 2025の資料(上図(右))に示されたセルライブラリの比較図を見ると、Intel 18AではIntel 3よりもセルの高さが低く抑えられていることがわかる。特に高性能(HP)ライブラリでは240CHから210CHへ、高密度(HD)ライブラリでは80CHから70CHへと縮小されている。これは、電力線を裏面に移設したことで前面の配線に必要なスペースが削減され、より小さな標準セルを設計できるようになったためだ。結果として、同じ面積により多くのトランジスタを集積することが可能となり、チップ全体のコスト削減や機能向上に繋がる。

設計容易性とライブラリ

Intelは18Aプロセス向けに、高性能(HP)と高密度(HD)の両方のライブラリを提供し、幅広い用途に対応する。さらに、これらのライブラリは「フル機能の技術設計能力」と「強化された設計容易性」を提供するとされている。これは、PowerViaのような新しい技術を導入しつつも、チップ設計者が比較的容易に設計作業を行えるような配慮がなされていることを示唆しており、エコシステムの拡大にとって重要な要素となる。

業界内での位置づけと今後の展望

Intel 18Aは、Intel自身がCPUなどの製品に採用するだけでなく、外部企業に半導体製造サービスを提供するIntel Foundry Services (IFS) の主力プロセスとしても期待されている。

Wccftechの記事によると、Intel 18AのSRAMセル密度は、競合であるTSMCのN2プロセスに匹敵するレベルにあると報じられている。これは、Intelがプロセス技術において競合他社と同等か、分野によってはリードする可能性を示唆するものであり、半導体業界の勢力図に影響を与える可能性がある。ただし、これはSRAM密度に関する比較であり、プロセス全体の総合的な優劣を示すものではない点には注意が必要である。

Intel 18Aを採用する最初の製品としては、コンシューマ向けCPU「Panther Lake」やサーバー向けCPU「Clearwater Forest」が計画されている。これらの製品が市場に登場することで、Intel 18Aの真価が問われることになるだろう。外部顧客向けの製造に関しては、歩留まり率の安定化と量産体制の確立が鍵となるが、順調に進めば2026年頃から18Aを採用した製品が登場する可能性も報じられている。

Intel 18Aは、RibbonFETとPowerViaという野心的な技術を採用することで、性能、電力効率、密度のすべてにおいて大きな飛躍を遂げようとしている。VLSI Symposium 2025で示されたデータは、そのポテンシャルの高さを裏付けるものだ。今後の量産化の進捗と、実際の製品におけるパフォーマンスに大きな注目が集まる。Intelが再び半導体製造の頂点に返り咲くための、重要な試金石となるプロセスであることは間違いない。

Sources

- VLSI Symposium 2025: Technical Highlights from the 2025 Symposium On VLSI Technology and Circuits [PDF]