AMDが新しい「マルチチップ積層」技術に関する特許を出願し、次世代Ryzen SoCに向けた新たな道筋が明らかになった。この革新的な手法では、大型ダイの下に小型チップレットを重ねて配置することで、ダイ面積の効率的な活用と性能向上を同時に実現する。

3D V-Cacheを更に発展させたチップ重ね合わせ技術

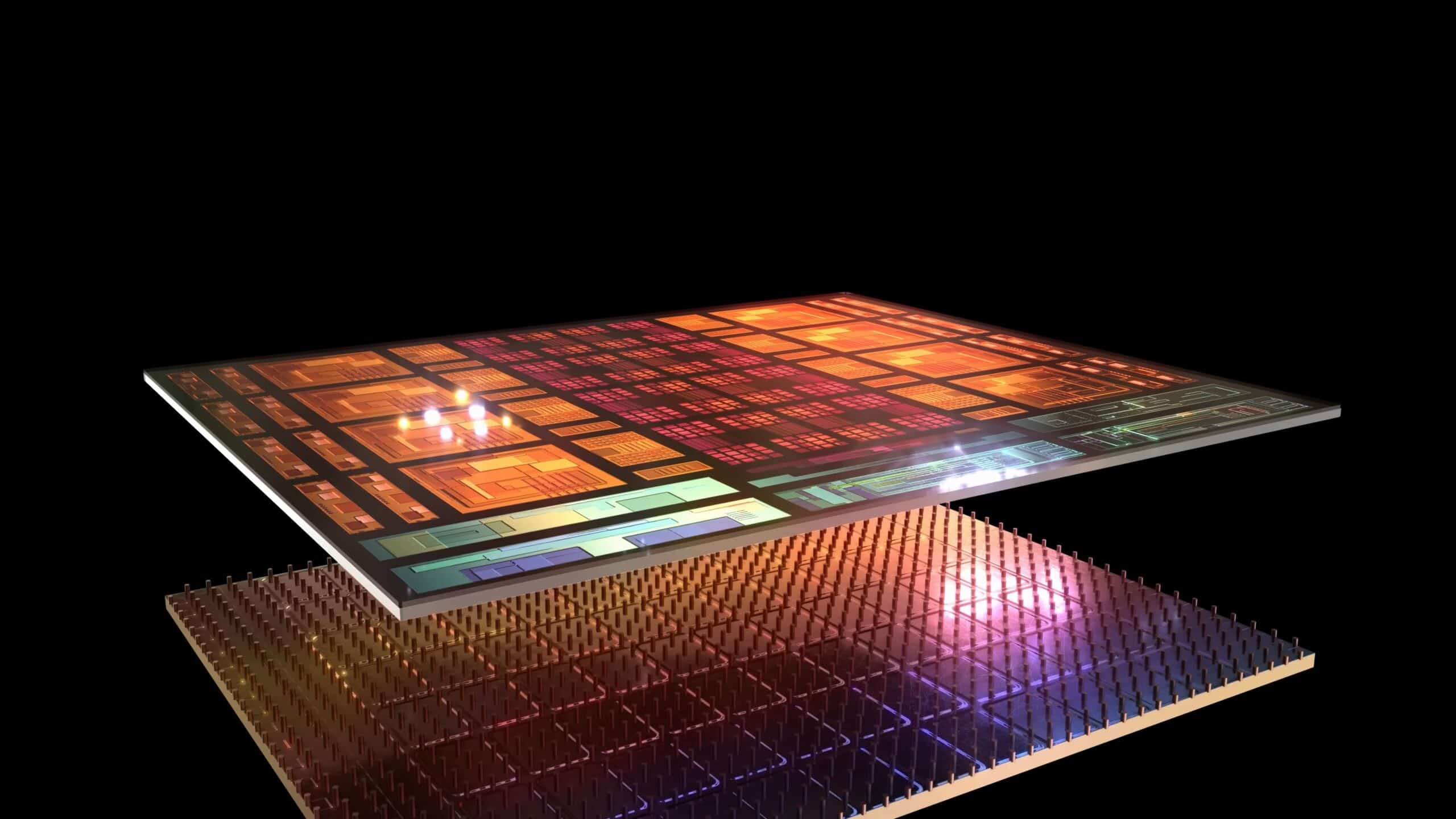

AMDが出願した特許で提案された新しいパッケージング設計は、従来のチップレット技術を大きく進化させるものである。この設計の核心は、大型のメインダイの下に小型のチップレットを部分的に重ねて配置する「オーバーラップ方式」にある。従来の水平方向のチップレット配置や単純な垂直積層とは異なり、この手法では接触面積を最大限に活用しながら、同一パッケージ内により多くの機能を統合することが可能となる。

この技術革新の重要性は、既存のダイサイズを維持したまま、プロセッサーの性能を飛躍的に向上できる点にある。具体的には、より多くのCPUコア、大容量のキャッシュメモリ、そして広帯域なメモリインターフェースを同一パッケージ内に実装できるようになる。これはAMDが3D V-Cache技術でX3Dプロセッサーに採用している垂直積層技術を更に発展させたものと位置付けられる。

チップレットの重ね合わせ方式には、もう一つ重要な技術的利点がある。それは相互接続における信号伝達距離の短縮である。チップレット間の物理的な距離が縮まることで、データ転送の遅延時間が大幅に削減され、プロセッサー全体の応答性が向上する。さらに、各チップレットが独立して電力制御可能な設計となっているため、使用していない部分の電力を効率的にカットすることができ、全体的な消費電力の最適化にも貢献する。この設計思想は、AMDが長年追求してきた高性能と電力効率の両立という目標に完全に合致している。

これはAMDが単一のモノリシック設計から複数のチップレットを組み合わせる設計へと移行を進めている証拠であり、既にGPUにおいても同様のマルチチップレットアプローチを模索していることが報告されている。

Xenospectrum’s Take

AMDの新特許は、半導体業界における「より小さく、より速く」という永遠の命題に対する興味深いアプローチを示している。Intelとの競争が激化する中、チップレットベースの設計を洗練させることで、AMDは製造コストと性能のバランスを巧みに取ろうとしている。しかし、この技術を量産化する際の歩留まりと熱設計の課題は依然として残されており、これらをいかに克服するかが今後の成否を分けるだろう。皮肉なことに、かつて「グルー」と揶揄されたチップレット設計が、今や業界の主流となりつつあるのは興味深い展開だ。

Source

コメント