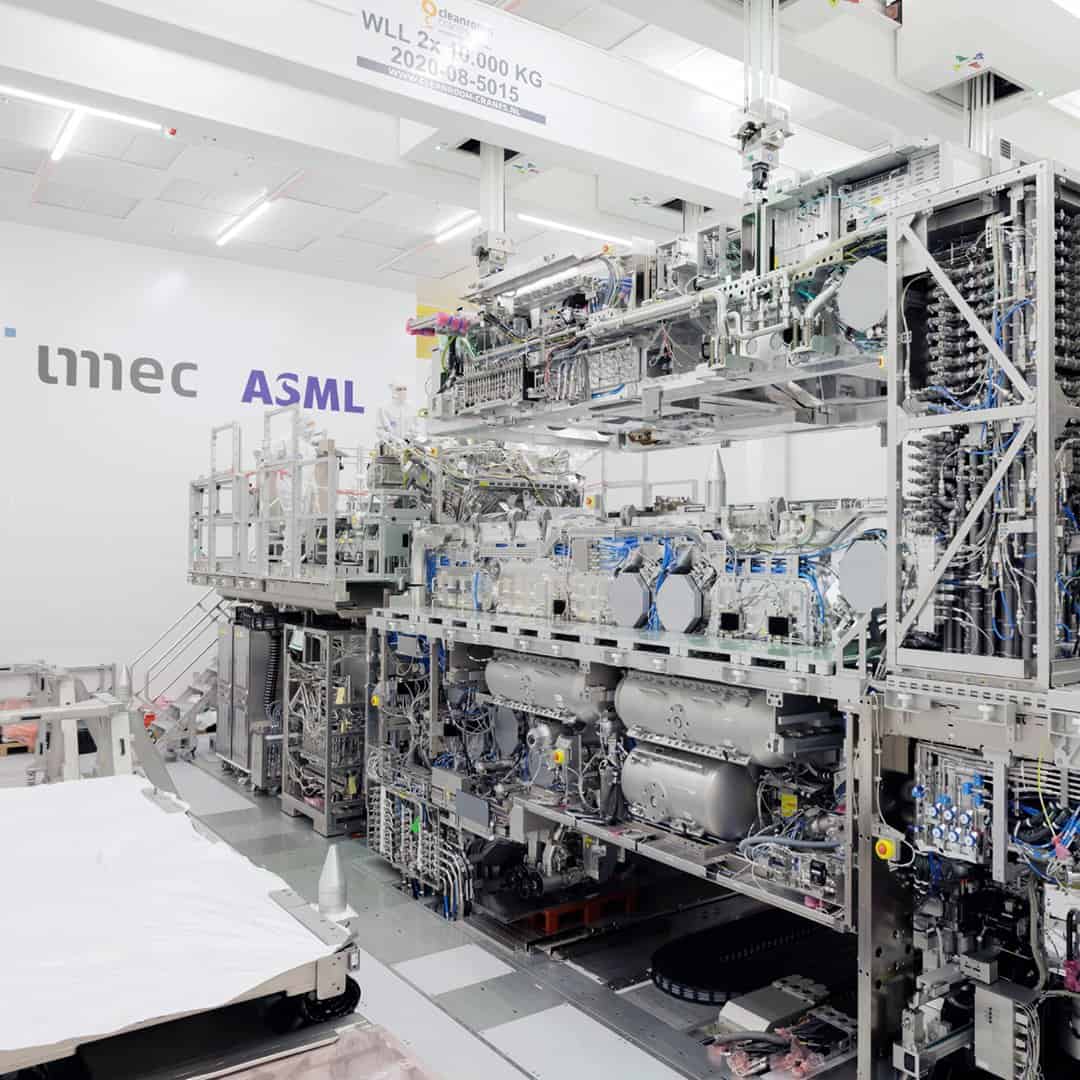

ベルギーの研究機関imecとオランダのASMLは、次世代の半導体製造技術において重要な一歩を踏み出した。imecは、ASMLの最新のHigh-NA (高開口数) EUV (極端紫外線) リソグラフィ装置を用いて、業界初となるロジックおよびDRAMトランジスタのパターン化に成功したと発表した。この成果は、ナノメートルからさらに小さいオングストローム時代の幕開けと言えるだろう。

High-NA EUVリソグラフィがもたらす微細化の飛躍

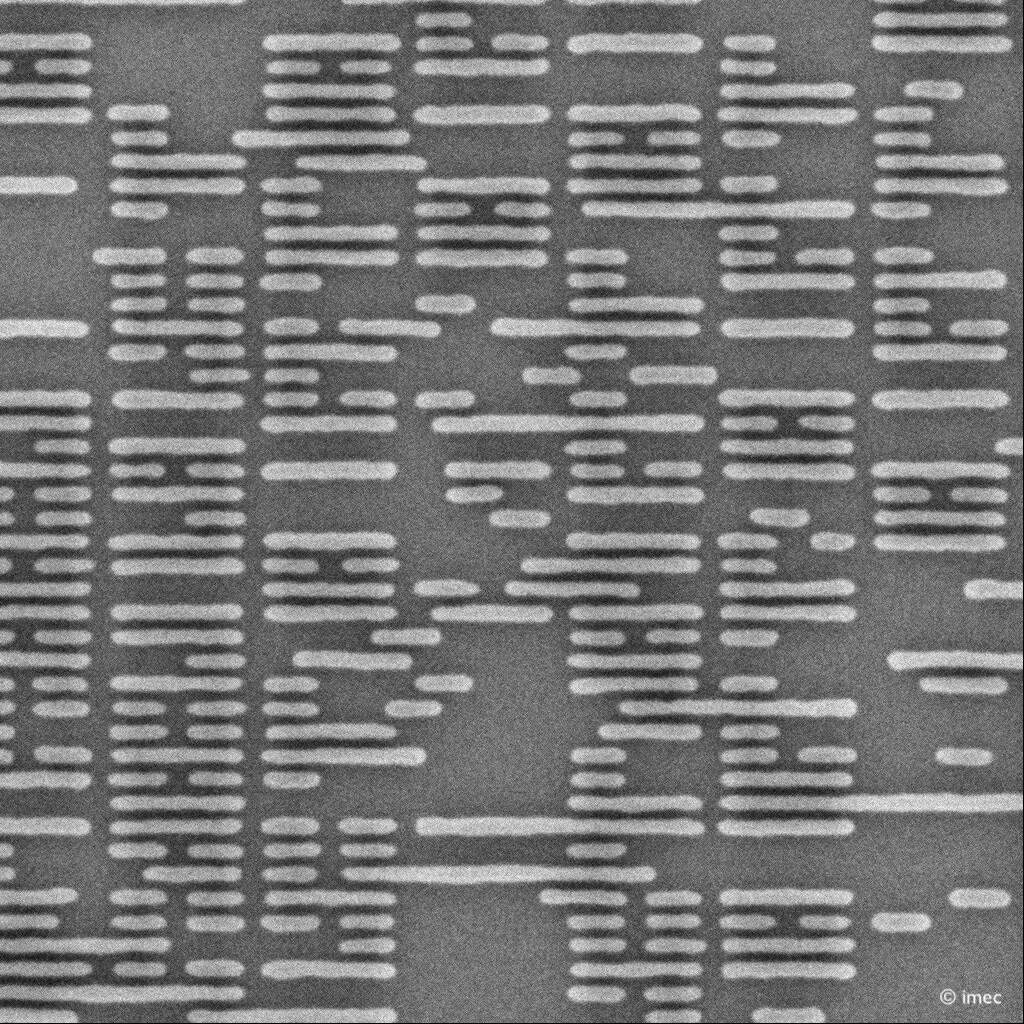

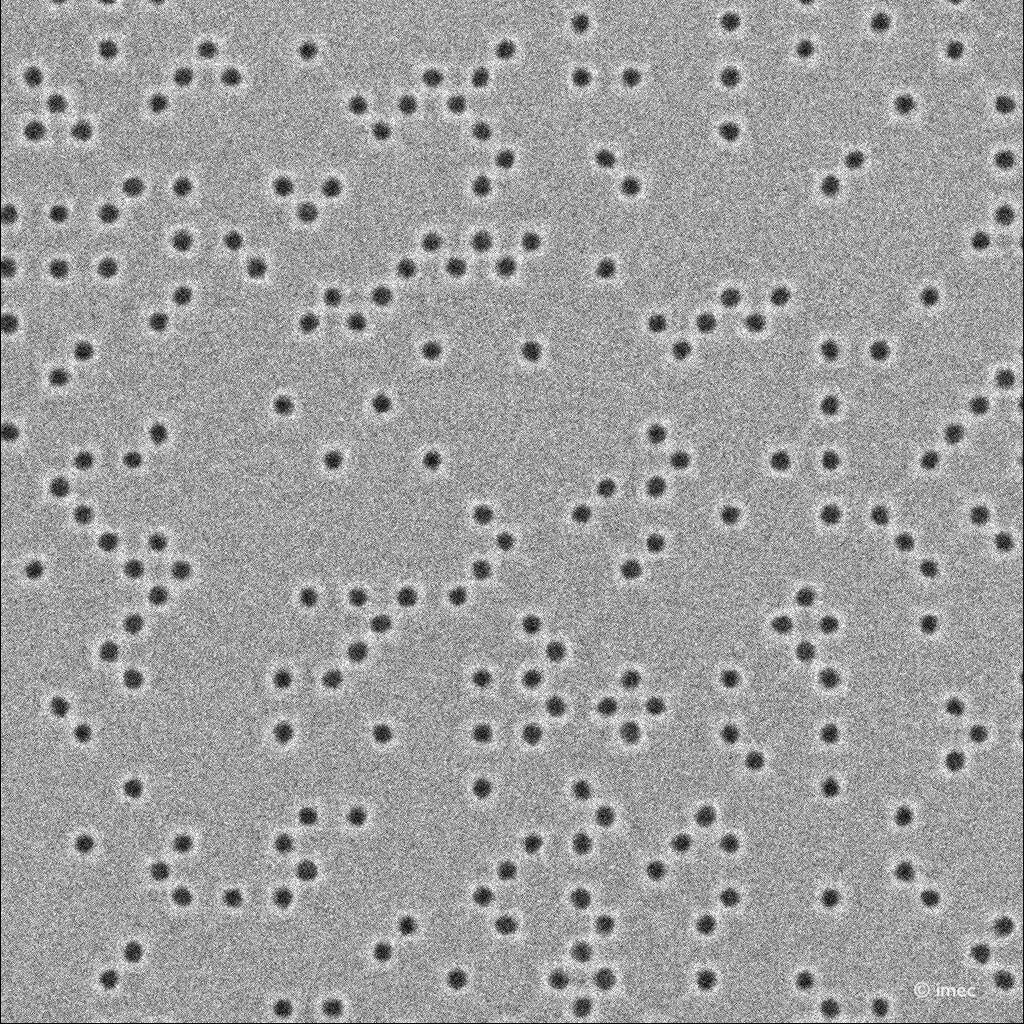

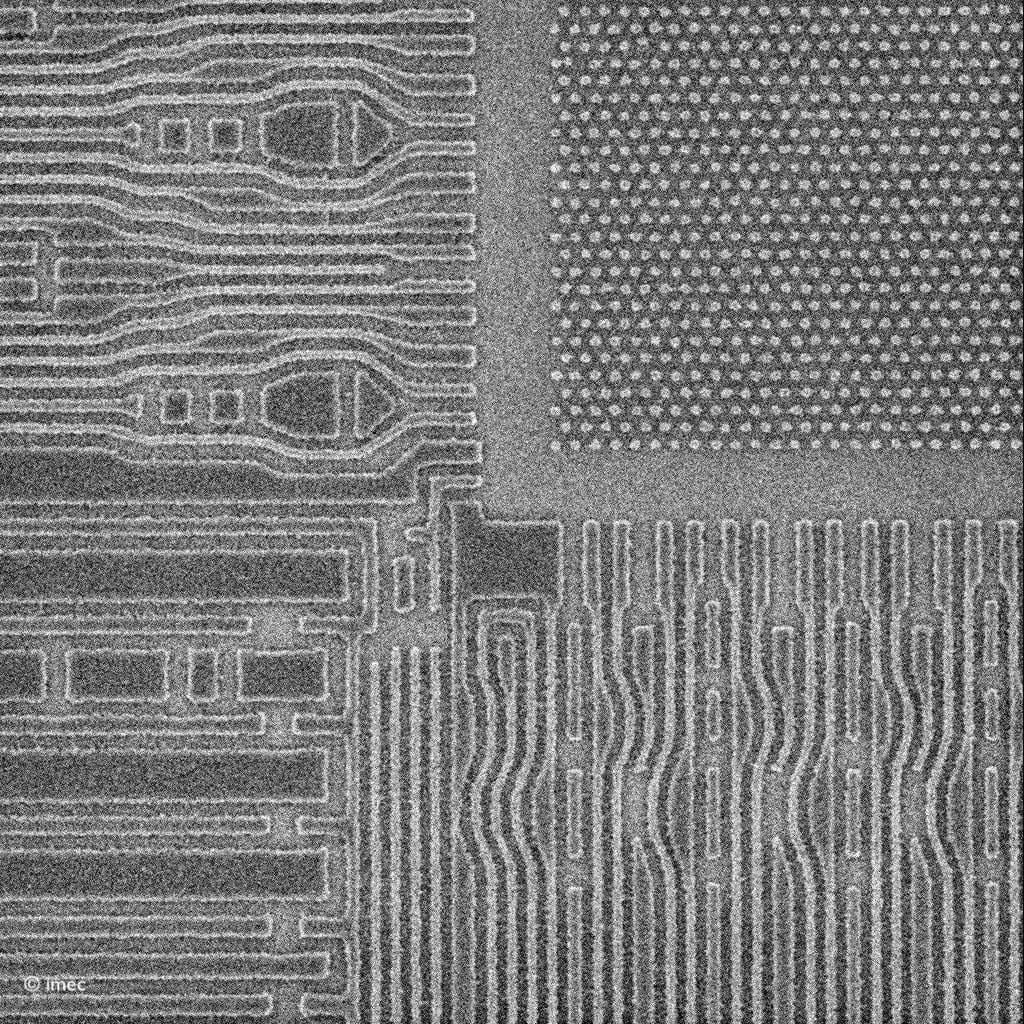

imecの研究チームは、ASMLのTwinscan EXE:5000 EUVリソグラフィ装置を駆使し、これまでにない微細構造の形成に成功した。具体的には、9.5nmの密集した金属配線(19nmピッチ)を持つランダムロジック構造の形成や、30nmの中心間距離を持つランダムビアのパターン化を実現した。

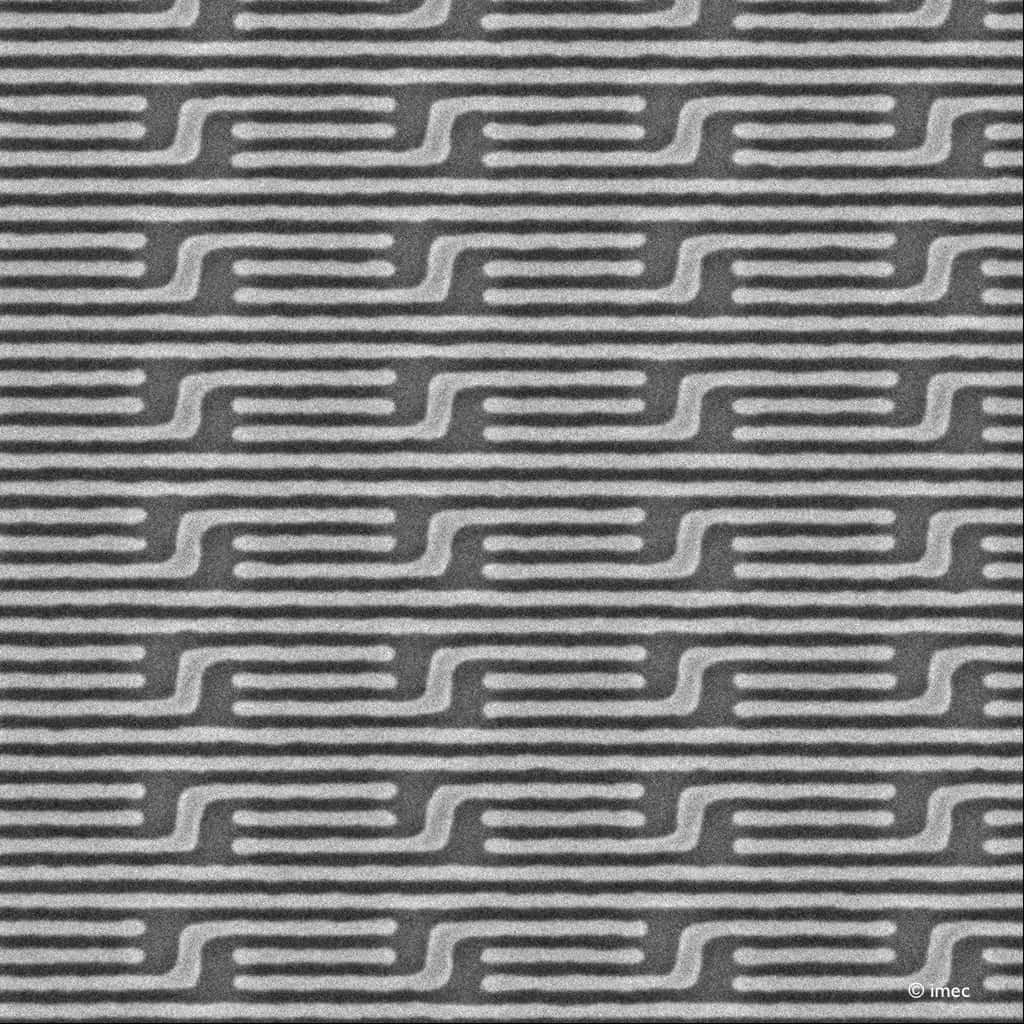

さらに、22nmピッチの2Dフィーチャーの形成にも成功し、DRAMの専用レイアウトを32nmピッチで単一露光により形成することにも成功している。

これらの成果は、現行のLow-NA EUV装置と比較して、解像度を13nmから9.5nmへと大幅に向上させたことを意味する。この技術的進歩により、半導体チップの性能向上と省電力化が飛躍的に進むことが期待されている。

imecの社長兼CEOであるLuc Van den hove氏は、この成果の重要性を強調している。同氏によれば、High NA EUVリソグラフィは単一露光で20nmピッチ未満のメタル層を形成できることが実証され、ロジックおよびメモリ技術の寸法スケーリングを継続するための重要な役割を果たすという。さらに、この技術が半導体産業のロードマップを「オングストローム時代」へと押し進める重要な柱の一つになると述べている。

一方で、imecのSteven Scheer氏は、High NA EUV技術が単一露光で積極的にスケーリングされた2D特徴の形成を可能にし、設計の柔軟性を向上させるとともに、パターニングのコストと複雑さを軽減する可能性があると指摘している。これは、半導体製造プロセスの効率化と経済性の向上につながる重要な要素となる。

High-NA EUV技術の実用化に向けて、imecとASMLは共同でHigh NA EUVリソグラフィラボをオランダのフェルトホーフェンに設立した。このラボは、半導体メーカーが新技術にアクセスし、自社の設計ルールやレイアウトに基づいたHigh NA EUVの使用例を開発できる環境を提供している。

実際に、Intelは既に2台のHigh-NA EUV装置を受け取っており、2025年頃のデビューを目指して開発を進めている。また、TSMCも1台の装置を保有していると噂されているが、同社は2023年の時点で、次世代の1.6nmチップ(A16プロセス)の製造にはHigh-NA EUV技術を必要としないと述べている。

しかし、GartnerのアナリストAlan Priestley氏は、この発表を進捗状況の更新と位置づけ、実際の量産への適用にはまだ時間がかかると指摘している。Priestley氏は、TSMCやIntelなどの主要半導体メーカーがこの技術をどのように採用し、特定のプロセスノードで使用するかが、今後注目すべき点だと述べている。

High-NA EUV技術の実用化には、3億5000万ユーロ(約560億円)という高額な装置コストや、関連する材料・プロセスの最適化など、まだ多くの課題が残されている。しかし、imecとASMLの今回の成果は、半導体産業が新たな技術的限界に挑戦し続けていることを示す重要な一歩であり、次世代の高性能コンピューティングや人工知能、5G通信などの発展を支える基盤技術となる可能性を秘めている。

Source

コメント