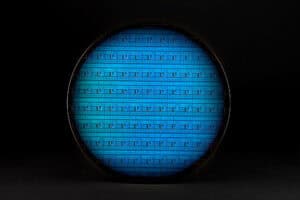

JEDECは、AMDとNVIDIAの両社が参加する次世代グラフィックスメモリ規格「GDDR7」の仕様を正式に発表した。

GDDR7ではGDDR6Xの2倍の転送速度を実現

Samsungはすでに昨年、グラフィックスカード向けの次期標準メモリと、チップあたり最大37Gbpsの高帯域幅について発表している。しかし、JEDEC標準規格の発行は重要なマイルストーンであり、GDDR7ソリューションの一般への普及と利用が間近に迫っていることを示唆するものだ。

GDDR7では、メモリ帯域幅の大幅な向上を実現する。具体的には、JEDECの仕様では、最終的にデバイスあたり192GB/秒に達する予定だ。これは、現在最速のGDDR6Xの2倍である48Gbpsのメモリ速度に相当する。しかし、この速度に到達するには、現在のメモリ・ソリューションとはとは異なる方法をとる必要が出てくるのだ。

具体的には、パルス振幅変調(PAM)に変更が加えられる。現在、GDDR6XではPAM4が使用されているが、次世代GDDR7ではPAM3が採用される。PAM4では伝送する信号を4つの電圧レベル(00、01、10、11)で規定しているが、PAM3では信号を3つ(+1、0、-1)に変調しなければならない。しかし、これによって高クロック・レートでも有効な信号を読み出しやすくなり、S/N比が有利になる。PAM4を使用すると、例えば2つの状態(0と1)を持つNRZに比べて、1クロックあたり2倍のデータを送信できる。PAM3はその中間で、1サイクルあたりの情報量が50%多い事になる。

また、GDDR7は、クロックレートを1.75GHz(実効7GHz)とし、メモリチップをアドレス指定できるメモリチャネル数がGDDR6の2チャネルから4チャネルに倍増することで、より高い帯域幅を実現している。ただし、GDDR7チップを2つのチャネルでアドレス指定することは可能だ。

もちろん、GPUのメモリコントローラとGDDR7チップの配線は、それに応じて設計されなければならない。したがって、GPU メーカーとしては、GDDR7 にクアッドチャネルモードが必要かどうかを判断することが出来る。ただし、メモリチャネル数が半分になると、同じクロックレートでメモリ帯域幅が半分になる。

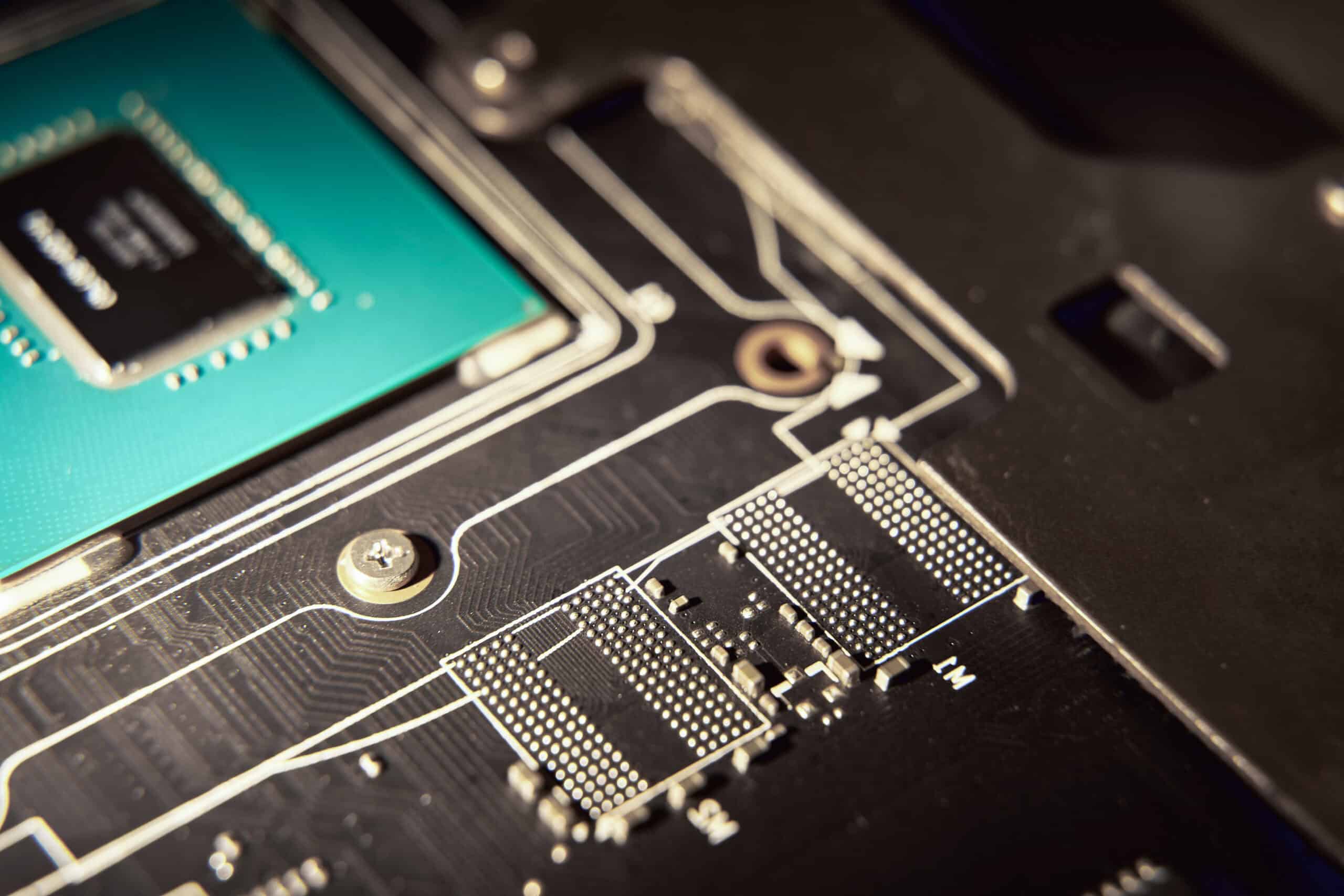

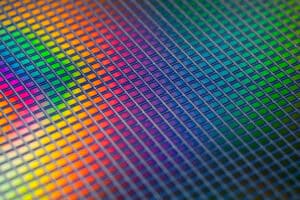

GDDR7は当初、チップあたり2GB、3GB、4GBの容量で提供される。これらの容量に対応する仕様はすでに公開されている。将来的には、チップあたり6GBと8GBも計画されている。 GDDR7チップの動作電圧は1.1Vまたは1.2Vとなる。チップ・パッケージのサイズは12 x 14 mmで、高さは1 mmだ。ボール・パッチは0.75、X/Y方向では0.73である。寸法はGDDR6とほぼ同等か、あるいは同一となる。

その他の高度な機能としては、以下の項目があげられている。

その他の高度な機能は以下の通り:

- アイマスキングとエラーカウンターを備えたコア独立LFSR(リニアフィードバックシフトレジスタ)トレーニングパターンにより、トレーニング時間を短縮しながらトレーニング精度を向上。

- システム容量を倍増させる2チャネル・モードのサポートを含む、16Gビットから32Gビットの密度をサポート。

- リアルタイム・レポート機能付きオン・ダイECC(ODECC)、データ・ポイズン、エラー・チェックおよびスクラブ、コマンド・ブロッキング(CAPARBLK)付きコマンド・アドレス・パリティを含む最新のデータ・インテグリティ機能を組み込むことにより、RAS(信頼性、可用性、保守性)に対する市場のニーズに対応。

GDDR7メモリがいつ、どのカードで初めて使用されるかは現時点では不明だ。

NVIDIAの次世代Blackwellアーキテクチャは、発売時にGDDR7を採用すると予想されている。Blackwellのデータセンター・バージョンは2024年後半に登場する可能性が高いが、その場合はGDDR7の代わりにHBM3Eメモリが使用される。コンシューマーレベルの製品は2025年初頭に登場する可能性が高く、通常通り、これらのパーツのプロフェッショナル版とデータセンター版が存在することになる。AMDもRDNA 4に取り組んでおり、こちらもGDDR7を採用すると予想されるが、両社の低価格帯パーツがコスト上の理由からGDDR6にこだわる可能性もある。

AMDにせよNVIDIAにせよ、GDDR7を最高速度で使用すれば、現在最も広帯域の384ビット・インターフェイスを使用して、最大2,304GB/秒の帯域幅を実現できる可能性がある。ただし、仕様上の帯域幅を実際に見ることができるかどうかはまた別の話だ。例えば、GDDR6Xを搭載したNVIDIAのRTX 40シリーズGPUは、いずれもわずかに低いクロックを使用しており、仕様上の上限には達していない。それでも、今後登場するアーキテクチャーを使えば、帯域幅が2倍になることは期待出来るだろう。

Sources

コメント