JEDECが第4世代高帯域幅メモリ(HBM4)の暫定仕様を発表し、次世代のAIと高性能コンピューティング向けメモリ技術の方向性が明確になった。HBM4は前世代のHBM3から大幅な性能向上を実現し、データ集約型アプリケーションの需要に応えるための仕様を備えている。

HBM4は16段スタックで最大32ギガバイトの大容量メモリーを実現する

半導体業界とメモリ業界は、関連製品の性能を新たなレベルに引き上げると期待されるメモリタイプ、HBM4に注目している。 HBMの採用率は、AIアクセラレータなど、このメモリタイプを利用した製品に対するAI市場からの需要により、この1年で大幅に急上昇した。 JEDECはついにHBM4の開発を検証し、次世代のHBM4でどのようなことが実現されるのかを垣間見せてくれている。

HBM4の最も注目すべき特徴は、スタックあたりのチャネル数がHBM3の2倍に増加したことだ。これにより、メモリの物理的なフットプリントは大きくなるものの、帯域幅と容量が大幅に向上する。JEDECの予備的仕様によると、HBM4は以下の特徴を持つ:

- メモリ層の密度:24 Gbitと32 Gbitの2種類が規定される。

- スタック構成:4段、8段、12段、16段のTSV(Through-Silicon Via)スタックをサポート。これにより、様々なアプリケーションのニーズに柔軟に対応できる。

- データ転送速度:初期の合意では最大6.4 Gbpsまでの速度ビンが指定されているが、さらに高い周波数についても議論が進行中である。

- インターフェース幅:スタックあたり2048ビットのインターフェースをサポート。これはHBM3から大幅に拡張されている。

- メモリ容量:32 Gbit層を使用した16段スタックの場合、単一のスタックで64 GBの容量を実現できる。4つのメモリモジュールを搭載したプロセッサーでは、最大256 GBのメモリと6.56 TB/sのピーク帯域幅を8,192ビットインターフェースで実現可能となる。

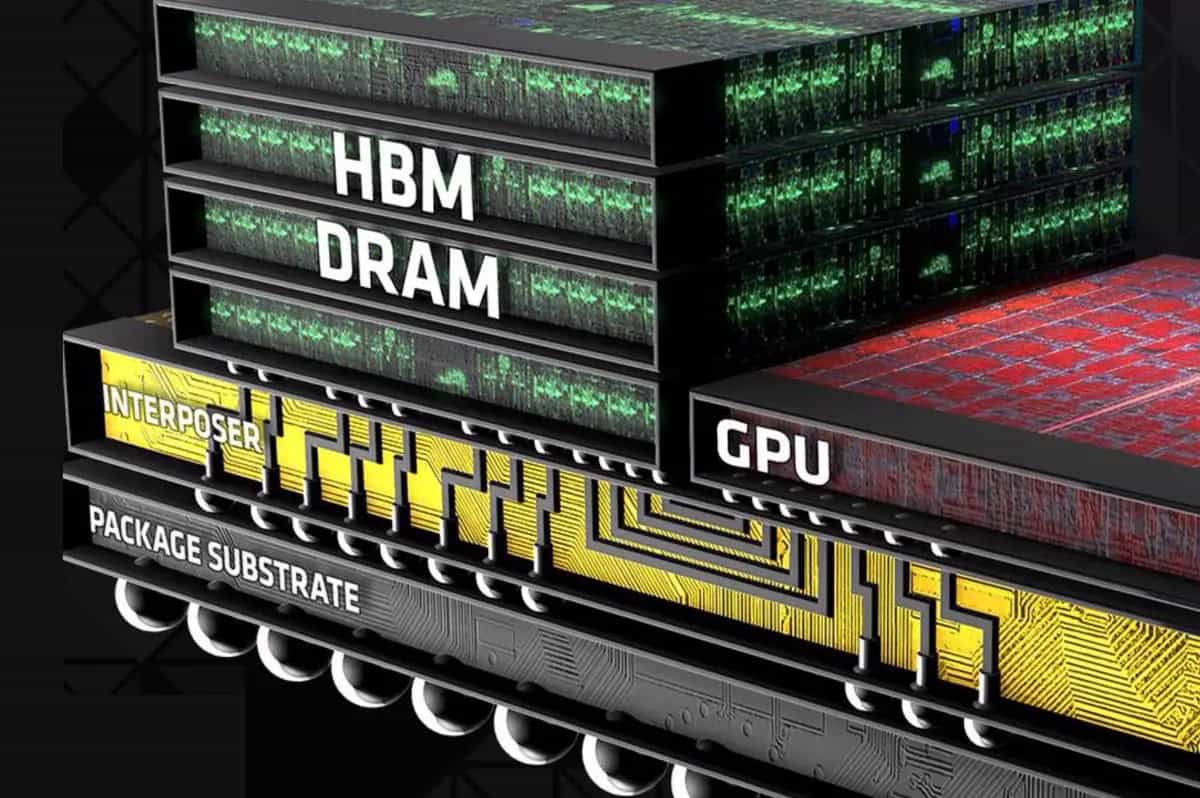

- 後方互換性:HBM4は単一のコントローラーでHBM3とHBM4の両方をサポートできるよう設計されている。ただし、異なるフットプリントに対応するために、様々なインターポーザーが必要となる。

これらの仕様により、HBM4はAI、高性能コンピューティング(HPC)、ハイエンドグラフィックス、サーバーなど、大規模なデータセットと複雑な計算を効率的に処理する必要があるアプリケーションに最適化されている。特に、生成AIの分野では、HBM4の高帯域幅と大容量メモリがモデルの学習と推論の高速化に貢献すると期待されている。

また、HBM4の開発には主要な半導体企業が関与している。SK hynixとTSMCはHBM4のベースダイ開発で協力関係にあり、TSMCは12FFC+(12nmクラス)とN5(5nmクラス)プロセス技術を使用してこれらのダイを製造する予定である。さらに、NVIDIAは次世代のRubin AIアクセラレーター向けにHBM4の採用を既に発表しており、業界全体でHBM4への期待が高まっている。

JEDECは現在、HBM4標準規格の完成に向けて作業を進めており、業界各社に標準化プロセスへの参加を呼びかけている。HBM4の登場により、次世代のコンピューティング技術が大きく前進し、AIや高性能コンピューティングの分野に新たな可能性が開かれることが期待される。

Source

コメント