NEO Semiconductorが人工知能(AI)処理の性能と効率性を大きく高める可能性を持った「3D X-AI」チップ技術を発表した。この画期的な技術は、現在の高帯域幅メモリ(HBM)チップに代わり、3D DRAM内でAI処理を可能にすることで、長年の課題であったデータバスのボトルネックを解消することを目指したものだという。

3D X-AI技術がAIチップの常識を覆す

従来のAIチップアーキテクチャの根本的な問題に、データ転送速度の問題が存在する。現在のAIチップは、データをHBMに保存し、GPUで全ての計算を行うという分離構造を採用しているが、この構造では、膨大な量のデータをHBMとGPU間で転送する必要があり、そのプロセスがパフォーマンスのボトルネックとなっていた。NEO Semiconductorの創業者兼CEOであるAndy Hsu氏は、この問題について「現在のAIチップは、アーキテクチャと技術の非効率性により、大量のパフォーマンスと電力を無駄にしています」と指摘している。

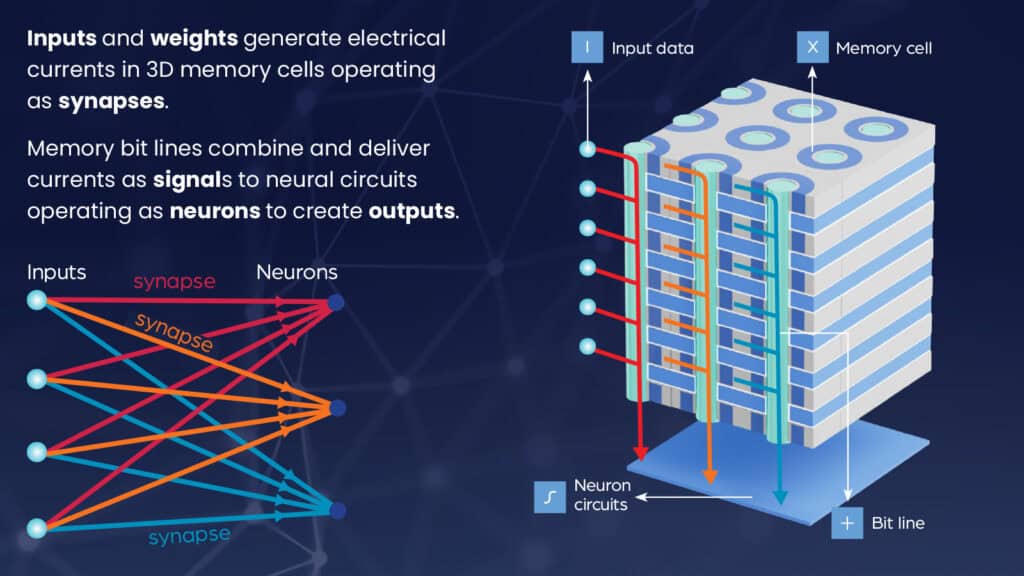

3D X-AI技術は、この課題に対して革新的なアプローチを提案している。具体的には、3D DRAM内にAI処理能力を組み込むことで、データ転送の必要性を大幅に削減する。この方式により、パフォーマンスの向上と消費電力の劇的な削減が同時に実現されるのだ。

技術の詳細を見ていくと、1つの3D X-AIダイは300層の3D DRAMセルと8,000個のニューロンを持つ1層の神経回路で構成されている。この構造により、128Gbの容量と10TB/秒という驚異的なAI処理スループットが実現される。さらに注目すべきは、12個の3D X-AIダイをHBMパッケージングで積層した場合の性能だ。NEO Semiconductorの試算によると、この構成で120TB/秒もの処理スループットが達成可能となり、これは現在の技術と比較して100倍ものパフォーマンス向上を意味する。

同時に、この技術は消費電力の面でも大きな進歩をもたらす。GPUへのデータ転送を最小限に抑えることで、データバスによる消費電力と発熱を99%も削減できるという。これは、AIシステムの運用コストと環境負荷の大幅な低減につながる重要な特徴である。

さらに、3D X-AI技術は8倍のメモリ密度を実現する。300層ものメモリ層を含むことで、より大規模で複雑なAIモデルを単一のチップに保存することが可能になる。これにより、AIアプリケーションの能力と多様性が飛躍的に向上することが期待される。

この革新的な技術の影響は、単にハードウェアの性能向上にとどまらない。Network Storage Advisors社長のJay Kramer氏は、「3D X-AI技術の応用は、新たなAIユースケースの開発を加速し、新しいイノベーションを促進するでしょう」とコメントしている。実際、この技術が実用化されれば、自然言語処理、コンピュータビジョン、自動運転など、様々な分野でAIアプリケーションの能力が劇的に向上する可能性がある。

しかし、この技術の実用化には課題も存在する。300層もの3D DRAMセルと神経回路の製造プロセスは極めて複雑であり、量産化には技術的なブレークスルーが必要となるだろう。また、既存のAIソフトウェアやフレームワークとの互換性確保も重要な課題となる。

Source

コメント