NVIDIAは、現行世代であるHopperアーキテクチャGPU「H100」と比較して最大5倍の性能向上を誇るという、次世代「Blackwell」アーキテクチャGPUと、それに基づくAIアクセラレータ「B200」GPUを正式に発表した。Blackwell GPUは、同じダイ上に2つのGPUを組み込むNVIDIA初のMCM(マルチチップモジュール)設計を採用している。

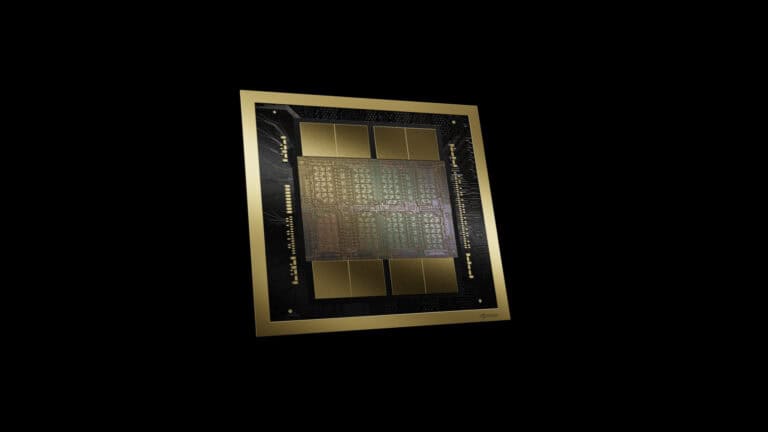

NVIDIA B200 GPU

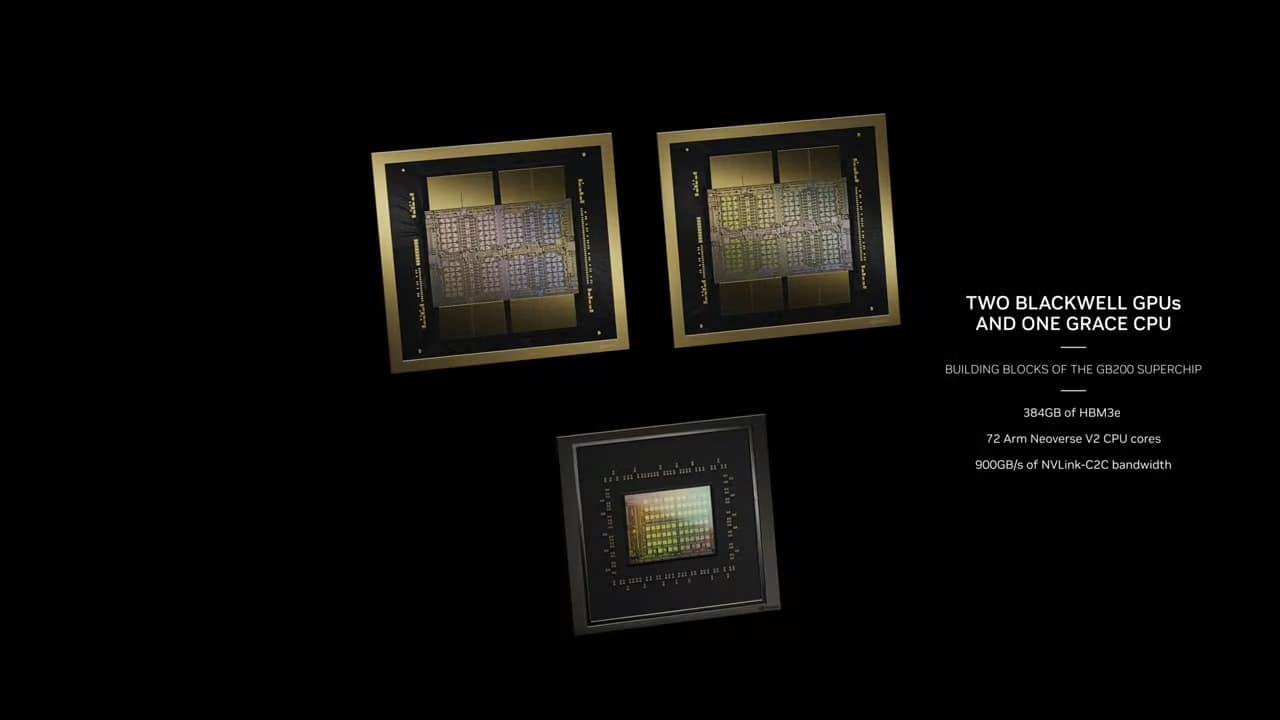

BlackwellアーキテクチャとB200 GPUは、H100/H200の系譜を引き継ぐものだ。また、今回の発表では、Grace Blackwell GB200スーパーチップも登場したが、これはGH200スーパーチップとGrace CPUアーキテクチャは同じものであり、組み合わせられるGPUがアップデートされたBlackwell GPUと置き換えられたものだ。

NVIDIA B200の概要は以下の通りだ。

- 世界で最も強力なチップ – 2,080億個のトランジスタを搭載したBlackwellアーキテクチャGPUは、カスタムビルドの4NP TSMCプロセスを使用して製造されており、2レティクル限界のGPUダイが10TB/秒のチップ間リンクで接続され、単一の統合GPUとなっています。

- 第2世代のTransformer Engine – NVIDIA TensorRT™-LLMとNeMo Megatronフレームワークに統合された、新しいマイクロテンサースケーリングサポートとNVIDIAの高度なダイナミックレンジ管理アルゴリズムによって強化されたBlackwellは、新しい4ビット浮動小数点AI推論機能によって、2倍の計算とモデルサイズをサポートします。

- 第5世代NVLink – 数兆パラメータと専門家の混合AIモデルのパフォーマンスを加速するために、NVIDIA NVLink®の最新の反復は、GPUあたり1.8TB/秒の画期的な双方向スループットを実現し、最も複雑なLLMのために最大576GPU間のシームレスな高速通信を保証します。

- RASエンジン – Blackwell搭載GPUには、信頼性、可用性、保守性のための専用エンジンが搭載されています。さらに、Blackwellアーキテクチャには、AIベースの予防保守を利用して診断を実行し、信頼性の問題を予測する機能がチップレベルで追加されています。これにより、システムの稼働時間を最大化し、大規模なAI導入のための回復力を向上させ、一度に数週間から数カ月にわたって中断することなく稼働し、運用コストを削減します。

- セキュアなAI – 高度な機密コンピューティング機能により、パフォーマンスを損なうことなくAIモデルと顧客データを保護します。新しいネイティブ・インターフェース暗号化プロトコルをサポートしており、ヘルスケアや金融サービスのようなプライバシーに敏感な業界にとって重要です。

- 解凍エンジン – 専用の解凍エンジンが最新のフォーマットをサポートし、データベースクエリを高速化することで、データ分析やデータサイエンスにおいて最高のパフォーマンスを実現します。今後数年間で、企業が年間数百億ドルを費やすデータ処理は、ますますGPUによる高速化が進むでしょう。

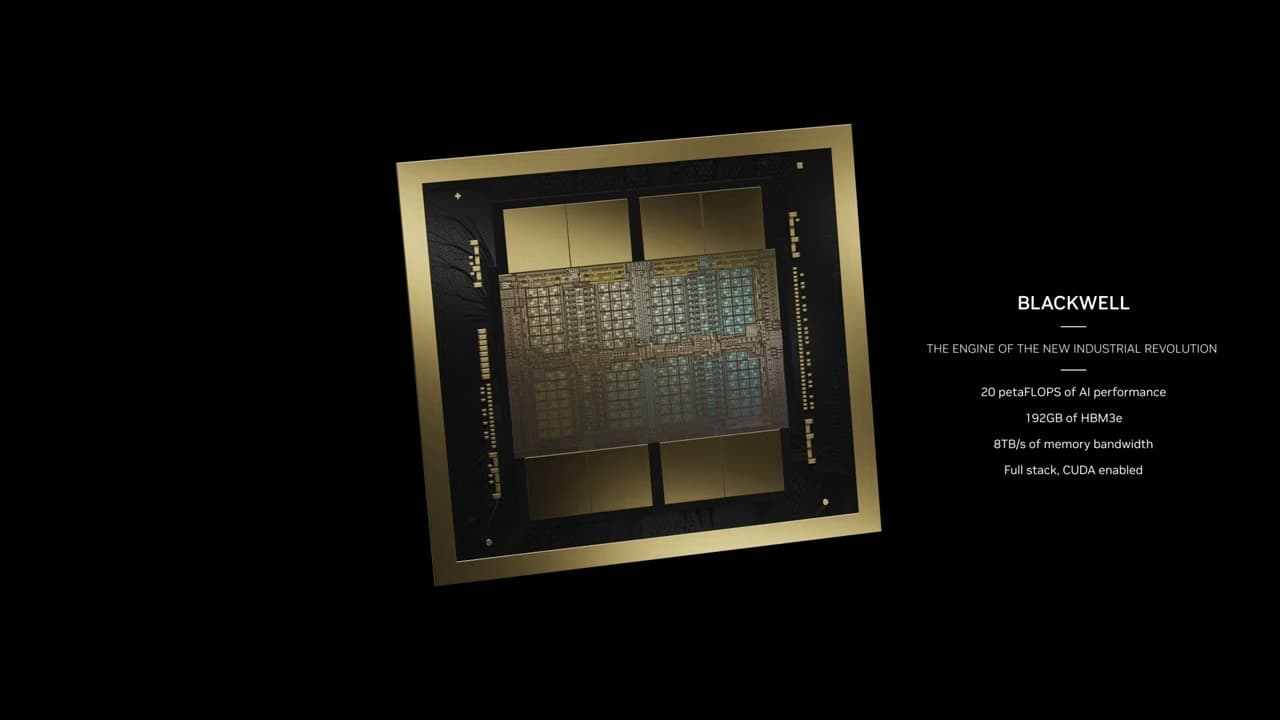

B200 GPUは既存のH100の2倍以上の2,080億トランジスタを搭載している。(H100/H200は800億トランジスタ)。また、GPUあたりのAI演算性能は、H100の最大4ペタフロップスから大幅に向上した20ペタフロップスのAI性能を提供するという。搭載されるメモリは、最大192GBのHBM3eメモリに対応し、最大8TB/秒の帯域幅を提供する。

Blackwell B200は先述したとおり、MCM設計を採用したもので、従来の意味でのシングルGPUではない。NVIDIAによれば、B200は2つの緊密に結合したダイで構成され、1つの統合CUDA GPUとして機能する。2つのダイは、10TB/秒のNV-HBI(Nvidia High Bandwidth Interface)接続を介してリンクされており、完全にコヒーレントな1つのチップとして適切に機能するようになっている。

MCM(マルチチップモジュール)は、NVIDIAが歩留まりやコストといった次世代プロセスノードに関連する課題に取り組もうとしている中で、NVIDIA側にとって長い間待ち望まれていたものだ。これはいわゆる“チップレット”であり、NVIDIAが供給やコスト面で妥協することなく、より高速な世代を超えた性能を達成できる実行可能な代替手段を提供する事になるだろう。製造に関しては、Blackwell B200は、TSMCの4NP(3nmではないのだ)プロセスノードを使用している。これは、既存のHopper H100およびAda LovelaceアーキテクチャGPUで使用されている4Nプロセスを改良したものだ。TSMC 4NPの詳細についてはまだわかっていないが、機能密度が大きく向上することはないだろう。H100は基本的にすでにレチクル・サイズのチップであり、ダイ・サイズは814mm2で、理論上の最大値は858mm2である。

B200は2つのフルレチクルサイズのチップを使用するが、NVIDIAはまだ正確なダイサイズを提示していない。各ダイには、それぞれ24GBのHMB3eスタックが4つあり、1024ビットのインターフェイス上でそれぞれ1TB/秒の帯域幅を持つ。H100では、各16GBのHBM3スタックが6基搭載されていた(当初は、H200ではこれを24GBの6基に増やした)ため、H100のダイのかなりの部分が6基のメモリコントローラ専用だったことになる。チップあたり4つのHBMインターフェイスに落とし、2つのチップをリンクさせることで、NVIDIAはメモリ・インターフェイスに割くダイ面積を減らすことができる。

B200 GPUは合計160個のSMを搭載し、20,480コアを実現する。また、このGPUは、最新のNVLINKインターコネクト技術を採用し、1.8TB/秒の全対全双方向帯域幅を持ち、576 GPU NVLinkドメインをサポートする。これは、同じTSMC 4NPノードで製造された500億トランジスタのチップだ。このチップは、チップ上で3.6テラフロップスのSharp v4インネットワーク・コンピュートもサポートしており、大型モデルの効率的な処理に役立つだろう。

前世代では、HDR InfiniBandの帯域幅は最大100GB/秒をサポートしていたので、帯域幅の増大はかなり大きい。新しいNVSwitchは、H100マルチノードインターコネクトと比較して18倍のスピードアップを提供する。これにより、より大規模な兆レベルパラメータモデルのAIネットワークのスケーリングが大幅に改善されるはずだ。

各Blackwell GPUには18個の第5世代NVLink接続が装備されている。これはH100の18倍のリンク数だ。各リンクは、50 GB/秒の双方向帯域幅、つまり1リンクあたり100 GB/秒の帯域幅を提供する。

また、ピーク時TDPが700Wと非常に消費電力が大きくなるが、これはH100およびH200チップと同じだ。

- TMSC 4NPプロセスノード

- マルチチップパッケージGPU

- 1-GPU 1,040億トランジスタ

- 2-GPU 208億トランジスタ

- 160個のSM(20,480コア)

- 8HBMパッケージ

- 192 GB HBM3eメモリ

- 8 TB/秒 メモリバンド幅

- 8192ビット・メモリ・バス・インターフェース

- 8ハイスタックHBM3e

- TDP 700W(ピーク)

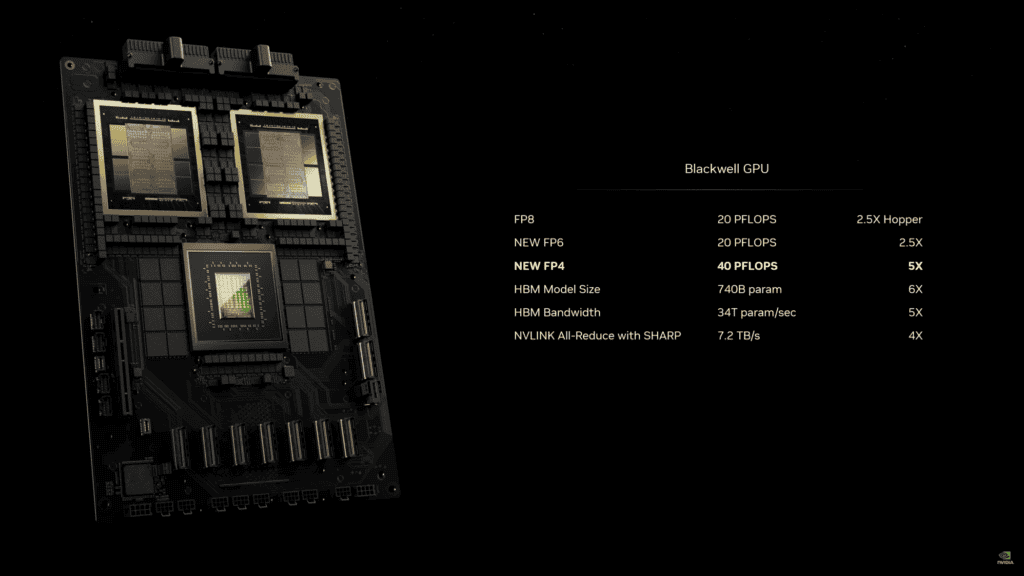

NVIDIAがHopperで大きな成功を収めたのは、アーキテクチャ的に言えば、NVIDIAがTransformer Engineと呼ぶ特殊なハードウェアを搭載することで、Transformer タイプのモデル向けにアーキテクチャを最適化したことだ。NVIDIAは、Transformer がすべての計量とパラメータを高精度(FP16)で処理する必要がないという事実を利用し、これらの演算を低精度(FP8)演算と混在させるサポートを追加することで、必要なメモリを削減し、スループットを向上させた。

第2世代のTransformer Engineでは、NVIDIAはこれを踏襲する。Blackwellは、FP4精度までの数値フォーマットを扱えるようになり、推論に超低精度フォーマットを使用することを視野に入れている。一方、NVIDIAは、FP8でより多くのトレーニングを行うことを視野に入れており、これによっても計算スループットを高く保ち、メモリ消費量を低く抑えることができる。

Transformerは、精度をそれほど落とすことなく低精度フォーマットを扱う興味深い能力を示している。しかし、FP4は控えめに言ってもかなり低い。FP4が推論に有用であるかどうかが、推論プラットフォームとしてのB200の良し悪しを決めると思われるからだ。

いずれにせよ、NVIDIAは1台のB200アクセラレータで最大10ペタFLOPSのFP8性能(スパース性を利用すると仮定した場合、H100の約2.5倍)、さらに推論では20ペタFLOPSのFP4性能を提供できると見込んでいる。H100はFP4の恩恵を受けていないため、FP8の最小データサイズと比較すると、B200はFP4が使用可能な場合、推論スループットが5倍向上することになる。

また、NVIDIAの演算性能比がH100と変わらず、FP16の性能がFP8の半分で、そこからスケールダウンすると仮定すると、B200はより高い精度でも非常に強力なチップになる。少なくともAI用途では、可能な限り低精度で済ませることが目標であることは明らかだが。

もう一方では、基調講演に先立ち、FP64テンソルの性能についても未公表のままだ。NVIDIAはAmpereアーキテクチャ以来、FP64テンソル機能を提供してきたが、低精度に比べればはるかに低いレートである。これは、大半のAIワークロードにはほとんど役に立たないが、HPCワークロードには有益である。NVIDIAがここでどのような計画を立てているのか、B200がHPC向けの機能を多く持っているのか、あるいはNVIDIAが低精度AIに全面的に取り組むつもりなのかは不明だ。

Source