2023 IEEE International Electron Devices Meeting (IEDM 2023)では、半導体企業、研究グループ、大学が現在の半導体開発に関する最新の研究成果を発表している。

今年は、主にバックサイドパワーデリバリーネットワーク(BSPDN)、パッケージング、トランジスタの2nm以下への微細化といった分野の技術開発に焦点が当てられる。

Intel、TSMC、Samsungのような企業、あるいはimecのような研究企業がIEDM 2023で何を発表するかを見ることは、今後数年、あるいは数十年先の半導体セクターで何が起こるのかを先取りする事にも繋がる。Intelの場合、研究成果はコンポーネント・リサーチ(CR)グループによって発表される。その結果、開発グループの生産技術やパッケージング技術が提供される。とはいえ、その技術が、いつ、どのような形で、あるいはどの製品に使われるかは、まったく別の問題ではあるが。

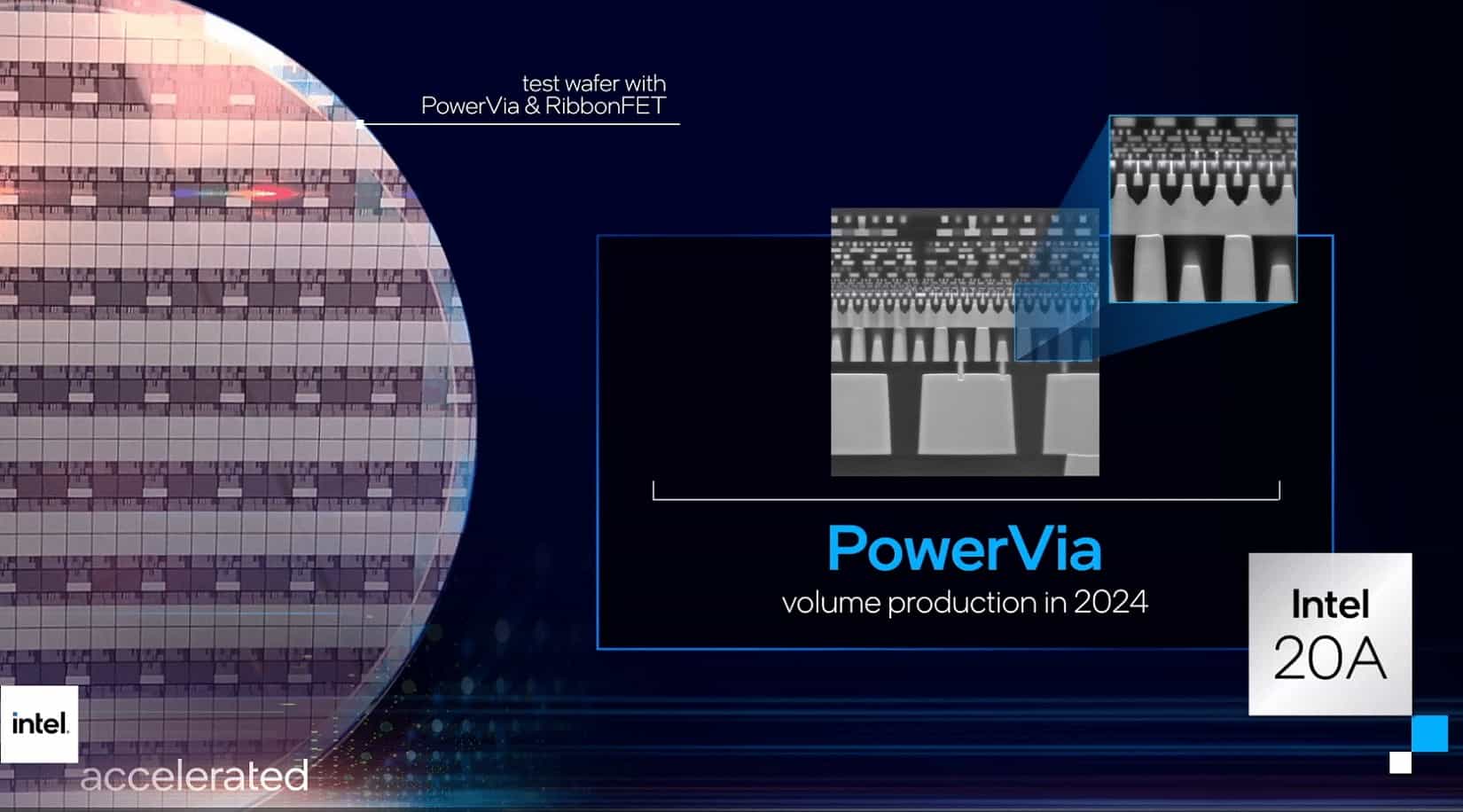

しかしもちろん、提示された技術と具体的なロードマップとの間に直接的なつながりがあることもある。バックサイドパワーデリバリーネットワーク(BSPDN)である「PowerVia」テクノロジーは、Intel 20Aで製造される最初のプロセッサーにおいて見ることが出来るだろう。PowerViaの利点については、電源と信号供給を分離することのメリットに焦点を当てて紹介されている。例えば、今年のVLSIや、Intel 4での試験生産に基づく最初の具体的な結果などである。

しかし、IntelのPowerViaテクノロジーは、数あるBSPDNのひとつに過ぎない。PowerViaは、チップの裏側からトランジスタセルに直接電源を供給する。もう一つの実装は、チップに水平に組み込まれ、トランジスタセルに電源を供給するBurried Power Rail(BPR)である。BPRはフロントサイド電源(Frontside Power Delivery)を介して実装することもできる。

だが、プロセス技術の次のステップと、これまで以上に微細な構造のために、IntelはPowerViaを超えなければならない。この目的のために、BSCON(Back-Side Contacts:バックサイド・コンタクト)が開発された。

BSCONは、トランジスタ技術の次のステップとなるトランジスタセルを積層する際に使用される。現時点では、Intelはナノシート・トランジスタとしても知られるRibbonFETに取り組んでいる。第一世代では、これらのRibbonFETは互いに隣接して配置されるが、さらなるステップでは、これらも積層され、さらにスケーリングされる。したがって、これらのトランジスタ・セルに必要な電圧を供給する方法を開発しなければならない。そこで、BSCONの出番となる。

BSCONは長さが短いため、配電層を超えるキャパシタンスが小さくなり、トランジスタのスイッチング速度が速くなるため、高いクロックレートを実現できる。その一方で、安定した電圧供給を実現する必要があるため、このセグメントではPowerViaとBSCONの開発に多くの研究作業が費やされている。

そして、まだ導入されていないPowerViaは、垂直面のスペースを節約し、トランジスタ密度を高めるために、将来のプロセス・ステップで再び省略されることになる。これは、積層RibonFET(NMOS on PMOSなど)にとって特に重要になる。

トランジスタを2つの側面から接点で接続する(片側から信号、もう片側から電源)ためには、もちろんウェハーの扱いを変えなければならない。まず、現在のように金属層を持つチップをウェハーの前面から露出させる。Intelによれば、M0メタル層の複雑さが大幅に軽減されたことで、この工程も簡素化されるはずだという。その後、キャリア・ウェハーを貼り付け、2枚のウェハーを回転させ、すでに露出しているウェハーの裏面をトランジスタ・レベルまで研磨する。その後、nanoTSVと電源用金属層の構築に取りかかる。

しかし、ボンディング工程とウェハーの研磨はウェハーに影響を及ぼし、歪みを引き起こす。水平面におけるこの歪みは、BSPDNのミスアライメントにつながる。しかし、Intelはこの影響を最小限に抑える適切な技術にも取り組んでいる。

基本的に、この問題はパッケージングでもおなじみのもので、より小さな接点が互いを見つけなければならない。Foverosダイレクトでは、バンプ・ピッチ、すなわちコンタクト間の距離を10μm以下に縮小する必要がある。TSMCはこのために、バンプピッチがすでに9μmであるハイブリッド・ボンディングなどのパッケージング・プロセスを使用している。PowerViaに使用されるTSVは、現在パッケージングに使用されているTSVの500分の1であると言われており、BSPDNのボンディングプロセスの精度も強調されている。

早ければ来年には、Intel 20AのArrow LakeプロセッサーにPowerViaが搭載され、RibbonFETも使用されることが予想されるが、実際の製品にBSCONのような技術が搭載されるまでには、まだ時間がかかるだろう。

Sources

コメント