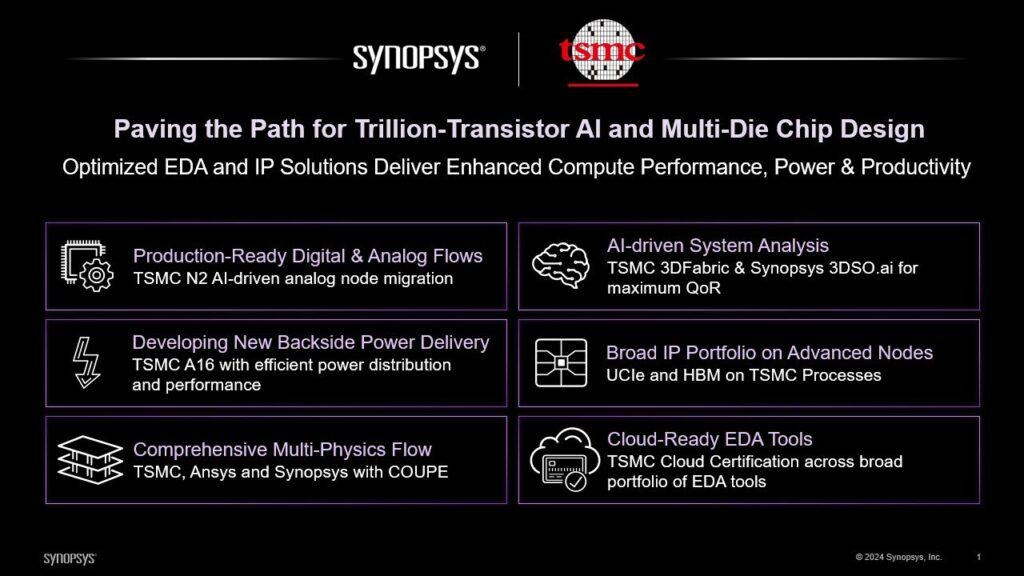

半導体設計ツールの大手Synopsysと世界最大の半導体ファウンドリTSMCが、次世代AIチップ開発に向けた協業を発表した。両社の長年にわたるパートナーシップが新たな段階に入り、急増するAIコンピューティング需要に応えるべく、両社は現在1兆個のトランジスタを搭載するチップの設計・製造を可能にする技術の開発を進めているとのことだ。

AIチップ設計の革新:SynopsysのAI駆動型EDAツールとTSMCの先端プロセス技術の融合

Synopsysは、TSMCの最新プロセスノードに対応したAI駆動型EDA(Electronic Design Automation)スイートとマルチダイソリューションの開発を進めている。この取り組みは、TSMCの最新プロセスノードおよび3Dパッケージング技術と密接に連携しており、次世代AIチップの設計・製造を加速させることが期待されている。

具体的な成果として、SynopsysのカスタムデザインおよびシミュレーションツールがTSMCのN2ノード(2nmプロセス)向けに認証を受けており、すでにMediaTekの製品開発に貢献している。MediaTekのCorporate VPであるChing San Wu氏は、「Synopsysの認証済みCustom CompilerおよびPrimeSimソリューションにより、TSMC N2プロセスにおける高性能アナログ設計のシリコン要求を満たすパフォーマンスと生産性の向上が実現されています」と述べている。さらに、「Synopsysとの協力関係を拡大することで、AI駆動型フローの可能性を最大限に活用し、設計の移行と最適化プロセスを加速させ、複数の垂直市場向けに業界をリードするSoCを提供するために必要なプロセスを改善することが可能になります」と付け加えた。

さらに、SynopsysはTSMCの最先端プロセスであるA16(1.4nmプロセス)向けに、バックサイドルーティング技術をサポートする物理検証および実装ソリューションを開発した。バックサイドルーティングは、チップの背面に電源供給ラインを配置する新技術で、性能と密度の向上に寄与する。この技術は、2026年後半に量産が予定されているA16プロセスにおいて、電力供給と信号配線の最適化を実現し、チップの性能と密度を向上させる重要な役割を果たすと期待されている。

マルチダイ設計の進化:複雑化するAIチップに対応する統合ソリューション

AIチップの複雑化に伴い、マルチダイ設計技術の重要性が増している。Synopsysはこの課題に対応するため、3DIC Compilerプラットフォームを強化し、複雑な2.5Dおよび3Dマルチダイパッケージの設計、実装、検証を統合環境で行えるようにした。

この取り組みは、AnsysおよびTSMCとの協力により実現された。最新のアップデートでは、Ansysの業界標準のRedHawk-SCパワーインテグリティ・サインオフプラットフォームと緊密に統合された熱およびIR(電圧降下)を考慮したタイミング解析が可能になった。さらに、Synopsys 3DIC CompilerはTSMCの3DFabricをサポートする認証済みプラットフォームとなっており、TSMC-SoIC(System on Integrated Chips)およびCoWoSパッケージング技術を含む高度な3D積層技術に対応している。

この統合ソリューションにより、設計者はチップ、パッケージ、およびシステムレベルの効果を考慮した正確なサインオフ精度を達成できるようになった。Ansysの半導体、エレクトロニクス、オプティクス事業部門のバイスプレジデント兼ゼネラルマネージャーであるJohn Lee氏は、「Synopsys、TSMCとの協力は、イノベーションを推進し、AIおよびマルチダイチップ設計の未来を実現するという私たちの共同の取り組みを示しています。共に、マルチダイアーキテクチャに固有のマルチフィジックス課題に取り組み、最新のTSMCテクノロジーにおけるSynopsys設計環境内でのチップ、パッケージ、およびシステムレベルの効果に対するゴールデンサインオフ精度の達成を支援しています」と述べている。

さらに、SynopsysはTSMCと協力して、UCIeおよびHBM3 IPを含む包括的なマルチダイテストソリューションを開発した。これにより、製造テストおよび現場での使用中にマルチダイパッケージの健全性を確保することが可能になる。両社は、TSMCのCoWoSインターポーザー技術を利用したテストチップを設計し、テスト、監視、デバッグ、修復機能を完全にサポートしている。

最新の開発では、Synopsys UCIe IPが最大40Gで動作し、追加の面積を必要とせずに最大の帯域幅とエネルギー効率を実現している。また、HBM4および3DIO IPソリューションは、TSMCの先進プロセスにおける3D積層ダイの異種集積を加速している。これらの技術的進歩により、2030年頃には1兆トランジスタを超える巨大なマルチチップレットパッケージの実現が期待されている。

Source

コメント