TSMCは同社の次世代プロセスとなる「A16」プロセスの詳細を発表した。

TSMC初のオングストローム級製造ノードとなるA16(1.6nm)は、その前身となるN2P(2nm)プロセスを大きく上回る性能を実現するという。

TSMC A16:GAAFETとBSPDNが採用され大幅な性能向上

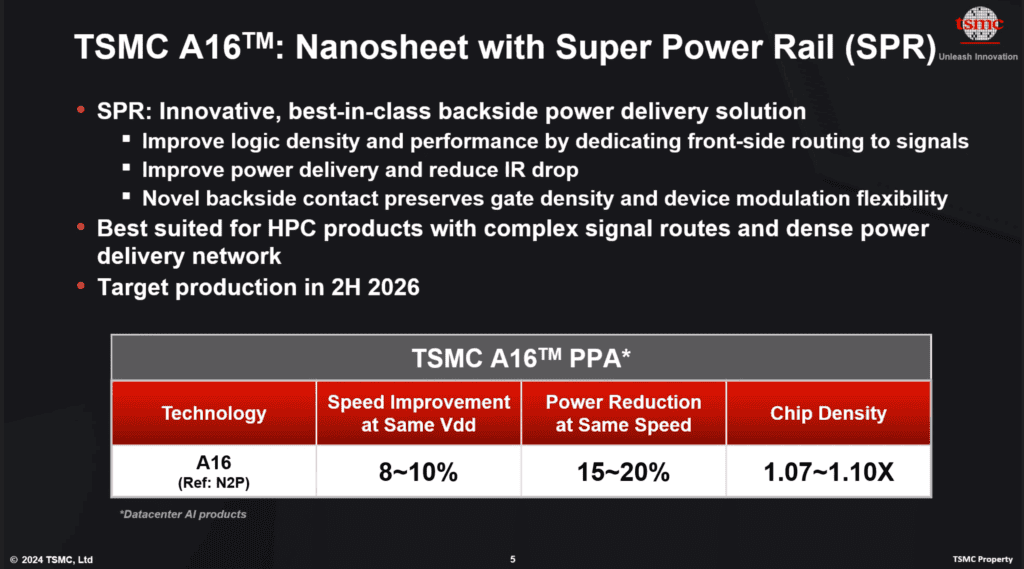

TSMC A16プロセスは、前世代の2nmノードから採用されるGAA(Gate-All-Around)FETと共に、同社初のBSPDN(Back-Side-Power-Delivery-Network)が採用される。TSMCのBSPDNは「Super Power Rail (SPR)」と呼ばれるが、このGAAとBSPDNの両輪によってA16プロセスはN2Pと比較して大きな性能向上を果たすとTSMCは述べている。

TSMCによると、A16プロセスは、N2P比較で、同じ電圧で最大10%のクロック・レート向上と、同じ周波数とトランジスタ数で15%から20%の消費電力削減が見込まれという。さらに、実際の設計にもよるが、トランジスタ密度を7%~10%向上させることができるとのことだ。

そしてA16プロセスの革新の鍵は、TSMC初のBSPDNであるSuper Power Rail (SPR)にある。TSMCは、A16のSPRは、複雑な信号経路と高密度な電力回路の両方を特徴とする高性能コンピューティング(HPC)製品向けに特別に調整されていると述べている。

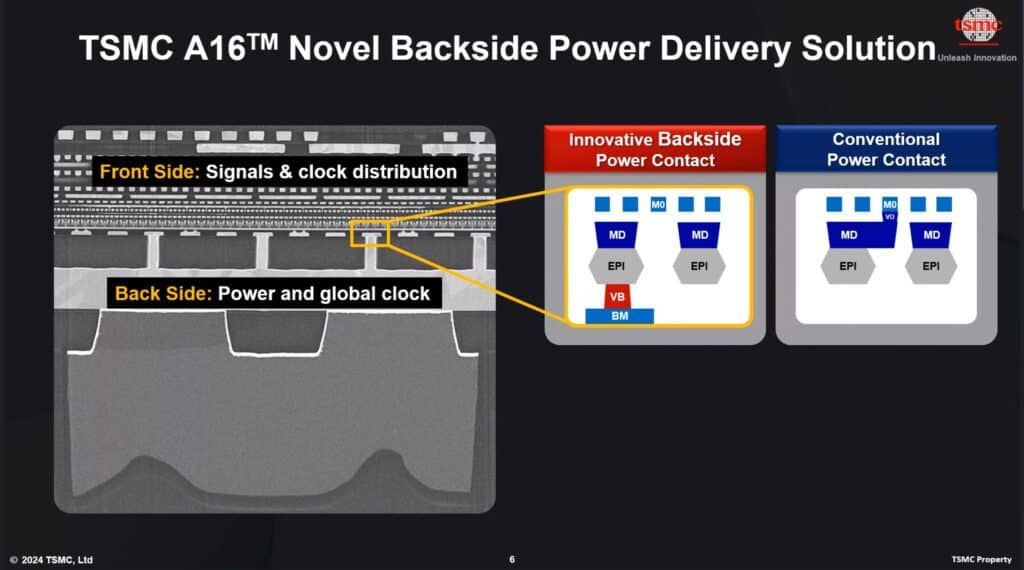

BSPDNは、トランジスタ密度の向上と、性能に影響する電力供給の改善を可能にするため、今後登場する多くのプロセス技術に実装されることになる。一方、BSPDNを実装する方法はいくつかある。ImecのBuried Power Rail、IntelのPowerVia、そして今回のTSMCのSuper Power Railである。

最も古い手法であるImecのBuried Power Railは、基本的にウェハーの裏面にPower Delivery Network(PDN)を配置し、ロジック・セルのパワー・レールをナノTSVを使ってパワー・コンタクトに接続する。これにより、ある程度の面積のスケーリングが可能になり、製造に複雑さを加えることもない。2番目の実装であるIntelのPowerViaは、電力をセルまたはトランジスタのコンタクトに接続する。

TSMCのSPRは、BSPDNを各トランジスタのソースとドレインにプラグインし、抵抗も低減する特殊なコンタクトを使用することで、最大限の性能と電力効率を実現する。TSMCによると、これは面積の拡大という点では最も効率的な技術だが、生産に関しては最も複雑(かつ高価)であるというトレードオフがある。

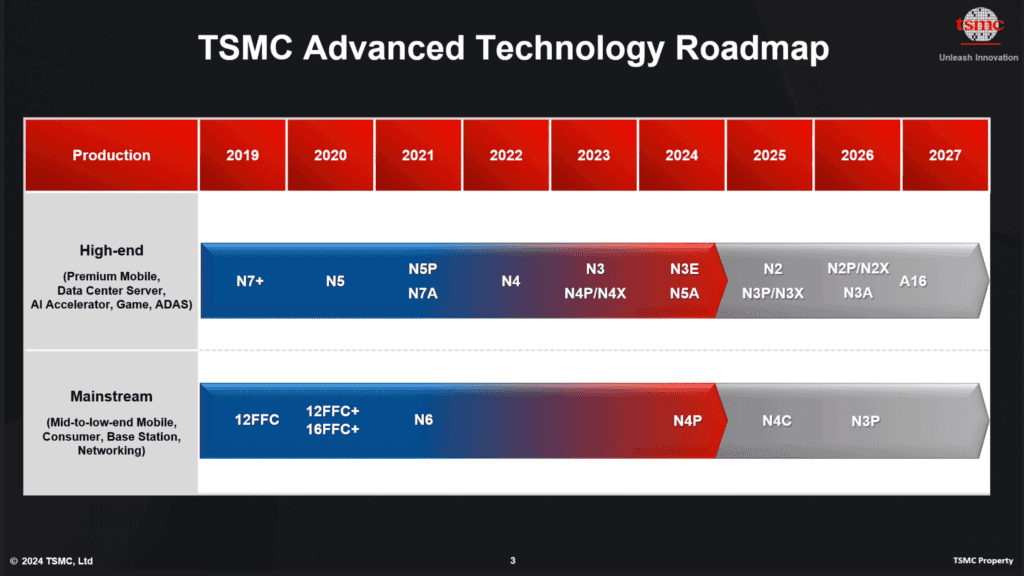

TSMCは当初、2026年にN2PでBSPDN技術を提供する予定だったが、理由は明らかではないが、この技術はN2Pから外され、A16から採用されることとなった。TSMCがBSPDNの最も複雑なバージョンを選択したことは、N2PからBSPDNが削除された理由の一部かもしれない。これにより、A16は2026/2027年のTSMCの最高性能ノードとなり、N2Pは性能とコスト効率のバランスの取れた組み合わせとなる。

A16の生産スケジュールによると、A16の量産は2026年後半に開始される。したがって、実際のA16製製品は2027年に登場する可能性が高い。このスケジュールでは、A16はIntelの14Aノード「Intel 14A」と競合する可能性がある。

Sources

コメント