TSMCが2027年までに革新的なCoW-SoW(System-on-Wafer)パッケージング技術の量産を計画していることが明らかになった。この技術は、巨大なチップの開発を可能にし、これまで以上に高性能なAIチップの登場を約束する画期的な動きとなるだろう。

TSMCが描く次世代チップの青写真

台湾積体電路製造(TSMC)は、2027年までに次世代CoW-SoW(System-on-Wafer)先進パッケージング技術の量産を開始する計画を発表した。この革新的な技術は、メモリと論理チップを単一のインターフェース上に積層することで、より高速なパフォーマンスと、チップ上のダイ間のブリッジングの精度向上を実現する。

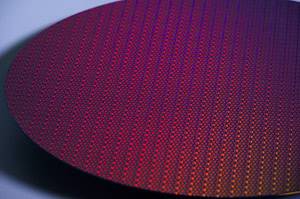

CoW-SoW技術の最大の特徴は、その規模と集積度にある。TSMCによると、この技術は現在のレチクル制限の40倍の面積を持ち、HBM(High Bandwidth Memory)容量を60倍に拡大できるという。これにより、AIや大規模データセンター向けの巨大チップの開発が可能となる。

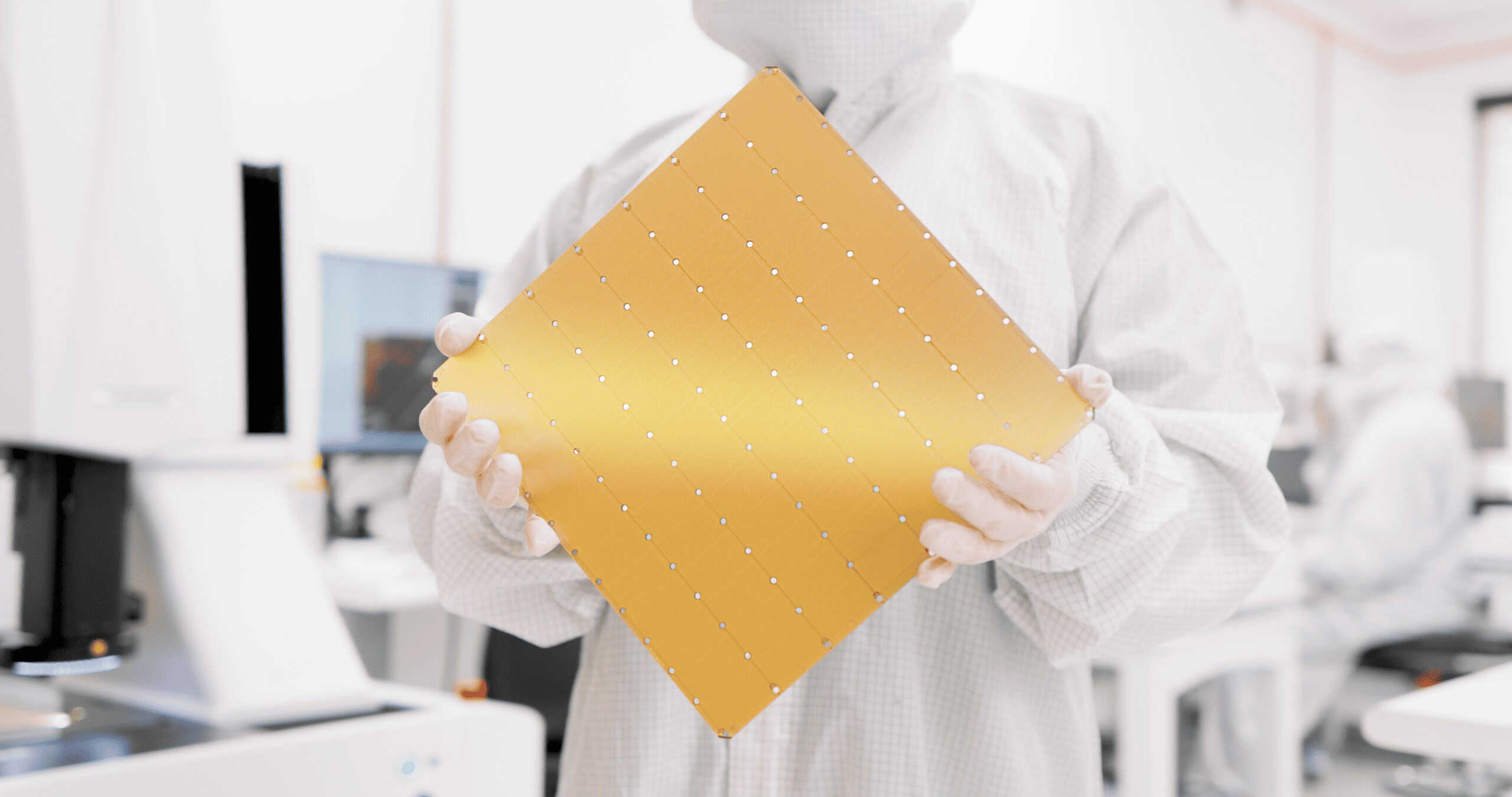

実際に、TSMCのCoW-SoW技術は既にCerebrasによって採用されている。Cerebrasは、AI市場向けに世界最大のウェハースケールチップを開発しており、TSMCはこの経験を活かして技術の完成度を高めている。

CoW-SoW技術は、TSMCが長年開発してきたInFO-SoW(Integrated Fan-Out System-on-Wafer)技術とSoIC(System on Integrated Chips)技術を組み合わせたものだ。この新技術により、記憶素子や論理チップを直接ウェハー上に積層することが可能になる。これは、AIワークロードが要求する大容量メモリへの需要に応えるものであり、半導体業界の未来を切り開く重要な技術革新となる可能性がある。

巨大化するAIチップと製造の課題

現在のAI業界では、チップの大型化が進んでおり、製造プロセスにおいて新たな課題が浮上している。NVIDIAの最新AIチップアーキテクチャであるBlackwellは、その代表例だ。NVIDIAのCEOである黄仁勳氏が「非常に非常に大きなGPU」と評したBlackwellは、2つのチップを組み合わせて作られており、TSMCの4nm製造プロセスを採用し、2,080億個のトランジスタを搭載している。

しかし、このような巨大チップの製造には複雑な課題が伴う。特に、GPU、LSIブリッジ、RDL(再配線層)、およびメインサブストレート間の熱膨張係数(CTE)の違いにより、チップの反りやシステム障害が発生する可能性がある。これらの問題を解決するため、NVIDIAはGPUチップの最上位金属層とバンプの再設計を行った。

AMD CEOのLisa Su氏も、チップサイズの拡大に伴い製造の複雑さが増加することは避けられないと指摘している。次世代チップは、AIデータセンターの巨大な計算能力需要を満たすため、性能と消費電力の両面でブレークスルーを実現する必要がある。

CoW-SoW技術がもたらす未来

TSMCのCoW-SoW技術は、これらの課題に対する解決策となる可能性がある。この技術により、より大規模で複雑なAIチップの製造が可能になり、性能と電力効率の両面でブレークスルーを実現することが期待される。

CoW-SoW技術の導入により、AIや大規模データセンター向けの「巨大なAIチップ」の開発が加速すると予想される。この技術革新は、半導体業界全体に波及効果をもたらし、AI分野における台湾の重要性をさらに高めることになるだろう。

2027年の量産開始を目指すTSMCのCoW-SoW技術は、NVIDIAの次世代アーキテクチャであるRubinにも採用される可能性がある。これにより、AI性能のさらなる飛躍的向上が期待される。

Cerebrasのように「1枚のウェハーが1つのプロセッサ」となる巨大AIチップの開発が今後増加すると予想される。TSMCのCoW-SoW技術は、このトレンドを加速させ、半導体業界に新たな可能性をもたらすことになるだろう。AI技術の進化と共に、より大規模で効率的なチップの需要が高まる中、TSMCの技術革新は業界の未来を切り開く重要な役割を果たすことになりそうだ。

Sources

コメント