台湾の半導体受託製造最大手TSMCの次世代製造プロセスである2nmノードの開発において、テスト段階での歩留まり率が6%改善されたことが明らかになった。この進展により、同社の顧客企業に対して数十億ドル規模のコスト削減効果がもたらされる見通しである。

歩留まり改善の具体的成果

TSMCのエンジニアであるDr. Kimが、2nmプロセスのテストチップ製造における歩留まり率が6%向上したことをXにて報告している。この改善は、2025年後半に予定される量産開始に向けた重要なマイルストーンとなる。ただし、この歩留まり改善がロジック回路とSRAMのいずれのテストチップで達成されたかについては明らかにされていない。

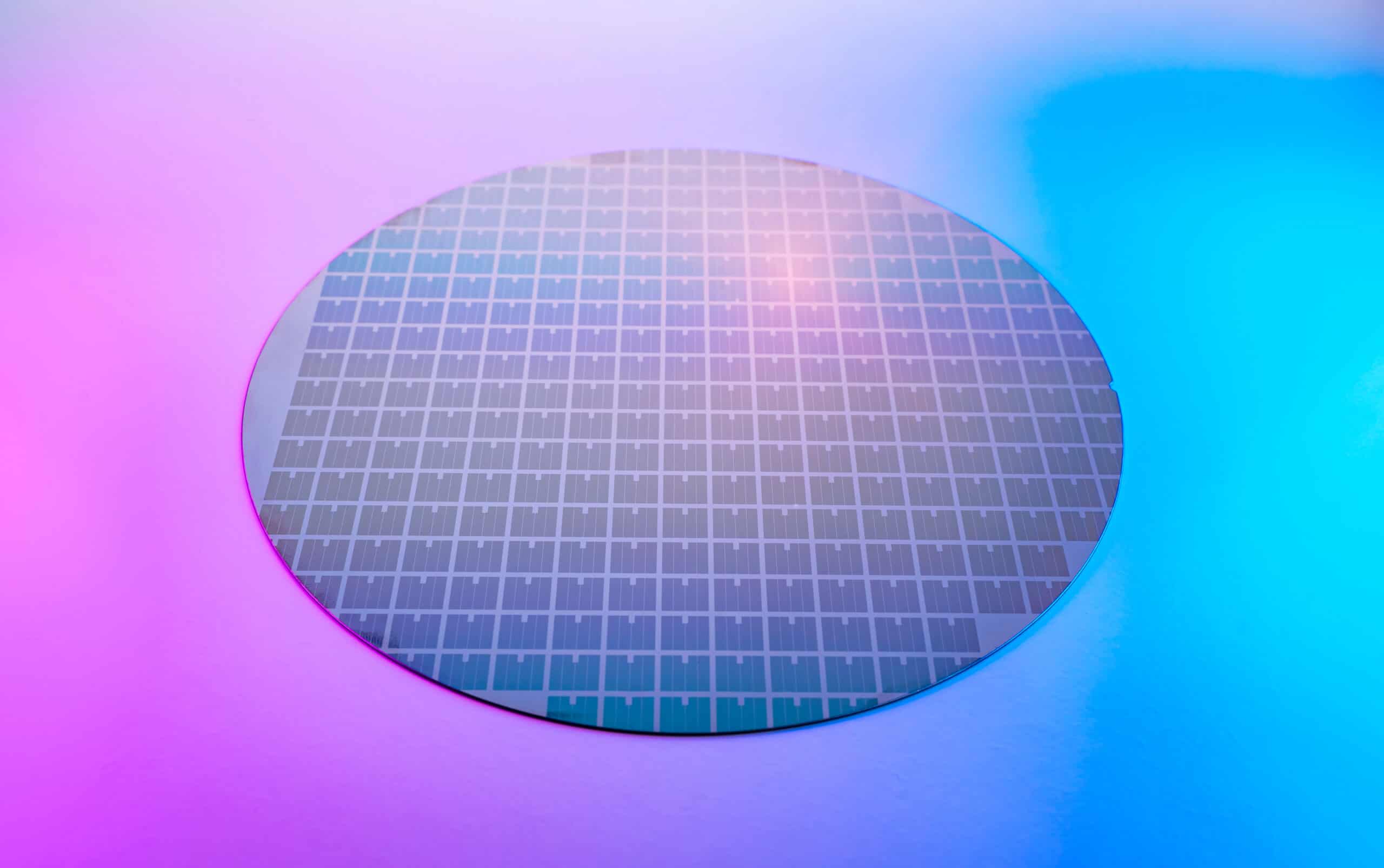

なお、TSMCは2024年1月から2nmプロセスのシャトルテストウェハーサービスを開始する予定であり、今回の歩留まり改善は実際の製品チップではなく、開発段階のテストチップにおける成果であると考えられる。

革新的な技術進展と期待される性能向上

TSMCの2nmプロセスは、同社の半導体製造技術における画期的な転換点となる。その中核となるのが、初めて採用されるGate-All-Around(GAA)ナノシートトランジスタ技術だ。この新しいトランジスタ構造は、現行の3nmプロセスで採用されているFinFET(Fin Field-Effect Transistor)からの進化形として位置づけられる。

従来のFinFET構造では、チャネル部分を「フィン」と呼ばれる突起状の構造で形成し、その三方をゲートで制御していた。これに対して新しいGAAナノシートトランジスタでは、チャネルを薄いシート状の構造として形成し、その全周をゲートで取り囲む設計となっている。この構造的な革新により、電流の制御性が大幅に向上し、より微細な製造プロセスにおいても安定した動作を実現できる。

この技術革新がもたらす具体的な性能向上は、現行の3nmプロセス(N3E)と比較して極めて顕著なものだ。同じトランジスタ数と動作周波数での比較において、消費電力を25%から30%削減できることが最大の特徴となる。これは、モバイルデバイスのバッテリー時間の延長や、データセンターの電力効率改善に直接的な恩恵をもたらす。

さらに、消費電力を維持したまま演算性能を10%から15%向上させることも可能となる。この性能向上は、人工知能の処理やビッグデータ解析など、高い計算能力を必要とするアプリケーションにおいて特に重要な意味を持つ。

トランジスタ密度に関しても、同等の速度と消費電力を維持しながら15%の向上を実現する。これにより、より多くの機能を同じダイサイズに統合することが可能となり、製造コストの削減にも貢献する。

特筆すべきは、新しいGAAナノシートトランジスタが高密度SRAM(Static Random-Access Memory)の小型化にもたらす効果だ。改善された静電制御と漏電流の低減により、性能を損なうことなくSRAMビットセルの小型化が可能となる。これは、プロセッサのキャッシュメモリやSoC(System-on-Chip)設計において、より効率的なメモリ配置を実現する上で重要な進展となる。

このような包括的な性能向上は、閾値電圧の精密な調整機能によって支えられている。GAAアーキテクチャでは、トランジスタのチャネルを完全に取り囲むゲート構造により、これまでにない精度での電圧制御が可能となり、微細化に伴う性能低下や信頼性の課題を効果的に解決している。

Xenospectrum’s Take

今回の歩留まり改善は、半導体業界にとって極めて重要な意味を持つ。6%という一見小さな数字が、実際には数十億ドル規模のコスト削減につながる現実は、最先端半導体製造の経済的な重要性を如実に物語っている。

しかし、2025年後半の量産開始までには依然として多くの技術的課題が残されている。特に、GAAアーキテクチャへの移行は、製造プロセスの複雑性を大幅に増加させる。TSMCがこの歩留まり改善を実際の製品製造でも実現できるか、業界の注目が集まるところだ。

とはいえ、早い段階でこのような改善を達成できたことは、TSMCの技術力の高さを示すものであり、2nmプロセスの成功に向けて順調なスタートを切ったと見ることができるだろう。

Sources

コメント