半導体業界で最高のゲーミング性能を誇るAMD Ryzen 7 9800X3Dの詳細な構造解析により、プロセッサの大部分が構造保持のためのダミーシリコンで構成されていることが明らかとなった。半導体アナリストのTom Wassickによる詳細な分析で、AMDの第2世代3D V-Cache技術の革新的な設計思想が浮き彫りになった。

革新的な積層構造の詳細が判明

半導体アナリストTom Wassick氏による詳細な分析で、Ryzen 7 9800X3Dの内部構造における重要な技術革新が明らかになった。最も注目すべき発見は、AMDが採用した新しい積層アプローチだ。従来のプロセッサ設計とは異なり、第2世代3D V-Cache技術では、発熱源となるCCD(コンピュート・ダイ)の下にL3 SRAMキャッシュチップレットを配置している。

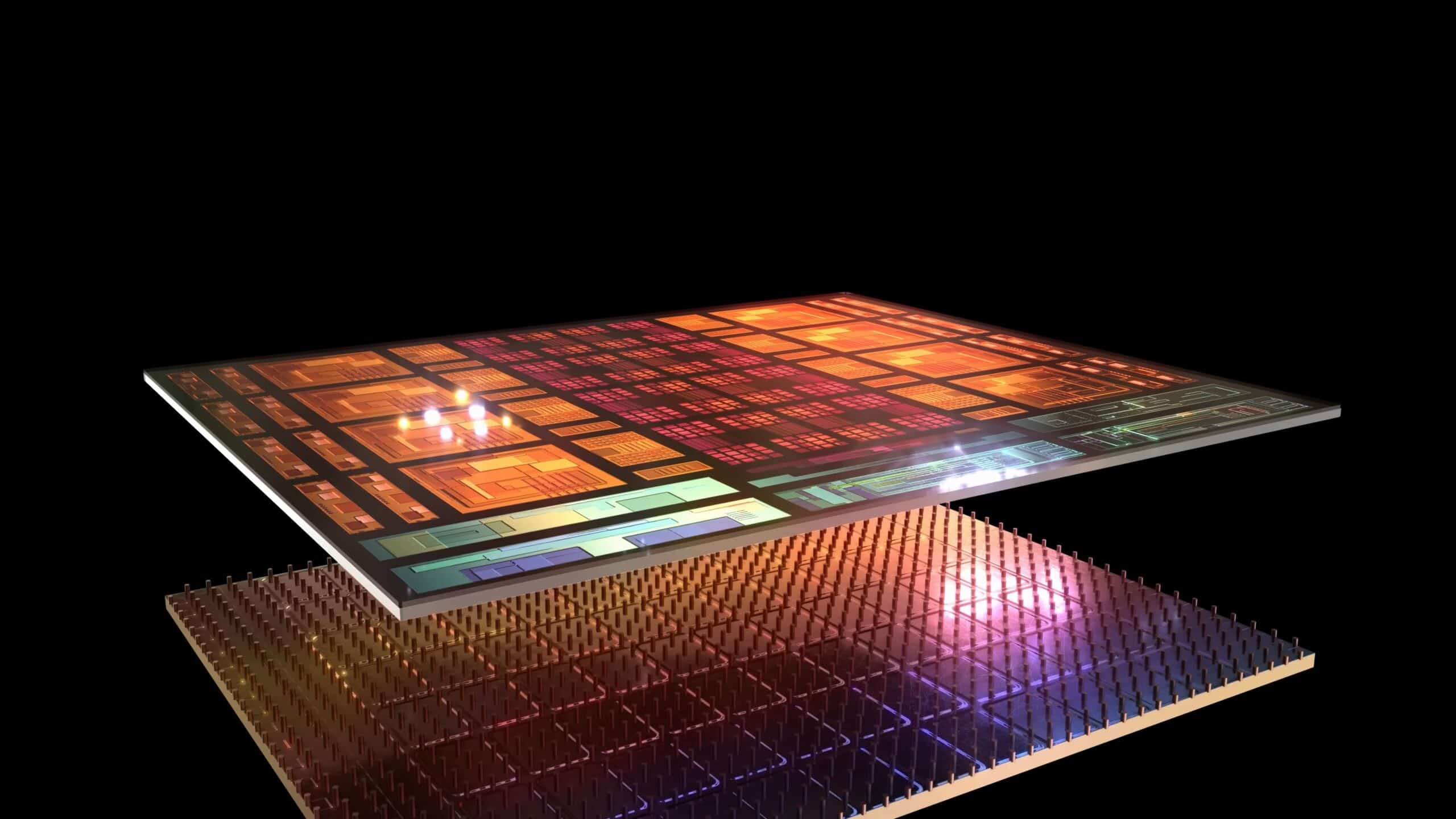

この構造を実現するため、AMDは極めて精密な加工技術を駆使している。CCDとSRAMチップレットは、驚くべきことにわずか10マイクロメートル未満という極薄さまで研磨されている。この極限まで薄くされた状態で、TSV(Through-Silicon Via)と呼ばれる貫通電極を露出させ、ハイブリッドボンディングによる接続を可能にしている。さらに、金属配線層を含むBEOL(Back-end of Line)部分を加えても、SRAMとCCDを合わせた総厚は40-45マイクロメートルに収まっている。

興味深いのは、SRAMダイの設計思想の大胆な転換だ。従来のRyzen 7000シリーズでは、3D V-Cacheチップレットは36平方ミリメートルと、66.3平方ミリメートルのCCDよりもかなり小さかった。しかし新設計では、SRAMダイがCCDよりも四方に50マイクロメートルずつ大きく設計されている。この変更には重要な技術的意義があると考えられるが、その詳細についてはWassick氏による今後の分析を待つ必要がある。

革新は接続技術においても見られ、TSV間の間隔は約15マイクロメートルと、第1世代の17マイクロメートルからわずかながら改善も見られる。この微細な改善が、全体的な性能向上にどの程度寄与しているかは、さらなる調査が必要だ。チップ間の接続には、銅の接着性を利用したハイブリッドボンディング技術が採用されており、従来のはんだ付けは不要となっている。これにより、より薄い接合層の実現と、それに伴う熱伝導効率の向上が可能になったと考えられる。

構造保持のための革新的アプローチ

半導体チップの微細化が進む中、AMDのRyzen 7 9800X3Dで採用された構造保持手法は、現代の半導体設計が直面する課題への独創的な解決策を示している。Wassick氏の分析によると、プロセッサパッケージの全体の厚さは約800マイクロメートルに達するが、その大部分は構造保持のためのダミーシリコンで占められている事実が判明した。実際の演算処理を担うCCDとSRAMチップレット、そしてBEOL層を合わせた厚さはわずか50マイクロメートル程度であり、残りの約750マイクロメートルは純粋に物理的な保護と構造的完全性を維持するための支持材として機能している。

この設計思想の背景には、極限まで薄くされたチップの脆弱性への対処という課題がある。10マイクロメートル未満まで薄く加工された演算部分は、そのままでは取り扱いが極めて困難で、製造工程や実際の使用時の物理的ストレスに耐えられない。AMDはこの問題に対し、上下にダミーシリコンを配置することで解決を図った。このアプローチにより、パッケージ全体の厚さを500から800マイクロメートルという、AMDやIntelが標準的なチップ厚として採用している範囲内に収めることにも成功している。

熱設計の観点からも、興味深い工夫が施されている。チップ間の接合には酸化物層が使用されているが、その厚さは場所によって意図的に変えられている。特筆すべきは、発熱源となるコアCCDとSRAM間の酸化物結合層を、ダミーシリコンと実働部分との間の結合層よりも薄く設計している点だ。これは熱伝導効率を最適化するための慎重な設計判断と考えられる。酸化物層の数と厚さは熱転送において極めて重要な要素であり、AMDはこれらを可能な限り最小限に抑えることで、熱問題の解決を図っている。

この構造設計の詳細な分析は現在も進行中で、Wassick氏は走査型電子顕微鏡を用いたさらなる調査を予定している。特に、64MBの追加キャッシュを構成するSRAMブロックの具体的な配置や、パッケージ基板からチップへの配線経路など、まだ解明されていない技術的詳細が多く残されている。これらの分析結果は、次世代プロセッサの設計に重要な示唆を与えるものと期待されている。

Xenospectrum’s Take

この発見は、最先端の半導体パッケージング技術が直面する興味深いパラドックスを示している。極限まで薄くした実働シリコンを保護するために、その何倍もの「無駄な」シリコンが必要とされるという事実は、微細化の限界に挑戦し続ける半導体業界の現状を象徴している。

TSMCとの緊密な協力関係なしには実現不可能なこの技術は、単なる製造委託を超えた深い技術的パートナーシップの重要性を示唆している。来月のCESで発表が予想されるRyzen 9 9900X3DとRyzen 9 9950X3Dでは、この技術がどこまで進化するのか注目したいところだ。

Source

- Tom Wassick

- HardwareLuxx: Neue Details zu AMDs Stapeltechnik

コメント