AMDのCEO、Lisa Su博士が次世代AIアクセラレータ「Instinct MI450」にTSMCの2nmプロセス技術を採用することを正式に認めた。 これは、競合するNVIDIAの次世代アーキテクチャ「Rubin」が3nmプロセスを採用すると見られる中で、AMDがプロセス技術において先行する可能性を示唆する重要な発表である。

AMD、次世代AIアクセラレータでプロセス技術の主導権を掌握

2025年10月9日、AMDのLisa Su CEOはYahoo Financeとのインタビューにおいて、OpenAIとの大規模なAIインフラ構築パートナーシップに触れる中で、2026年にリリースを予定する「Instinct MI450」が2nmプロセス技術を採用する事実を明言した。 「我々はMI450世代に非常に興奮している。これには2nm技術、すなわち最も先進的な製造能力が投入される」とSu博士は語り、AMDが最先端の半導体プロセスをAIアクセラレータ市場へ積極的に投入する姿勢を明確にした。

この発表は、OpenAIがAMDのInstinctアクセラレータを用いて数ギガワット規模のAIインフラを構築するという巨大契約の文脈で語られたものであり、単なる技術ロードマップの更新以上の意味を持つ。 NVIDIAのCUDAエコシステムが市場を席巻する中、ハードウェアの性能、特にプロセス技術における優位性を確立することは、AMDが市場シェアを奪うための極めて重要な戦略的布石となる。

NVIDIAの次世代アーキテクチャ「Rubin」はTSMCの3nmプロセス(N3P)を採用すると見られており、AMDがMI450の核心部に2nmプロセスを採用することで、少なくとも1世代分のプロセス・アドバンテージを握る可能性がある。 このプロセスノードの差が、性能と電力効率にどのような影響を与えるのかが、今後の技術競争の焦点となる。

Instinct MI450のハイブリッド・プロセスアーキテクチャ

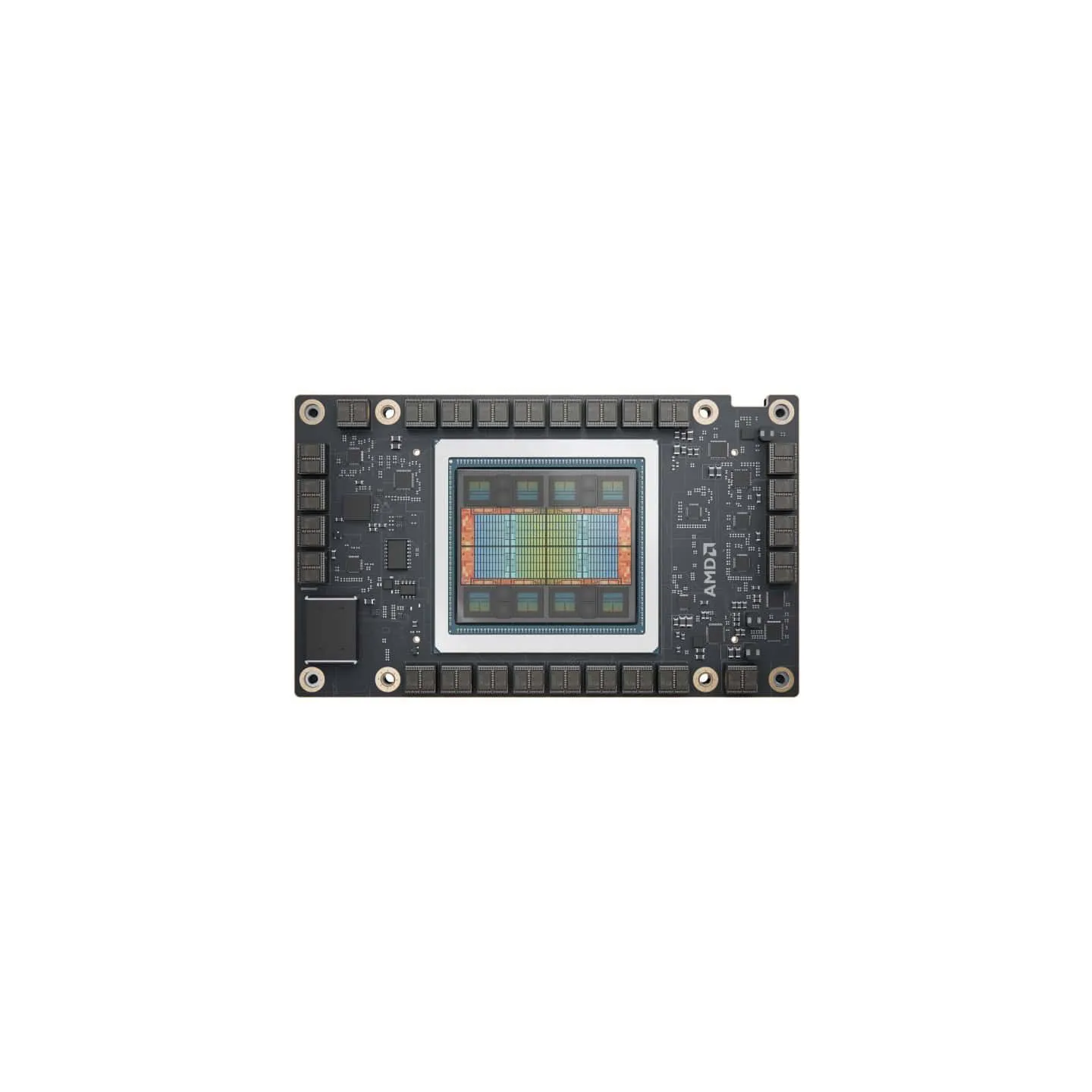

MI450が2nmプロセスを採用するという事実は、それ自体が大きなニュースであるが、その技術的な内実はより複雑かつ戦略的である。著名なリーカーであるKepler_L2氏によってもたらされた情報によれば、MI450は単一の2nmチップで構成されるのではなく、異なるプロセスノードで製造された複数のダイ(チップレット)を組み合わせた、洗練されたマルチチップモジュール(MCM)となる見込みだ。

なぜ全てのダイが2nmではないのか? チップレット戦略の成熟

リーク情報によると、MI450の内部構成は以下のようになると予測されている。

- Accelerator Core Die (XCD): TSMC N2P (2nm) プロセスで製造。AIの行列演算や浮動小数点演算を担う計算の心臓部。

- Active Interposer Die (AID): TSMC N3P (3nm) プロセスで製造。複数のXCDや後述のMIDを接続するための高密度配線層を持つアクティブなダイ。

- Media Interface Die (MID): TSMC N3P (3nm) プロセスで製造。HBMメモリや外部インターコネクト(例: Infinity Fabric)とのインターフェースを担うI/Oダイ。

このハイブリッド構成は、AMDが長年培ってきたチップレット設計思想の成熟を明確に示している。すべてのコンポーネントを最先端の2nmプロセスで製造することは、技術的にも経済的にも非効率である。2nmのような最先端プロセスは、トランジスタ密度と電力効率の恩恵が最も大きいロジック回路(=計算コア)に適用するのが合理的だ。一方で、I/O回路やアナログ回路は、プロセスの微細化による恩恵が比較的小さく、むしろ成熟したプロセスで製造する方がコスト、歩留まり、設計の安定性の面で有利となる場合が多い。

この設計選択の背景には、以下の技術的・経済的合理性が存在すると推察される。

- コストとリスクの最適化: TSMCの2nmプロセスは、製造コストが極めて高く、初期の歩留まりも不安定である可能性が高い。計算能力に直結するXCDにのみ2nmプロセスを適用し、比較的ダイサイズの大きいAIDやMIDに、より成熟しコスト効率の高い3nmプロセス(N3P)を用いることで、製品全体のコストを抑制し、製造リスクを分散している。

- Time-to-Marketの短縮: 異なる機能を持つダイを並行して開発・検証できるチップレット設計は、巨大なモノリシックチップを設計するよりも開発期間を短縮できる。特に、実績のあるI/O設計を流用しやすいMIDなどは、開発を加速させる上で有利である。

- 性能のスケーラビリティ: AIDを介して複数のXCDを接続する構成は、将来的にXCDの数を増減させることで、製品ラインナップを柔軟にスケールさせる道を開く。これは、NVIDIAもBlackwellアーキテクチャで採用している、現代のハイエンドGPU設計における主流アプローチである。

このアーキテクチャは、最先端プロセスの恩恵を最大化しつつ、そのリスクとコストを巧みに管理する、極めて現実的かつ高度なエンジニアリングの結晶である。

2nmプロセス(TSMC N2P)がもたらす技術的アドバンテージ

MI450の計算能力を支えるXCDに採用されるTSMCの2nmプロセス(N2P)は、AI/HPCの性能を飛躍させる可能性を秘めている。TSMCによれば、N2Pは先行するN3Pノードに対して、同一消費電力で10-15%の性能向上、または同一性能で25-30%の消費電力削減を実現するとされる。

このプロセス微細化がもたらすアドバンテージは、主に以下の2点に集約される。

- トランジスタ密度の向上: より多くのトランジスタを同一面積に集積できるため、演算器(ALU)の数やキャッシュ容量を増大させることが可能になる。これは、アクセラレータの理論性能(TFLOPS)の向上に直結する。

- 電力効率の改善: トランジスタのスイッチングに必要なエネルギーが減少するため、同じ計算を行う際の消費電力が低下する。これは、データセンターにおける総所有コスト(TCO)の重要な要素である電力コストと冷却コストの削減に貢献する。結果として、電力効率の指標である性能/ワット(TFLOPS/W)が大幅に向上する。

この2nmプロセスの採用は、AMDがNVIDIA Rubinに対して、特に電力効率の面で明確な優位性を築くための強力な武器となる可能性がある。

NVIDIA Rubin世代との技術比較と市場への影響

AMD Instinct MI450の登場は、NVIDIAが支配してきたAIアクセラレータ市場に、本格的な技術競争をもたらす。

プロセスノードの直接対決:2nm vs 3nm

MI450のXCDが2nm、対するNVIDIA Rubinが3nmというプロセスノードの差は、マーケティング上も技術上も大きな意味を持つ。 しかし、プロセスノードの優位性が即座に製品全体の性能優位性に繋がるわけではない点には注意が必要である。最終的な性能は、マイクロアーキテクチャの設計、コンパイラの最適化、そして何よりもソフトウェアエコシステムとの統合度に大きく左右される。

NVIDIAがRubinで3nmを選択した背景には、TSMCにおける生産キャパシティの確保、Blackwellアーキテクチャからのスムーズな移行、そして最先端ノードのリスク回避といった戦略的な判断があったと推察される。AMDはプロセスノードで一歩先んじることで、特に性能対電力比で差別化を図り、市場に揺さぶりをかける狙いである。

メモリ帯域と容量:LLM時代のボトルネックへの挑戦

現代のAI、特に大規模言語モデル(LLM)の性能を左右するのは、計算能力(FLOPs)だけではない。巨大なモデルパラメータ(数百億~数兆)と中間生成データを格納するためのメモリ容量、そしてそれらを高速に演算コアへ供給するためのメモリ帯域が、深刻なボトルネックとなっている。

一部報道によれば、AMDはMI450において、競合に対して1.5倍のメモリ容量と帯域を目指しているとされる。 これを実現する鍵となるのが、次世代メモリ規格「HBM4」の採用である。HBM4は、HBM3eからさらにピンあたりのデータ転送速度とインターフェース幅を拡大し、スタックあたりの帯域幅を飛躍的に向上させると期待されている。MI450がHBM4を先行して採用し、NVIDIA Rubinを上回るメモリスペックを実現した場合、以下のような具体的な利点が生じる。

- 大規模モデルの効率的な実行: より巨大なLLMを、複数のGPUに分割(モデル並列)することなく、単一あるいはより少数のGPUで実行可能になる。これにより、GPU間の通信オーバーヘッドが削減され、推論レイテンシや学習スループットが向上する。

- 推論スループットの向上: バッチサイズを大きく取ることが可能になり、単位時間あたりに処理できるリクエスト数が増加する。これは、AIサービスの提供コストに直接影響する。

MI450がプロセス技術の優位性に加え、メモリシステムでも優位性を確立できれば、NVIDIAにとって真に脅威となる存在となりうる。

ソフトウェアエコシステムと今後の展望

ROCmエコシステムの課題とOpenAIとの連携の意義

これまでAMDのAIアクセラレータがNVIDIAに大きく水をあけられてきた最大の要因は、ソフトウェアエコシステムにあった。NVIDIAのCUDAプラットフォームは、15年以上にわたる歴史の中で、膨大なライブラリ、開発ツール、そして開発者の知見を蓄積しており、その牙城を崩すことは容易ではない。

AMDのROCm(Radeon Open Compute platform)は、オープンソースとして開発が進められているが、安定性、機能性、対応フレームワークの広がりにおいて、依然としてCUDAに及ばないのが現状である。

しかし、今回のOpenAIとの大規模パートナーシップは、この状況を覆す転換点となる可能性がある。OpenAIが自社のモデル開発とサービス提供にAMD Instinctアクセラレータを本格採用することは、ROCmソフトウェアスタックに対する集中的な最適化とフィードバックを意味する。世界トップクラスのAI企業が深く関与することで、ドライバの安定性向上、重要なカーネルの性能最適化、主要なAIフレームワーク(PyTorch, TensorFlow)との統合強化が急速に進むと期待される。これは、ハードウェアの性能を最大限に引き出すための、最も効果的な処方箋と言えるだろう。

2026年に向けたAIアクセラレータ市場のロードマップ

AMDは、AIアクセラレータMI450だけでなく、次世代EPYCサーバープロセッサ「Venice」(Zen 6アーキテクチャ)にも2nmプロセスを採用する計画であり、データセンタープラットフォーム全体で技術的リーダーシップを狙っている。 CPUとGPUの両方で最先端プロセスを採用し、それらを独自の高速インターコネクト技術であるInfinity Fabricで緊密に連携させることで、AMDはNVIDIAだけでなくIntelに対しても強力な競争力を発揮しようとしている。

Instinct MI450の正式な製品発表は、2026年初頭のCESなどで行われる可能性がある。 MI450が公表通りの技術仕様で登場し、かつROCmエコシステムの成熟が順調に進めば、2026年以降のAI/HPC市場は、NVIDIA一強時代から、両雄が技術の粋を尽くして競い合う、よりダイナミックな時代へと移行するだろう。この競争は、最終的にAI技術の進歩を加速させ、我々ユーザーに多大な恩恵をもたらすに違いない。

Sources

- Yahoo Finance: AMD CEO talks OpenAI deal. Plus, how to play quantum stocks.