Intelは、International Solid-State Circuits Conference (ISSCC) 2025において、半導体製造における革新的な進歩を発表し、待望のIntel 18Aプロセステクノロジーの能力を明らかにした。SRAMビットセル密度の改善が特筆され、PowerViaシステムとRibbonFET (GAA) トランジスタの組み合わせが、Intelのこのノードの核となっている。

Intel、18AプロセスでSRAM密度を大幅に向上

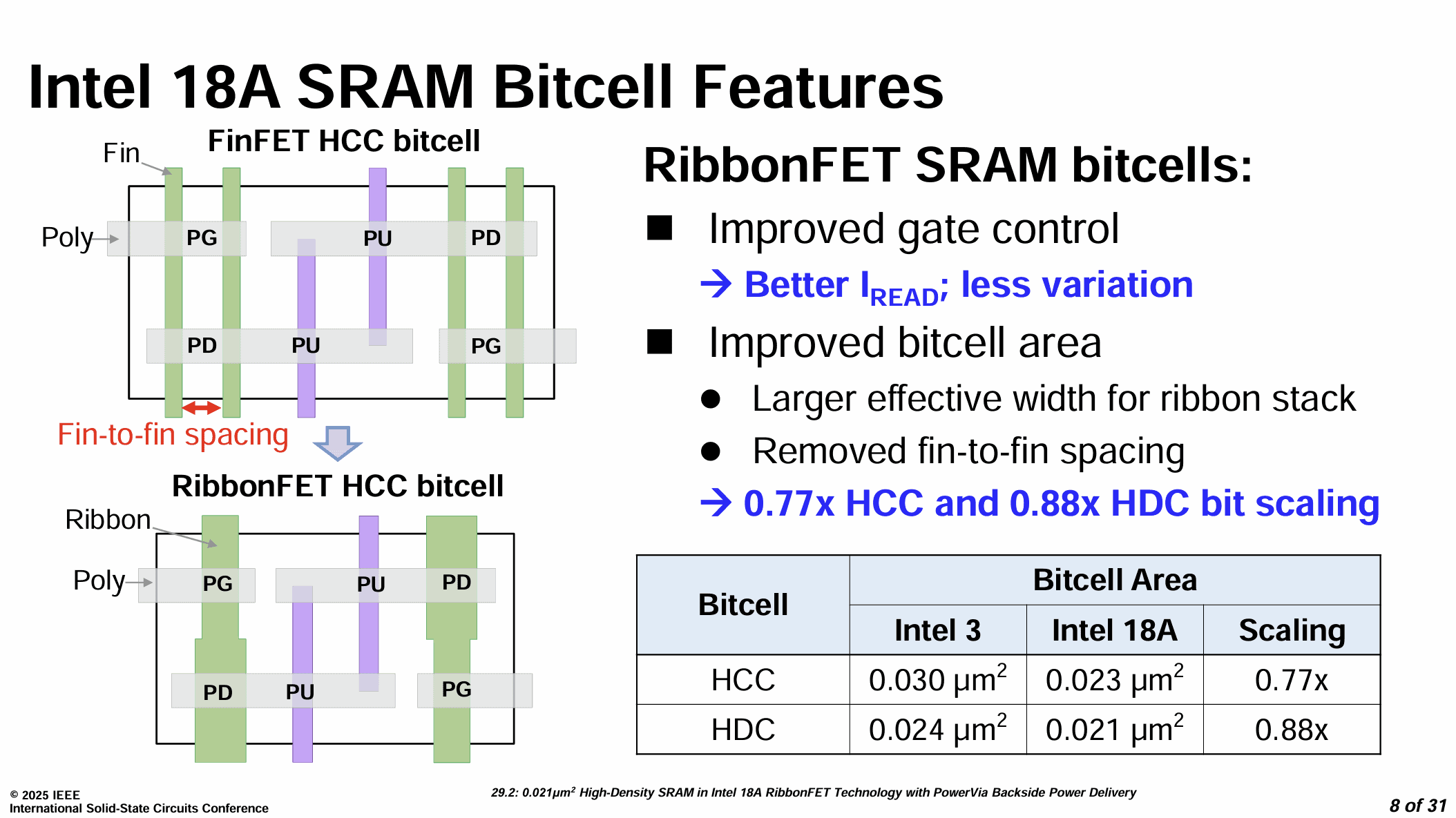

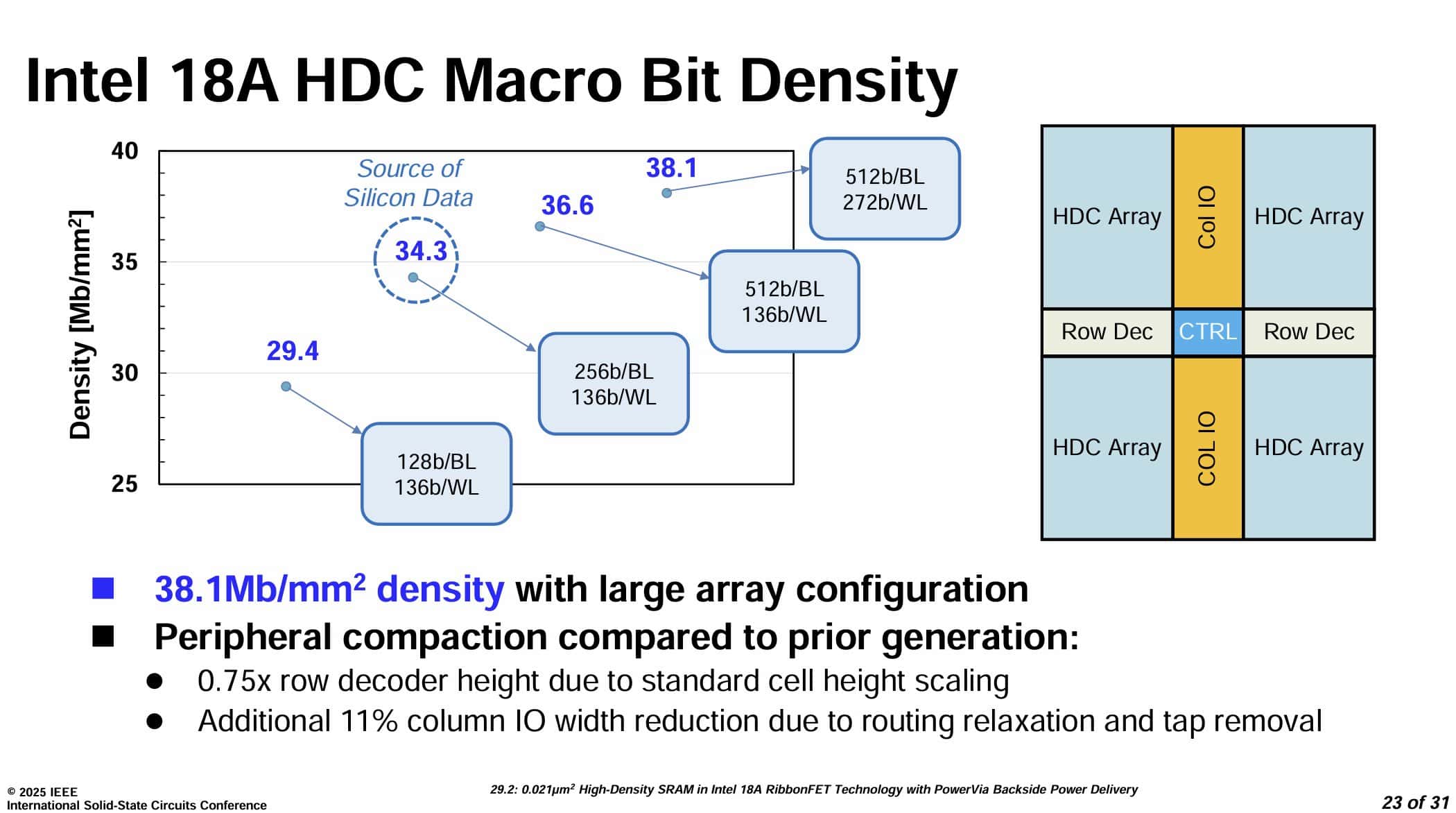

Intelは、高性能SRAMセルで目覚ましい進歩を遂げ、Intel 3の0.03 µm²からIntel 18Aでは0.023 µm²への縮小を達成した。高密度セルも同様の改善を示し、0.021 µm²に縮小された。これらの進歩は、それぞれ0.77倍と0.88倍のスケーリングファクターに相当し、かつてスケーリングの限界に達したと考えられていたSRAMテクノロジーにおける重要な成果である。

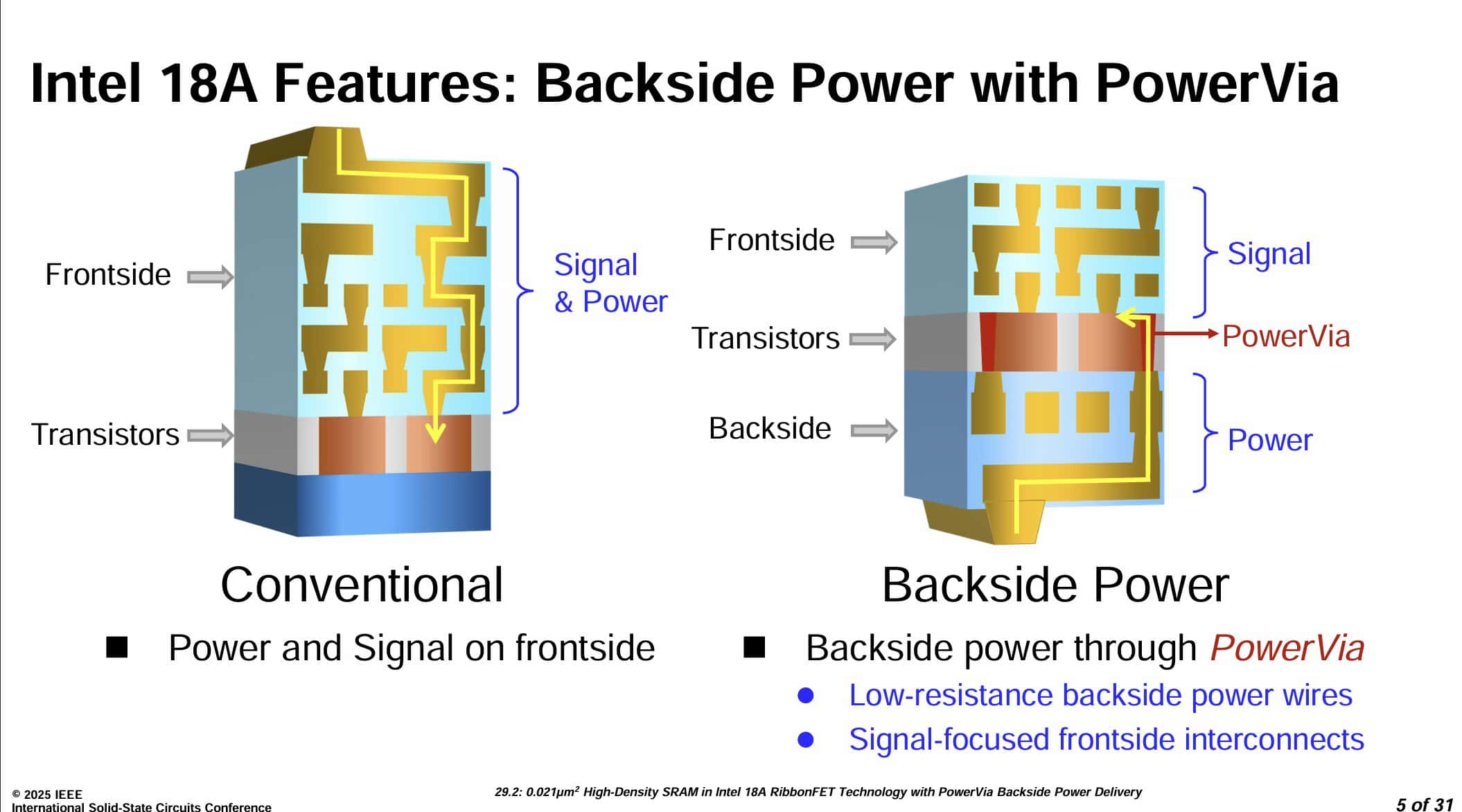

Intel 18Aの重要な特徴は、BSPDN (Backside Power Delivery Network) 、IntelではPowerViaと呼ばれる技術の採用である。これにより、電力供給プロセスをウェハーの背面に移動させ、電力効率と信号の完全性を向上させている。

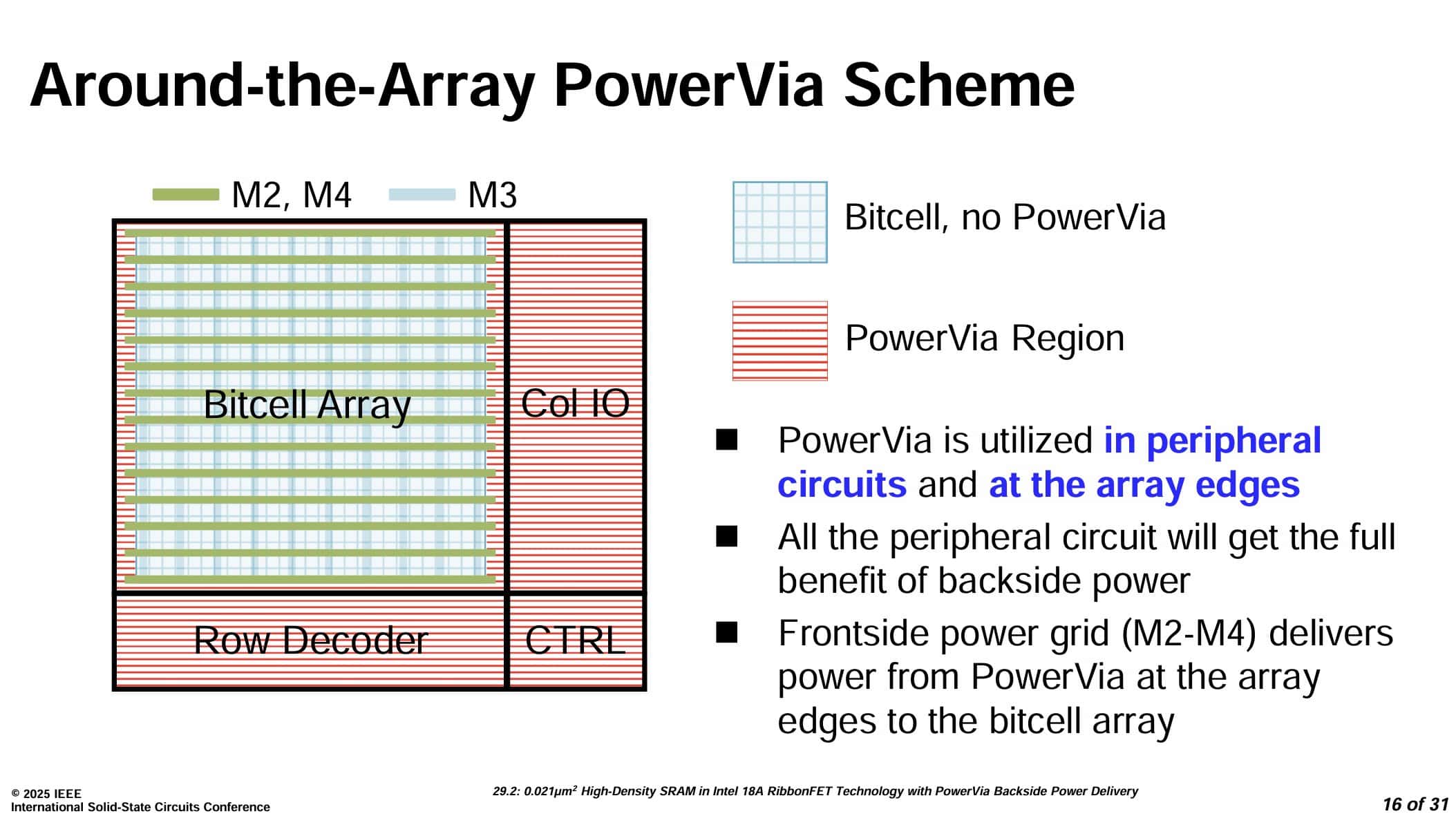

PowerViaテクノロジーは、電圧降下 (Vdroop) や干渉 (RC) の影響を受けやすいプロセッサのロジック領域で特に重要な役割を果たす。一方、SRAMビットセルでは、「アラウンド・ザ・アレイ」方式のPowerViaが採用され、ビットセル自体には背面電源供給は使用されず、I/O、制御、デコーダ要素にPowerViaが適用される。

Intel 18Aが達成した38.1 MBit/mm²のマクロビット密度は、同社を強力な競争力のある地位に位置づける。TSMCもN2プロセスで同等の数値を報告しているが、PowerViaとGAAトランジスタを組み合わせたIntel 18Aの包括的なアプローチは、TSMCやSamsungに挑戦する可能性があり、長期的にはNVIDIA、Apple、AMDといった現在TSMCがサービスを提供している主要顧客の獲得を目指している。

また、Intel 18Aは、GAA (Gate-All-Around) トランジスタ、IntelではRibbonFETと呼ばれる構造も採用。これにより、従来のFinFETトランジスタと比較して、より高い性能と電力効率が実現する。

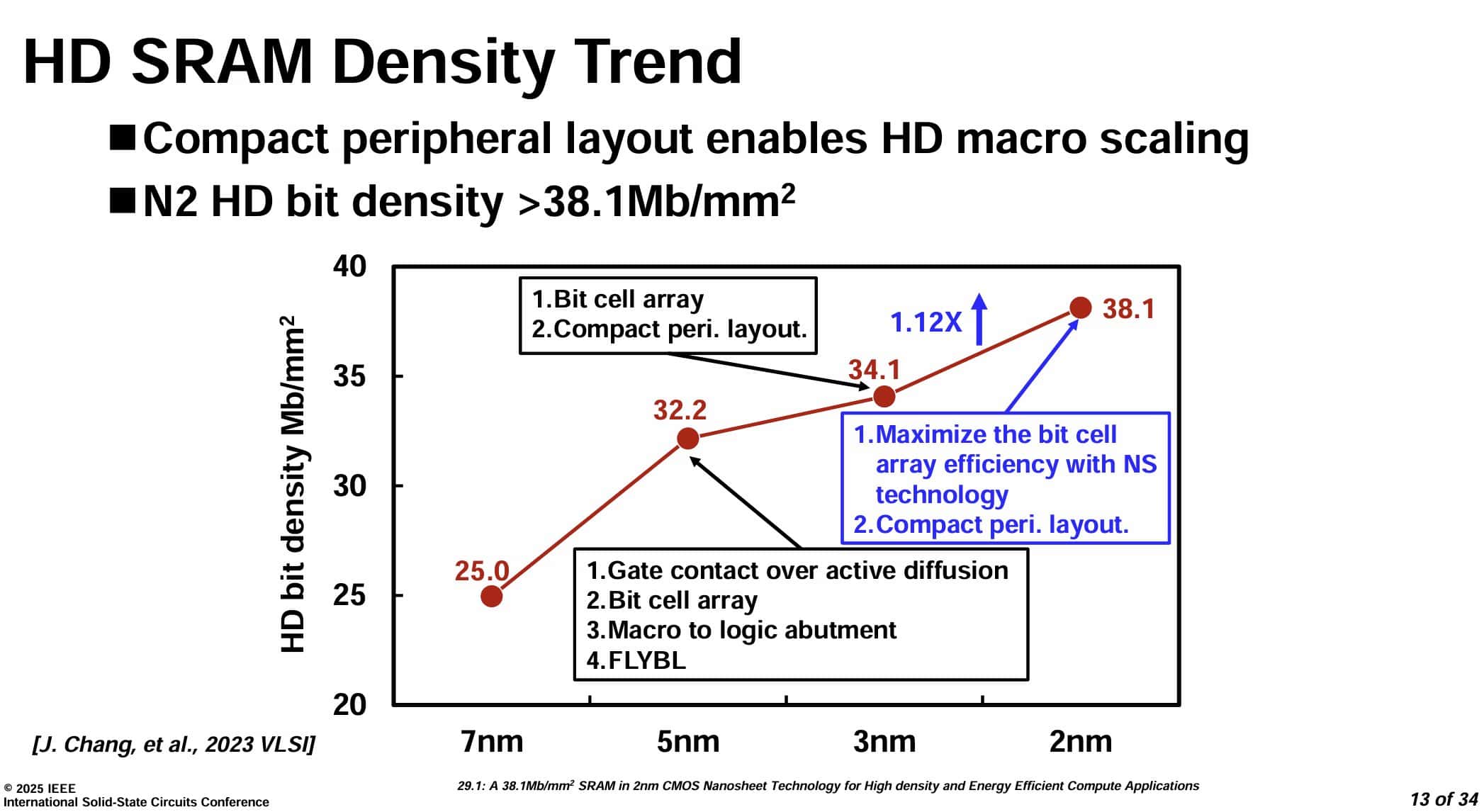

TSMCもN2プロセスの詳細を発表

TSMCもISSCCで、N2プロセスのHDマクロセルのスケーリングに関する数値を発表。TSMCは、38.1 MBit/mm²以上の値を達成すると述べており、Intelが示した値と一致している。これは、TSMCがより高い数値を達成する意欲を示すとともに、競合他社に対して潜在能力を完全には開示していないことを示唆している。

TSMCのN2プロセスは、GAAテクノロジーの統合によりSRAM密度が12%向上し、高性能SRAMでは18%の改善が見られるとのことだ。N2の主な改善点は、従来のFinFETテクノロジーから専用のN2「ナノシート」への移行であり、FinFET実装と比較して、より多くのプロセスカスタマイズと、より正確な制御が可能になった点である。

Intel従業員の懸念と期待

Tom’s Hardwareは、IntelのプリンシパルエンジニアであるJoseph Bonetti氏が、LinkedInへの投稿(現在は削除)で、Intelがプロセス技術のリーダーシップを取り戻し、今後数年間でファブレスチップメーカーの顧客を獲得しようとしているため、TSMCにIntelの製造の制御を譲渡することは逆効果であると述べたと報じている。

Bonetti氏は、Intelが半導体製造において大きな進歩を遂げていると主張。Intelの最新の製造プロセスであるIntel 3は、すでにXeon 6データセンタープロセッサの製造に使用されており、次世代のIntel 18Aは完成に近づいており、今年後半にクライアントPC向けのPanther Lakeプロセッサの製造に使用される予定である。一方、TSMCの同等のプロセス技術であるN2 (2nmクラス) は、2025年後半に量産段階に入る予定だ。

XenoSpectrum’s Take

Intelの18Aプロセスは、SRAM密度においてTSMCのN2プロセスに匹敵するという報告は、半導体業界における競争の激化を予感させる。IntelがPowerViaやRibbonFETといった革新的な技術を積極的に導入していることは、同社が製造プロセス技術のリーダーシップを取り戻そうとする強い意志を示している。

しかし、技術的な優位性だけでなく、実際のチップ生産における歩留まり率が、Intelの今後の成功を左右する重要な要素となるだろう。また、MicrosoftやAmazonといった初期の顧客獲得は有望であるが、より多くの主要顧客を獲得できるかが、Intel Foundry Services (IFS) の将来を決定づけることになる。

TSMCとの競争は今後も激化するだろうが、Intelが技術革新と顧客獲得に成功すれば、半導体業界の勢力図が塗り替わる可能性も秘めていると言えるだろう。

Sources