MITの研究チームが、シリコンウェハー基盤を必要としない革新的な3D積層チップの製造技術を開発した。Nature誌に発表されたこの研究成果は、AIハードウェアの性能を飛躍的に向上させる可能性を秘めており、現代のスーパーコンピュータに匹敵する処理能力を持つラップトップや携帯機器の実現に道を開くものとされている。

従来の限界を突破する新技術

半導体業界は長年、単一平面上へのトランジスタの集積度を高めることで性能向上を図ってきたが、物理的な限界に直面している。この課題を克服するため、MITのJeehwan Kim准教授が率いる研究チームは、「平面から高層ビルへ」という発想の転換により、半導体素子を垂直方向に積層する革新的なアプローチを実現した。

従来の半導体製造では、高品質な単結晶半導体素子を形成するために、シリコンウェハーを基板として使用することが不可欠とされてきた。この厚いシリコン基板は各層間に存在する「床」のような役割を果たすが、同時に層間の通信を遅延させる要因ともなっていた。研究チームが開発した新技術は、このシリコンウェハー基板を完全に排除することで、半導体層同士のより直接的な接続を可能にした。

特筆すべきは、この新技術が摂氏380度という低温環境下でも、高品質な単結晶半導体材料の形成を実現した点である。従来の手法では摂氏900度程度の高温が必要とされ、この高温処理が下層の回路を損傷させる原因となっていた。しかし新技術では、摂氏400度以下という低温での製造を可能にすることで、下層の回路機能を維持したまま、複数の半導体層を効率的に積層できるようになった。

金属工学からヒントを得た革新的手法

研究チームが直面した最大の技術的課題は、摂氏400度以下という低温環境下で、いかにして高品質な単結晶半導体材料を形成するかという点だった。この課題を解決するためのヒントは、意外にも金属工学の分野から得られた。金属の製造過程において、溶融金属が型に注がれる際の結晶化プロセスに着目したのだ。

金属工学の分野では、溶融金属が冷却される過程で「核生成」と呼ばれる現象が発生する。この過程で金属は徐々に結晶粒を形成し、それらが成長・融合することで規則的なパターンを持つ結晶となる。特に重要な知見は、この核生成が型の縁部分で最も容易に、かつ少ないエネルギーで発生するという点だった。Jeehwan Kim准教授は、「縁での核生成はより少ないエネルギーと熱しか必要としないことが知られています。この概念を将来のAIハードウェアに活用することにしました」と説明している。

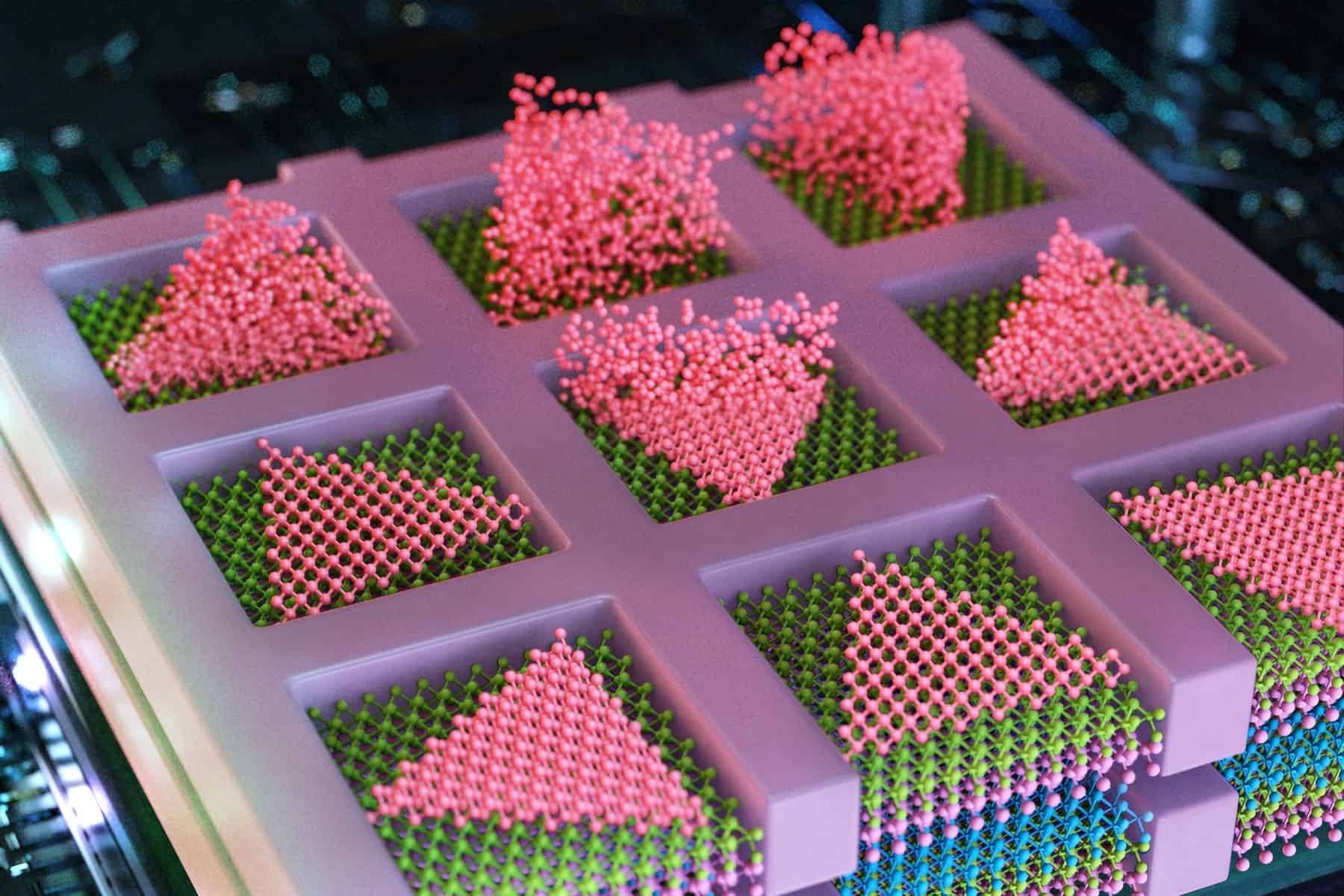

この技術の有効性を実証するため、研究チームは二種類のTMD材料を用いた多層チップの製造実験を行った。n型トランジスタ用の二硫化モリブデンとp型トランジスタ用の二セレン化タングステンを交互に積層し、これら異なる材料の単結晶を、中間のシリコンウェハーを必要とせずに直接積層することに成功した。

AIハードウェアの未来を切り開く

この革新的な3D積層技術は、AIハードウェアの性能向上に関して極めて重要な転換点となる可能性を秘めている。従来のチップ設計では、物理的な制約により演算処理能力とメモリ容量の拡張に限界があったが、新技術はこの壁を突破する可能性を示している。研究チームは、この技術を用いることで、現代のデータセンターに匹敵する記憶容量と、スーパーコンピュータ級の演算処理能力を持つチップを、ラップトップや携帯機器に搭載可能なサイズで実現できると考えている。

特に注目すべきは、この技術がAIの演算処理に必要な論理回路層とメモリ層を効率的に組み合わせられる点である。Jeehwan Kim准教授の説明によれば、新しい成長ベースのモノリシック3D方式を用いることで、数十から数百にも及ぶ論理回路層とメモリ層を直接積層することが可能となる。さらに重要な点は、これらの層が効率的に相互通信できる構造を実現できることである。

実用化に向けた取り組みも既に始まっている。Kim准教授は研究成果の商業化を目指し、FS2(Future Semiconductor 2D materials)を設立した。この研究は米国空軍科学研究局とSamsungの先端技術研究所からの支援を受けており、産学官による協力体制のもとで進められている。半導体業界の巨人であるSamsungの関与は、この技術の実用化に向けた強い期待を示すものと言える。

論文

参考文献

コメント