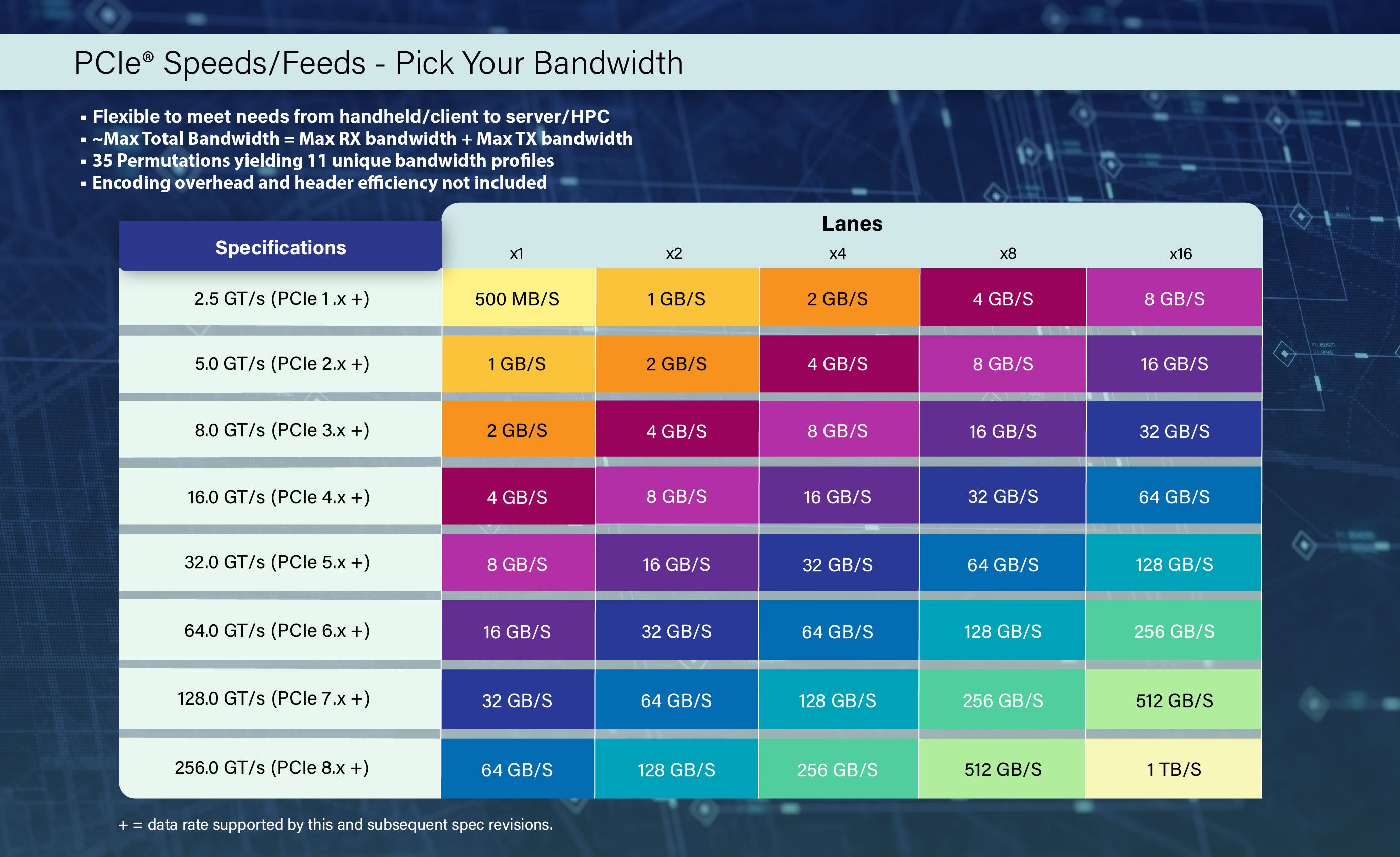

PCI-SIGは、次世代インターコネクト規格「PCI Express 8.0」の仕様策定を開始したと発表した。2028年の仕様リリースを目指し、生データレート256.0 GT/s(ギガトランスファー/秒)、x16構成で1TB/sという驚異的な双方向帯域幅を掲げる。これはAI/MLが牽引するデータ爆発時代への必然的な回答だが、その実現には物理法則との熾烈な戦いが控えている。

加速するAI需要が生んだテラバイト級インターコネクト

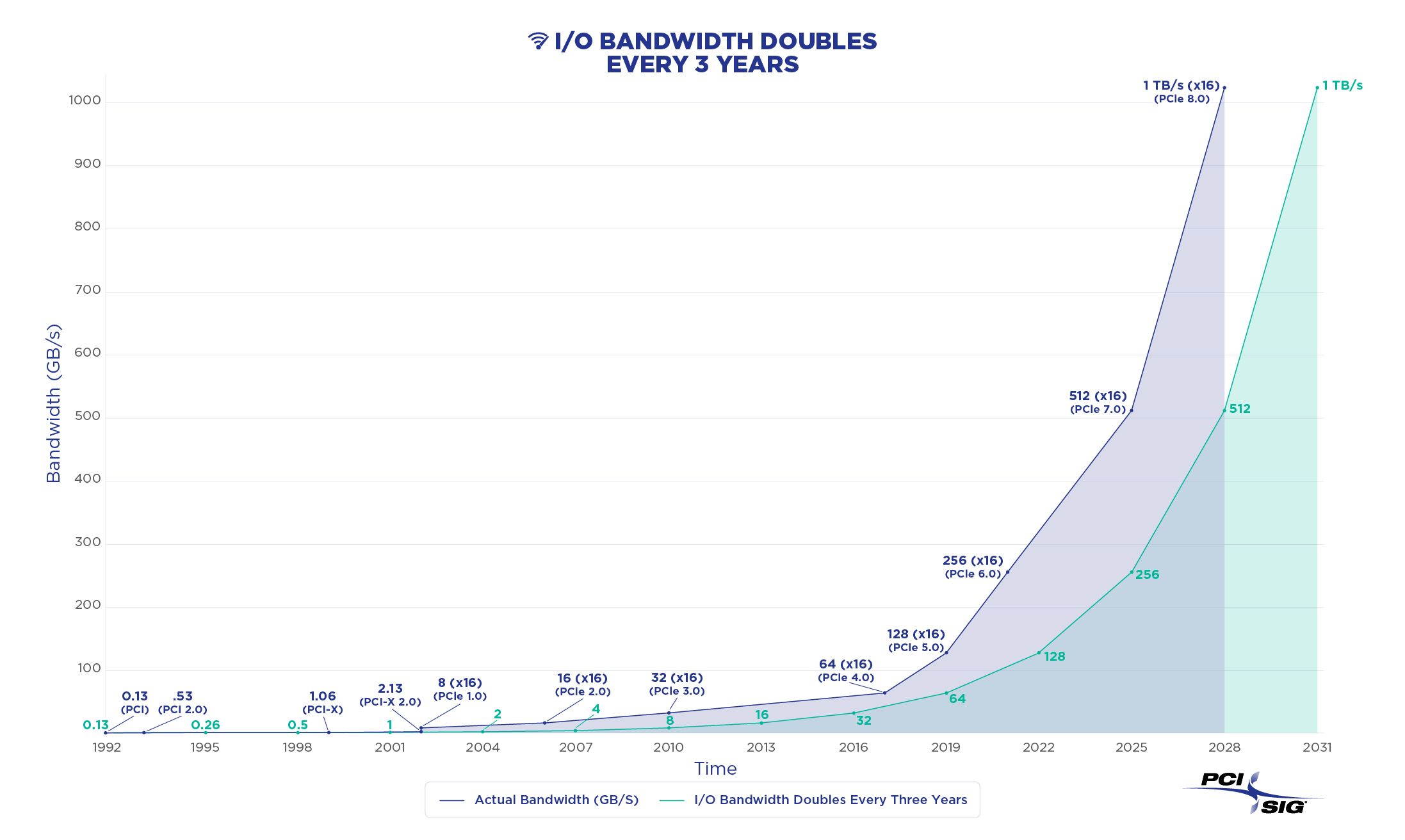

PCI-SIGが約3年周期で帯域幅を倍増させてきたロードマップは、もはや業界の定速巡航とも言える。PCIe 6.0(64 GT/s)が市場に出始め、PCIe 7.0(128 GT/s)の仕様が固まった直後に、次なるPCIe 8.0(256 GT/s)の目標が示されたのは当然の流れだ。

この飽くなき帯域追求の原動力は、言うまでもなくAI/MLとHPCである。巨大化する言語モデル、数兆パラメータへの道筋は、個々のアクセラレータ(GPU/NPU)の演算性能だけでなく、それらを繋ぐインターコネクトの帯域とレイテンシによって厳しく律速される。以前より、GPU間のデータ転送は常にボトルネックであり、NVLinkのような専用インターコネクトがその解の一つだった。PCIe 8.0が目指す1TB/sという領域は、まさにこのスケールアウトAIクラスタの根幹を、オープンスタンダードで支えようという野心的な試みだ。

GoogleがTPUで採用したような超広帯域のチップ間インターコネクトが、今やサーバーラック全体、さらにはデータセンター規模で求められている。PCIe 8.0は、その要求に応えるための重要なマイルストーンだ。

256GT/s実現への物理的課題とアーキテクチャの進化

PCIe 8.0の256.0 GT/sという転送速度は、物理層における極めて高度な技術的挑戦を意味するものだ。その実現のためには、銅配線の限界に挑み、信号伝送の物理層からプロトコル層に至るまで、抜本的な技術革新を要求する。

信号減衰とPAM4の先にあるもの

PCIe 6.0で導入されたPAM4(Pulse Amplitude Modulation with 4 levels)は、従来のNRZ(Non-Return-to-Zero)に比べ、同じ周波数で2倍のデータを伝送できる画期的な技術だ。これにより、信号周波数の急激な上昇を抑えつつ、帯域を稼ぐことが可能になった。PCIe 7.0もこのPAM4を継承する。

しかし、PCIe 8.0で256GT/sを達成するには、PAM4を維持したままクロックをさらに引き上げる必要がある。これは、信号の減衰(Insertion Loss)という物理的な壁との直接対決を意味する。高周波信号は、プリント基板(PCB)の銅配線を伝わるうちに急激にエネルギーを失う。数センチの配線が、もはや長距離伝送路と化すのだ。

この課題に対処するためには、以下のようなアプローチが考えられる。

- 超低損失基板材料: 現在のハイエンドサーバーで使われるMegtron 6やTachyon 100Gといった材料よりもさらに低損失な次世代材料が必須となる。

- リタイマ(Retimer)の多用: 信号を途中で受信・増幅・再送出するリタイマチップの配置が不可欠になるが、これはコストとレイテンシ、消費電力の増大に直結する。

- 配線長の極端な制約: CPUやアクセラレータからPCIeスロットまでの配線長が極めて短く制限され、マザーボード設計の自由度を著しく損なう可能性がある。

FECの進化とレイテンシのトレードオフ

PAM4は信号レベルが4値あるためノイズに弱く、ビットエラーレート(BER)が悪化しやすい。これを補うのがFEC(前方誤り訂正)である。PCIe 6.0では、レイテンシへの影響を最小限に抑えた軽量なFECが採用された。

しかし、256GT/sの世界では、信号品質はさらに劣化するため、より強力なFECが必要になる可能性が高い。問題は、強力なFECほど符号化・復号化の処理が複雑になり、レイテンシを増大させるという根本的なトレードオフが存在することだ。CXL(Compute Express Link)のようなプロトコルがPCIeの物理層上でキャッシュコヒーレンシを実現しようとしている現在、この付加レイテンシはシステム全体の性能に致命的な影響を与えかねない。PCI-SIGのワーキンググループは、このレイテンシ目標をいかに達成するか、極めて困難な最適化を迫られることになる。

「新コネクタ技術」が示唆する光I/Oへの道

今回の発表で最も注目すべき一文は、技術目標に「新しいコネクタ技術のレビュー(Reviewing new connector technology)」が明記されたことだ。これは、長年使われてきたCEM(Card Electromechanical)コネクタが、ついに物理的な限界を迎えることを示唆している。

PCI-SIG technical workgroups will be developing the PCIe 8.0 specification with the following feature objectives: … Reviewing new connector technology

この一文に、業界関係者は固唾を飲んだはずだ。銅線(カッパー)による伝送は、PCIe 8.0が最後の世代になるかもしれない。次なる選択肢として最も有力なのが、光I/O(Optical I/O)である。シリコンフォトニクス技術の成熟により、Co-Packaged Optics(CPO)のように、プロセッサパッケージのすぐそばに光の送受信機を実装するアプローチが現実味を帯びている。PCIe 8.0世代では、銅線と光I/Oが共存し、将来的には完全に光へ移行するロードマップが描かれる可能性が高い。

実用化への現実的考察

PCIe 8.0の仕様が2028年にリリースされるとして、搭載製品が市場に登場するのは2030年以降と見るのが妥当だろう。まず導入されるのは、間違いなくAIアクセラレータやHPC、ハイパースケールデータセンター向けの機器だ。Micronが初のPCIe 6.0対応SSD「9650」をデータセンター向けに出荷開始したように、最先端技術は常にエンタープライズ市場から浸透する。

コンシューマ向けのPC、特に自作PC市場のユーザーがその恩恵を享受するには、さらに数年を要する。その頃には、現在のGeForce RTX 4090が要求する帯域(PCIe 4.0 x16で64GB/s)が、いかに控えめなものだったかを実感することになるだろう。1TB/sという帯域は、GPUやSSDコントローラの消費電力と発熱を劇的に増大させる。単にスロットに挿すだけでなく、マザーボード全体の電源供給能力や熱設計が、これまで以上にシステムの安定性を左右する時代が到来する。

PCIe 8.0は、単なる高速化ではない。それは銅配線の限界を突破し、サーバーアーキテクチャを再定義し、そして最終的には光の時代へと導く、コンピュータ史における重要な転換点なのである。

Sources