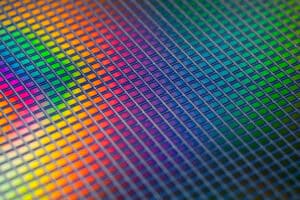

電子系設計自動化 (EDA)ツールの開発で有名なSynopsysは、Samsung Foundryの2nm「SF2プロセス」に対応した設計フローツールおよびIPの準備が完了したと発表した。これに先立ち、Samsungは同社の半導体製造プロセスのロードマップを更新し、2025年の2nmチップ量産開始を明らかにしていた。

FinFETからGAAへの移行を支援

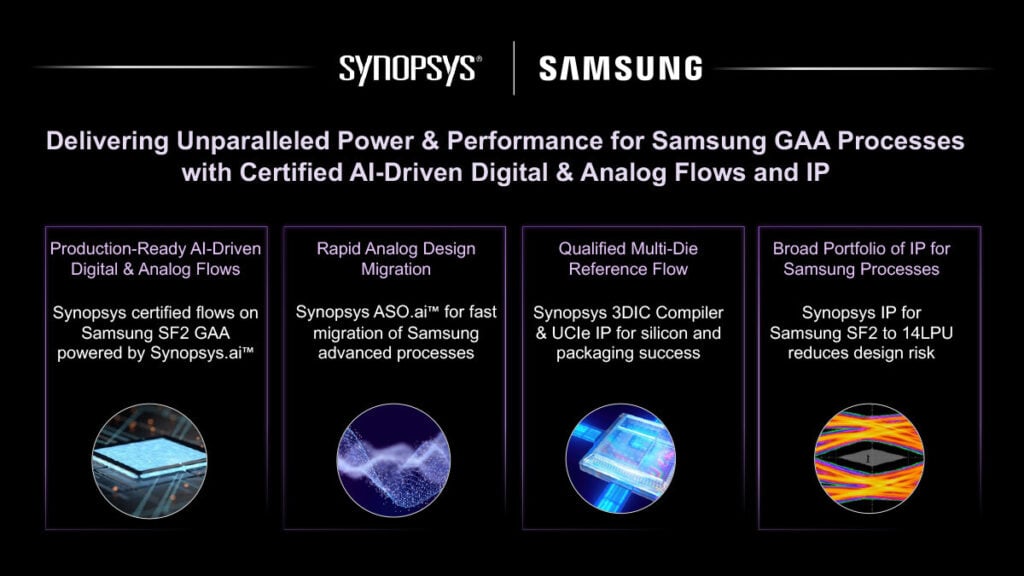

Synopsysのフルスタック電子設計自動化(EDA)スイート「Synopsys.ai」は、Samsung Foundryの2nm Gate All Around (GAA)プロセスノードにおけるアナログ設計の移行、PPA(性能、消費電力、面積)、および生産性を向上させる。Samsung SF2プロセスは、SynopsysのAI駆動の設計技術最適化(DTCO)ソリューションを用いて最適化され、AIを使用しない場合と比べて著しく優れたPPAを実現したという。この成功を基に、同じ最適化技術がSamsungの1.4nmプロセス「SF1.4」にも適用される予定である。

「広範なエコシステムの連携が必要とされる知能が普及する時代において、カスタムSoCの需要が高まっています。この連携は、顧客がSamsungのSF2および次世代SF1.4プロセスでのイノベーションとシリコンの成功を加速させるのを支援するために重要です。認証取得と、Synopsys.aiにより強化されたデジタルおよびアナログフローの複数の成功したテープアウトの達成は、デザイナーが市場投入までの時間を短縮するための信頼できる道を提供します」と、SynopsysのEDAグループのプロダクトマネジメントおよび戦略担当副社長であるSanjay Bali氏は述べている。

Synopsys DSO.aiツールは設計生産性とPPA最適化のために使用され、Synopsys ASO.aiはアナログ設計の移行を迅速化するために使用される。これらのプロセスは、設計をFinFETからGAAアーキテクチャに移行するために適用されており、クライアントは8nm(またはそれ以前)のFinFETプロセスで使用されたチップ設計を新しい2nm GAAプロセスに移行することができる。

チップ設計企業は、Synopsysのツールを使用して、SF2プロセスでの効率と性能を向上させるために、バックサイド電力ルーティング、ローカルレイアウト効果対応の手法、およびナノシートセル設計などの新しいチップ設計技術を開発することができる。Samsung FoundryのSF2Zプロセスノードは、性能、消費電力、および面積をさらに20%向上させることができる。

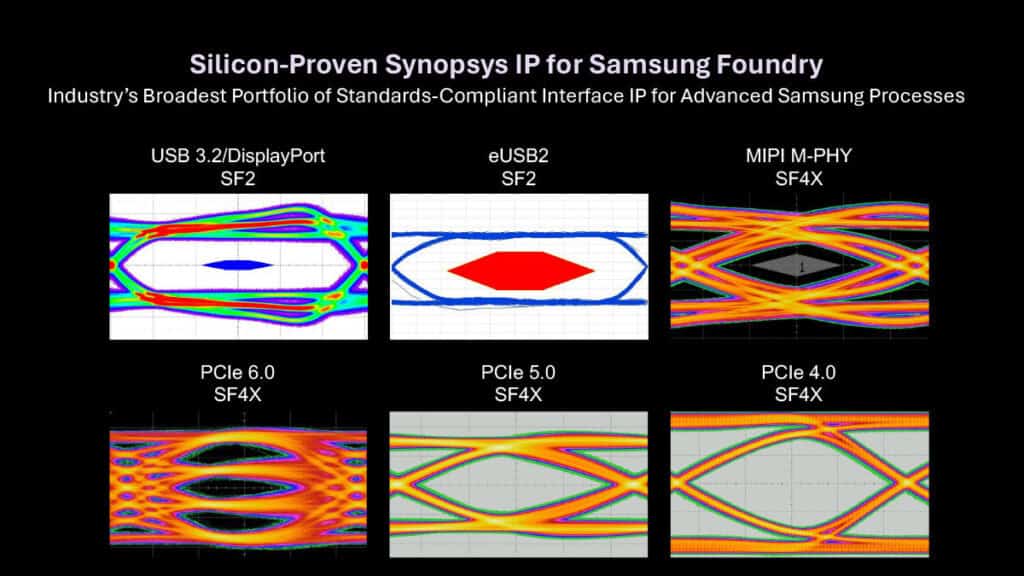

Synopsys UCIe IPは、SF2およびSF4xプロセスを使用してチップレットをマルチダイパッケージに迅速に統合するために使用されており、SF5Aプロセスでは遅延、電力、およびダイ間接続も改善されている。Synopsysの3DIC Compilerは、2.5Dおよび3D異種統合および先進的なパッケージングに使用できるとのことだ。

Source

コメント