PCI-SIGは2025年9月、次世代インターコネクト規格「PCI Express 8.0」の仕様バージョン0.3をメンバー向けに公開した。これは2028年の正式リリースを目指す同規格の、最初の公式なレビュードラフトである。PCIe 8.0は、x16構成で最大1TB/sという驚異的な双方向帯域幅を目標に掲げており、このドラフト公開は、AIやハイパフォーマンスコンピューティング(HPC)が要求するデータ転送能力の指数関数的な増大に応えるための、具体的な技術的道筋が示されたことを意味する。本稿では、このv0.3ドラフトの技術的詳細を深掘りし、1TB/sという帯域がもたらすインパクトと、それを実現するための物理層の挑戦について見ていきたい。

PCI Expressの進化:帯域倍増の歴史とその役割

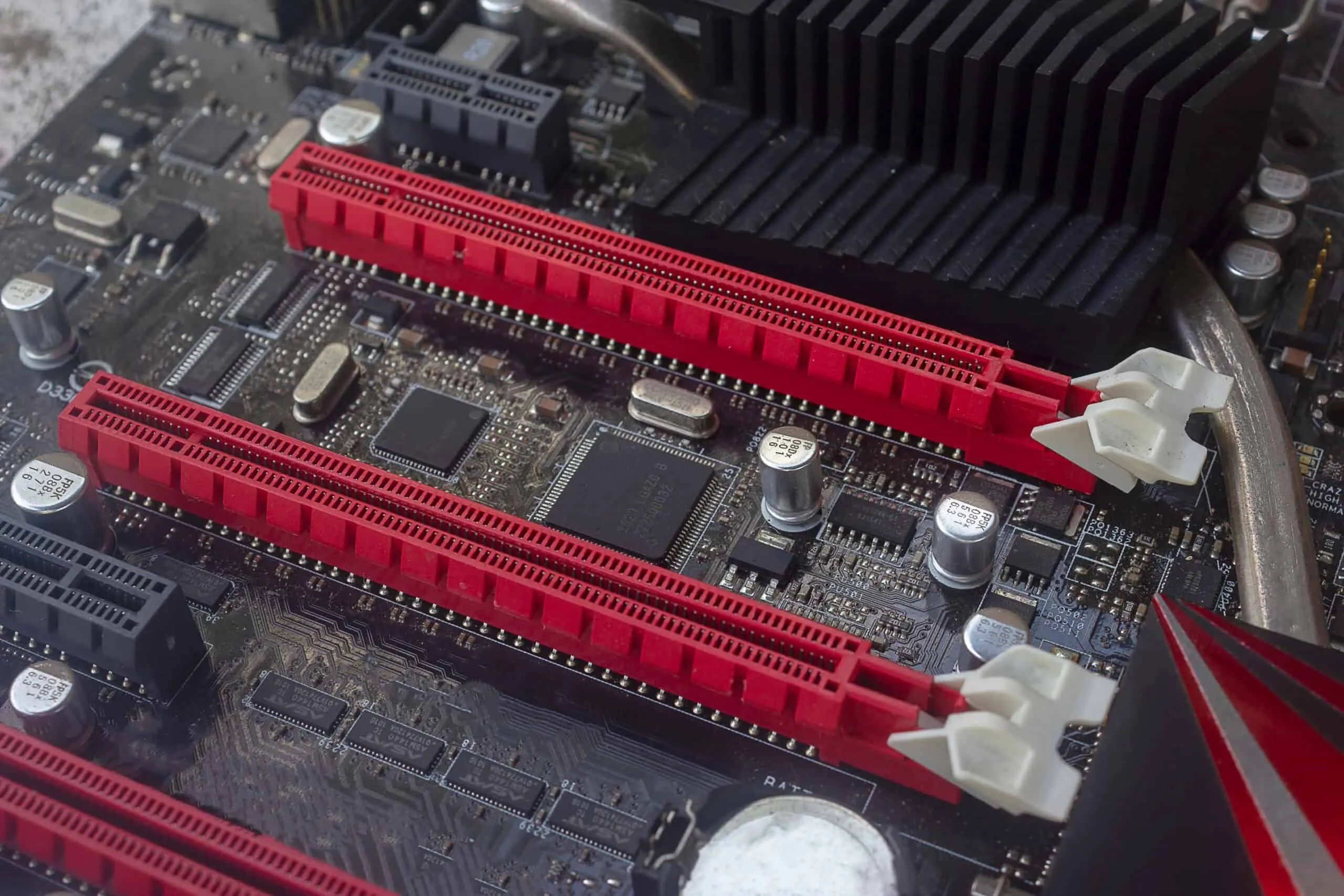

PCI Express (Peripheral Component Interconnect Express、以下PCIe) は、コンピュータ内部でCPUと各種コンポーネント(GPU、SSD、ネットワークカードなど)を接続するための標準的な高速シリアルインターフェースだ。その最大の責務は、データ転送のボトルネックを解消し、システム全体の性能を最大化することにある。

PCIeの歴史は、約3〜4年ごとに帯域幅を倍増させてきた歴史でもある。この予測可能で安定した進化が、周辺機器メーカーやソフトウェア開発者に明確なロードマップを与え、エコシステム全体の発展を支えてきた。

| 規格 | 転送速度 (per lane) | x16帯域幅 (片方向) | 主な登場時期 |

|---|---|---|---|

| PCIe 1.0 | 2.5 GT/s | ~4 GB/s | 2003年 |

| PCIe 2.0 | 5.0 GT/s | ~8 GB/s | 2007年 |

| PCIe 3.0 | 8.0 GT/s | ~16 GB/s | 2010年 |

| PCIe 4.0 | 16.0 GT/s | ~32 GB/s | 2017年 |

| PCIe 5.0 | 32.0 GT/s | ~64 GB/s | 2019年 |

| PCIe 6.0 | 64.0 GT/s | ~128 GB/s | 2022年 |

| PCIe 7.0 | 128.0 GT/s | ~256 GB/s | (2025年予定) |

| PCIe 8.0 | 256.0 GT/s | ~512 GB/s | (2028年目標) |

この表が示すように、PCIe 8.0が目指すx16での片方向約512 GB/s(双方向で約1TB/s)という帯域は、現在主流のPCIe 4.0の16倍、普及が始まったばかりのPCIe 5.0の8倍に相当する。この目標を達成するため、v0.3ドラフトでは具体的な技術仕様の骨子が示されている。

1TB/sを実現する物理層(PHY)の核心

帯域幅の倍増は、単にクロック周波数を上げれば済むという単純な問題ではない。特に256 GT/sという領域では、物理法則に根差した深刻なシグナルインテグリティ(信号忠実性)の問題が立ちはだかる。PCIe 8.0 v0.3ドラフトは、これらの課題に対する具体的なアプローチを示している。

転送速度 256.0 GT/sの意味と挑戦

仕様に記載されている「256.0 GT/s」は、Giga-transfers per secondの略であり、1秒間に2560億回の信号状態の切り替えが行われることを示す。これはデータの実効レート(GB/s)とは異なる。実際のデータ転送では、エラー訂正やクロック情報の埋め込みのためのエンコーディングによるオーバーヘッドが発生する。

PCIe 8.0は、PCIe 6.0/7.0から引き続きPAM4(4値パルス振幅変調)信号方式を採用する。PAM4は、従来のNRZ(Non-Return-to-Zero、2値)方式が1つの信号レベル(シンボル)で1ビット(0か1)の情報を伝達するのに対し、4つの異なる電圧レベル(00, 01, 10, 11)を用いて1シンボルで2ビットの情報を伝達する技術である。

- NRZ (PCIe 5.0まで): 1シンボル = 1ビット

- PAM4 (PCIe 6.0以降): 1シンボル = 2ビット

PAM4の採用により、信号の周波数を物理的に倍増させることなく、データ転送レートを2倍に引き上げることが可能となった。PCIe 8.0が256 GT/sを達成するにあたり、PCIe 7.0の128 GT/sから信号周波数を単純に倍増させると、信号の減衰やノイズ(特にクロストーク)が指数関数的に増大し、実用的な伝送距離を確保することが極めて困難になる。このため、PCIe 8.0でもPAM4を継続することは、物理的な実装の観点から合理的な選択である。

しかし、PAM4には大きな代償が伴う。4つの電圧レベル間の間隔(アイハイト)は、NRZの3分の1に狭まるため、ノイズに対する耐性が著しく低下する。これによりビットエラーレート(BER)が必然的に悪化するため、前方誤り訂正(FEC: Forward Error Correction)が必須となる。

FEC(前方誤り訂正)とレイテンシの精緻なバランス

FECは、データ送信時に冗長な誤り訂正符号を付加し、受信側でデータ中のエラーを検出・訂正する技術である。PCIe 6.0以降、FECはプロトコルに不可欠な要素として統合された。

PCIe 8.0では、さらに高速化する信号に伴い、より強力なFECアルゴリズムが求められる可能性がある。しかし、強力なFECは、エンコードとデコードの処理が複雑化し、レイテンシ(遅延)の増大を招く。これは、帯域幅と同じくらい、あるいはそれ以上にレイテンシが重要となるHPCや金融取引などのアプリケーションにとっては致命的な問題となりうる。

v0.3ドラフトで「レイテンシとFECターゲットの達成を確認する」という目標が掲げられているのは、このトレードオフを強く意識していることの表れである。技術的な観点からは、低レイテンシを維持しつつ、256 GT/sで要求されるBERを達成できる、軽量かつ高効率なFECの実装が最大の課題の一つとなる。このバランスをいかに取るかが、PCIe 8.0の性能特性を決定づける重要な要素となるだろう。

物理層を超えて:コネクタとプロトコルの進化

1TB/sという帯域を実用化するためには、信号方式だけでなく、物理的な接続媒体であるコネクタや、データを効率的に流すためのプロトコル層の進化も不可欠である。

新しいコネクタ技術と光インターコネクトの可能性

256 GT/sもの超高速信号をマザーボード上の銅配線(カッパー)で安定して伝送することは、極めて高い技術的ハードルを伴う。信号の挿入損失、反射、クロストークといった問題がより深刻化し、従来のPCIeコネクタ(CEMコネクタ)では性能限界に達する可能性が高い。

このため、v0.3ドラフトでは「新しいコネクタ技術のレビュー」が明確な目標として挙げられている。これは、インピーダンス整合をより厳密に行い、信号の減衰を最小限に抑える新しいコネクタ設計や、ケーブルソリューションの検討を示唆している。

さらに長期的な視点では、光インターコネクトの導入が視野に入る。光ファイバーは銅線に比べて以下の点で圧倒的に優れている。

- 低損失: 長距離にわたって信号の減衰が少ない。

- 広帯域: より高い周波数の信号を伝送可能。

- EMI耐性: 電磁干渉の影響を受けない。

これまで光接続はコストの高さからデータセンター内の長距離接続などに用途が限定されてきた。しかし、銅線での伝送が物理的な限界に近づくにつれ、チップ間やボード間といったより短い距離での光接続(Co-packaged Opticsなど)が現実的な選択肢として浮上する。PCIe 8.0の時代には、少なくともサーバー内部の特定用途で光接続が採用される可能性は十分に考えられる。

帯域効率を高めるプロトコル強化

PCIe 8.0は、物理的な帯域幅を増やすだけでなく、その帯域をいかに無駄なく使うかという「帯域効率」の向上も目指している。v0.3ドラフトの目標にある「帯域幅向上のためのプロトコル強化」は、この点に言及するものだ。

考えられる強化点としては、パケットのヘッダー構造を最適化してオーバーヘッドを削減することや、より高度なフローコントロールメカニズムの導入などが挙げられる。また、PCIe物理層上で動作するCXL (Compute Express Link)のような上位プロトコルとの連携をさらに深め、メモリセマンティクス(メモリとしての振る舞い)の転送効率を高める改良が含まれる可能性も推察される。

PCIe 8.0が解き放つ未来:AI、HPC、そして次世代コンピューティング

1TB/sという帯域は、もはやコンシューマ向けの一般的な用途を遥かに超えている。この規格が真価を発揮するのは、膨大なデータをリアルタイムで処理する必要がある、データセンターやスーパーコンピュータの世界である。

AI/MLアクセラレータのボトルネック解消

現代の大規模言語モデル(LLM)に代表されるAIの学習では、数千から数万個のGPUやAIアクセラレータを連携させて並列処理を行う。この際、アクセラレータ間のデータ通信速度がシステム全体の性能を決定づける最大のボトルネックとなる。

NVIDIAのNVLink/NVSwitchやAMDのInfinity Fabricといった専用インターコネクトがこの課題に対応しているが、PCIe 8.0は、標準規格として、異なるベンダーのアクセラレータを極めて広帯域で接続する基盤を提供する可能性がある。特に、複数のアクセラレータが巨大なメモリプールを共有するCXLとの組み合わせは、AIモデルのさらなる巨大化と複雑化を支える上で不可欠な技術となるだろう。

ヘテロジニアス・コンピューティングの加速

CPU、GPU、DPU、FPGAといった異なる種類のプロセッサを適材適所で活用するヘテロジニアス・コンピューティングは、性能と電力効率を両立させるための重要なアプローチである。PCIe 8.0とCXLは、これらの多様なプロセッサ群が、物理的に離れた場所にあるメモリに対して、あたかもローカルメモリであるかのように低遅延でアクセスすることを可能にする。これにより、真に統合された巨大なコンピューティング・リソースが実現され、これまで不可能だった規模の科学技術計算やデータ解析が可能になる。

2028年に向けた技術的マイルストーン

PCIe 8.0仕様バージョン0.3のリリースは、2028年の正式リリースに向けた重要なマイルストーンである。x16で1TB/sという目標は単なる数字の遊びではなく、次世代のAIおよびHPCインフラが直面するデータ転送のボトルネックを根本的に解決しようとする明確な意志の表れである。

PAM4信号の継続、FECとレイテンシの高度な最適化、そして新しいコネクタ技術や光接続の可能性。これらの技術的挑戦を乗り越える道のりは平坦ではない。しかし、このドラフトがPCI-SIGのメンバーに公開されたことで、半導体メーカー、機器ベンダー、システムインテグレーターは、次世代製品の設計を早期に開始できる。業界全体での協調とフィードバックを通じて仕様は磨き上げられ、我々のデジタル社会を支える新たなデータハイウェイが完成へと向かう。コンシューマ市場への直接的な影響は2030年代以降となるだろうが、その恩恵はクラウドサービスやAI技術の進化という形で、遠からず全ての人々にもたらされることになるだろう。

Sources