TSMCは昨年AppleのiPhone向けA17 Proチップや、Mac向けのM3チップで本格的に3nmプロセスの生産に乗り出したが、既にその先の2nmや1.4nmと言った次世代プロセスの開発を進めていることを明らかにしている。2nmプロセスの最初のチップは2025年の登場が明らかにされているが、今回DigiTimesによって、その先の1.4nmの具体的な時期についてが報じられている。

DigiTimesの新しいレポートによると、TSMCは2nmを2025年に、1.4nmを2027年頃に生産開始する予定だという。これらの最先端ノードは、これまでの全ての例にならい、Appleがその最初の顧客となる可能性が高いと見られる。

DigiTimesによると、TSMCは2nm試験生産を今年後半に開始し、2025年には量産体制に入るようだ。TSMCは最終的には2027年頃に1.4nmの生産を開始する予定だが、まだ2年以上先のスケジュールであることを考えると、これは変わる可能性もある。地政学的な影響も多分にあるだろう。特に近年の中国の台頭や台湾への圧力を考えれば、想定外の事態が生じる可能性もある。これには先日の台湾で起こった地震のような予期せぬ自然災害も含まれる。

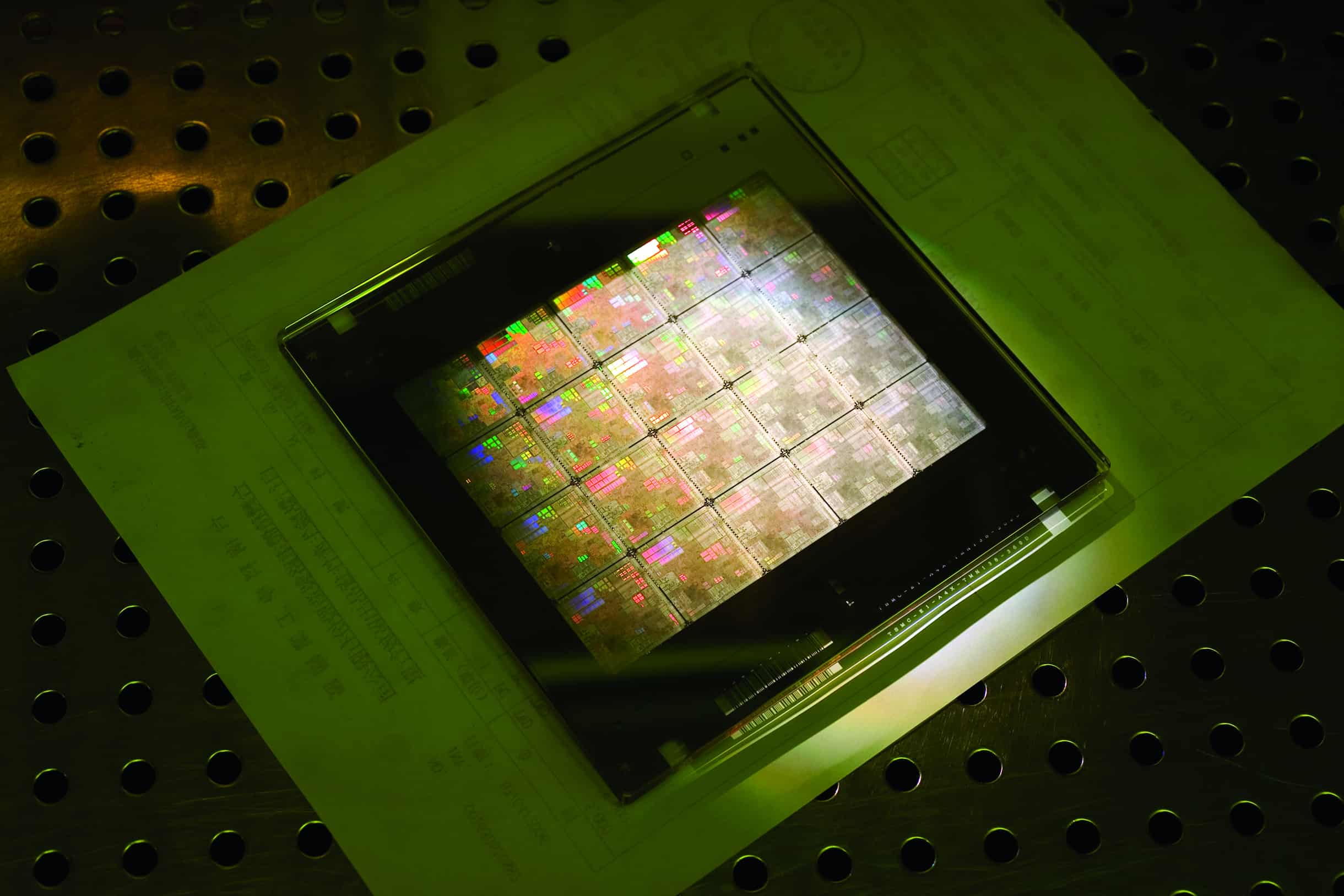

死者9人、負傷者1,000人以上を出した台湾で過去25年間で最大となった地震は、TSMCの2nm工場も直撃した。工場は水害に見舞われ、一部の設備は交換が必要になったという。この工場は現在、テスト用の少量のチップしか製造していない。

DigiTimesによると、すべてのプロセスサイズで失われたウェハーは 10,000 枚以下だとのことだ。

今回の地震により、台湾にあるTSMCの多数の工場で損傷したウェハーは10,000枚未満であるが、損害は保険でカバーされる。

AppleもTSMCもウェハー1枚当たりのチップ歩留まりを公表していないが、業界の推定によると、iPhone 15 Proモデルに搭載されているA17 Proと同サイズのチップの場合、歩留まりはウェハー1枚当たり440チップ程度になると思われる。これは、数十万チップ以上の損失はなく、すぐに埋め合わせが可能であることを示唆している。

TSMCがこうした自然災害や、地政学的リスクを軽減するためには戦略の転換が必要だ。例えば、同社は米国アリゾナ工場で2nmチップの一部を製造することを発表しており、これにより、アリゾナと台湾のファブで最先端チップの負担が分担される。これまで同社の最先端ノードは常に台湾にあったため、これはTSMCにとって大きな戦略の転換と言える。同社は2025年に最初の2nmウェハー(N2)を顧客に提供し、2026年にはN2Pと名付けられた強化版を提供すると報じられている。

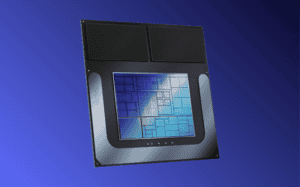

2nmへの移行はTSMCにとって大きな一歩となる。3nmまで採用されていたFinFETから、ゲート・オール・アラウンド(GAA)ナノシート・トランジスタに移行することになる。だが、TSMCによると、N2PまではBSPDN(裏面電力供給網)を追加しないようで、この点で今年のArrow Lake向けIntel 20Aプロセスでこの先端テクノロジーを導入すると予想されるIntelに少なくとも2年は遅れることになる。TSMCは、N2Pの後にN2Xと名付けられた3番目の2nmのバリエーションを追加する予定で、これは高性能コンピューティング・アプリケーション向けとなる。

このようなスケジュールと、今年後半からIntelがTSMCにかける圧力の高まりを考えると、TSMCがこれらの目標を達成できるかどうかが注目される。以前、TSMCは2nm生産を2026年に延期すると報じられた事もあったが、今回の報道では遅れを取り戻したようだ。

これまでTSMC、Samsungの後塵を拝していたIntelだが、2024年に2nmチップをリリースし、加えて世界初のHigh-NAリソグラフィ装置を稼働させ、2026年頃に1.4nmプロセスを実現する計画だ。これに対しTSMCは今のところLow-NAリソグラフィ装置に固執しており、2nm、1.4nm共にIntelから1~2年遅れになると見られる。2024年後半から2025年にかけての2社の戦いは激しさを増すことになりそうだ。

Sources

コメント