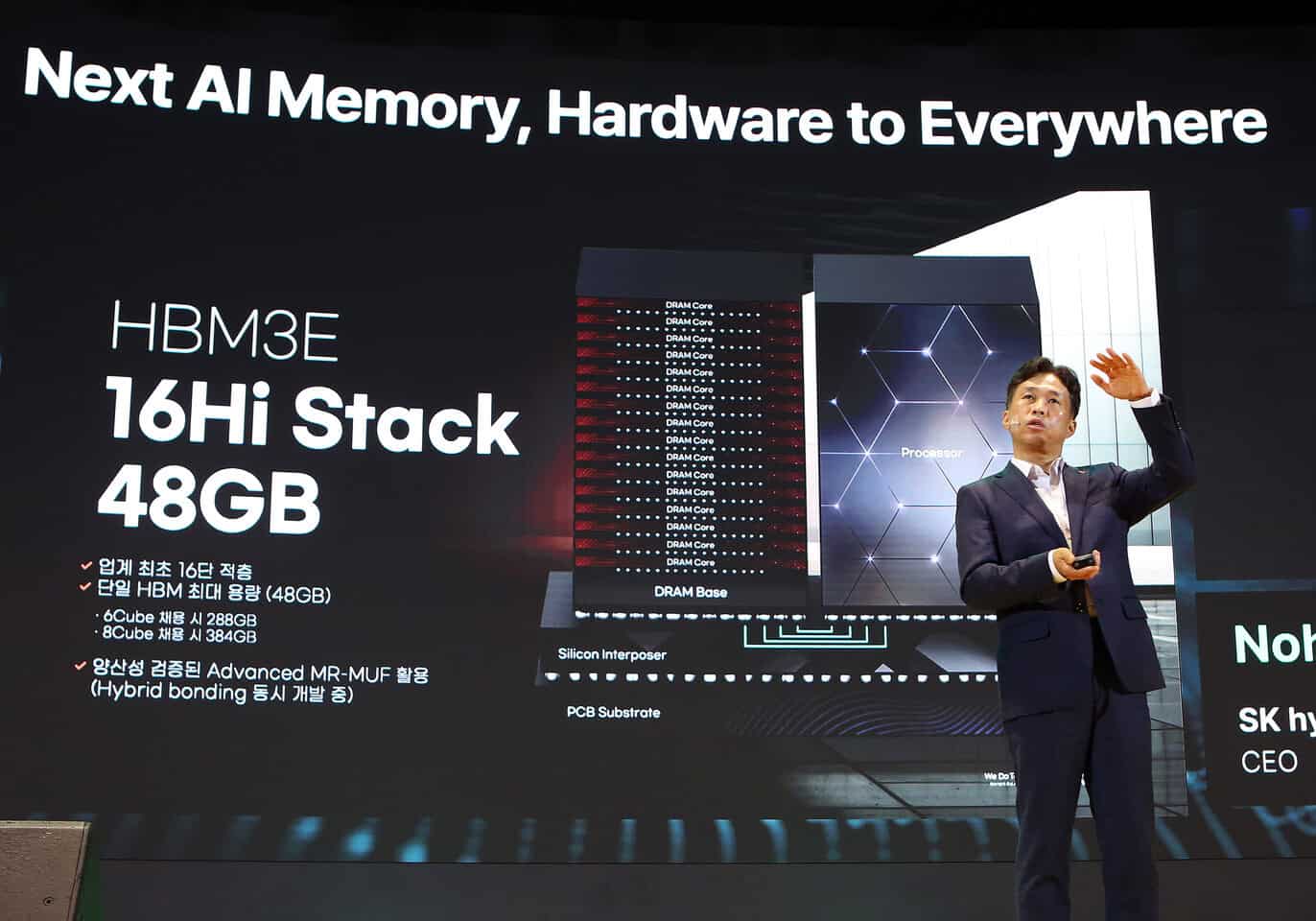

SK hynixは、世界初となる16層積層の「16-Hi HBM3E」メモリを開発したことを発表した。現行の12層製品から4層増やすことで、1スタックあたりの容量を36GBから48GBへと33%増加させることに成功している。同社CEOのKwak Noh-Jung氏が、ソウルで開催されたSK AIサミットの基調講演で明らかにした。

技術的ブレークスルーと性能向上

新開発の16-Hi HBM3Eは、同社の社内テストによると、AIトレーニングで18%、推論処理では32%の性能向上を達成しているという。この性能向上は、特にAI推論アクセラレータ市場の拡大が予想される中で、同社のAIメモリ分野におけるリーダーシップを強化するものとなる。

製造には「MR-MUF(mass reflow-molded underfill)」と呼ばれる技術が採用されている。この技術は、チップ間のバンプを溶解してチップを回路に接続するリフロープロセスと、チップ間およびバンプギャップに液状エポキシ成形コンパウンド(EMC)を充填する成形プロセスを組み合わせたものである。これにより、スタックの耐久性と放熱性が向上しているとのことだ。

次世代メモリ技術への展望

SK hynixは、2025年初頭から16-Hi HBM3Eのサンプル出荷を開始する予定だ。注目すべきは、16層積層技術が本来はHBM4世代から導入される予定だったものを、HBM3E世代で前倒しして実現した点である。これは技術的安定性の確保を目的としたものとされている。

また同社は、以下の次世代メモリ技術の開発も進めていることを明らかにした:

- PCおよびデータセンター向けLPCAMM2モジュール

- 1cnmプロセスベースのLPDDR5およびLPDDR6メモリ

- PCIe Gen 6 SSD

- 大容量QLCエンタープライズSSD

- UFS 5.0メモリ

- ベースダイにロジックプロセスを採用したHBM4チップ

Xenospectrum’s Take

SK hynixの16-Hi HBM3E開発は、AIワークロード向けメモリ需要の急増に対する戦略的な対応である。特に注目すべきは、HBM4世代で予定されていた16層積層技術をHBM3Eで実現した点だ。

既に報じたように、NVIDIAのJensen Huang氏はSK hynixに対し、HBM4チップを予定より6ヶ月早く納品するよう要請したことが、SKグループのChey Tae-won会長によって明らかにされた。同氏は、チップは2025年後半に納品されると述べているが、AI時代における半導体業界の急速な技術革新の一端を示すものと言えるだろう。

SamsungやMicronといった競合他社も同様の高容量HBM3E技術の開発を進めることが予想され、AI向けメモリ市場における競争は一層激化するものと考えられる。処理性能と電力効率の両立が求められる中、SK hynixのMR-MUF技術採用は、今後のAIメモリ開発の方向性を示す重要な指標となるだろう。

コメント