SK hynixが第6世代高帯域幅メモリ(HBM4)の製造プロセスを、当初計画していた5nmから最先端の3nmへと変更することを決定した。2025年後半からNVIDIAへの供給を開始する計画で、半導体業界における技術革新の加速を象徴する動きとなっている。

3nmプロセス採用の技術的意義

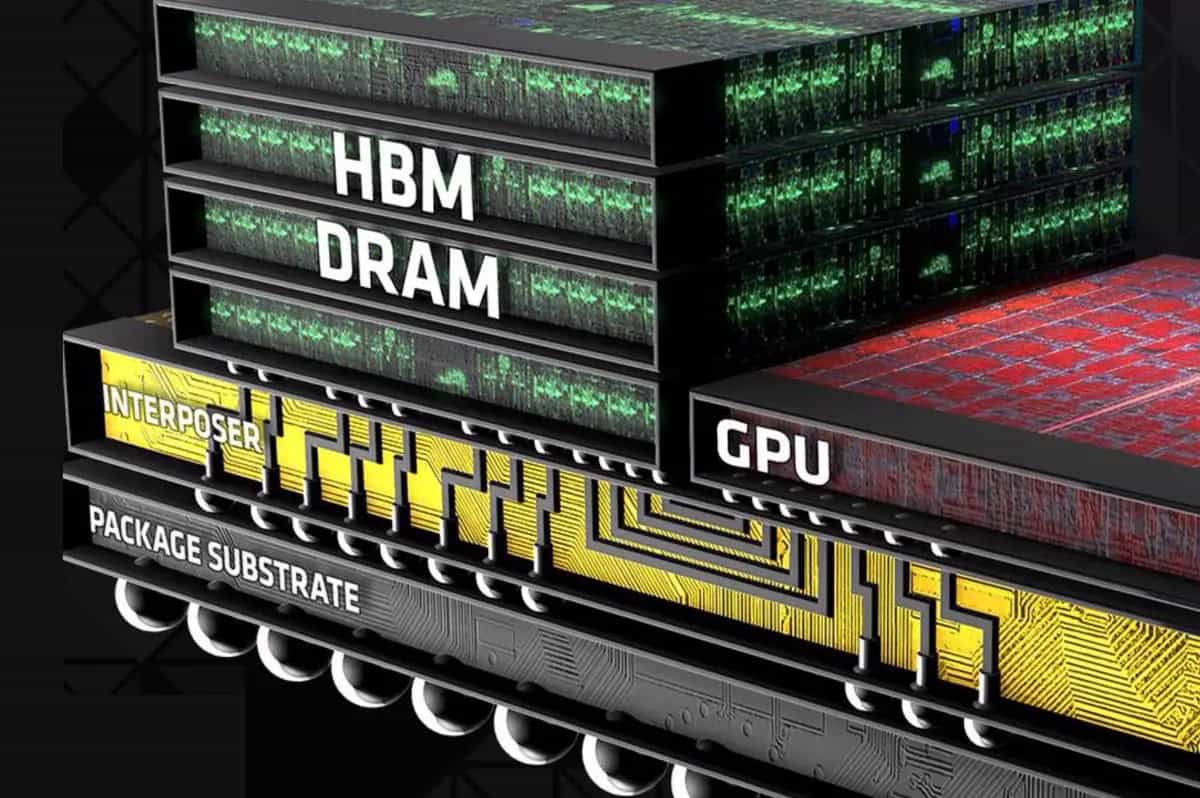

HBM4の製造における3nmプロセスへの移行は重要な技術革新と言えるだろう。ベースダイと呼ばれる制御部は、HBMチップの最下層に配置され、GPUとの接続を担う重要なコンポーネントとして機能する。このベースダイを3nmプロセスで製造することにより、5nmプロセス採用時と比較して20-30%の性能向上が実現される見込みだ。

この性能向上の本質は、微細化技術の進化にある。3nmプロセスでは、シリコン基板上に形成される回路の線幅がわずか3ナノメートル(10億分の3メートル)という極めて微細な寸法で製造される。これにより、同じ面積の基板により多くのトランジスタを搭載することが可能となり、演算処理能力の向上とエネルギー効率の改善が同時に達成される。

現在NVIDIAのGPU製品に使用されている4nmプロセスのHBMチップと比較しても、この3nmプロセスへの移行は大きな技術的飛躍を意味する。特に人工知能(AI)の演算処理において重要となるメモリ帯域幅とレイテンシの改善が期待される。TSMCの最先端製造プロセスを採用することで、現在AppleのiPhoneやMacBookに搭載されているチップと同等レベルの微細化技術を、高性能なHBMチップの製造にも適用することが可能となる。

さらに、この製造プロセスの微細化は、チップの発熱量の低減にも貢献する。回路間の距離が縮まることで、電子の移動距離が短くなり、その結果として消費電力が低減される。これは大規模なデータセンターにおける冷却コストの削減にも寄与する重要な要素となる。

一方で、3nmプロセスの採用には高度な製造技術と精密な品質管理が要求される。量子効果による干渉や、製造時の微細な欠陥が性能に与える影響が、より顕著になるためだ。SK hynixがTSMCとの協業を選択した背景には、このような技術的課題に対する戦略的な判断があったと考えられる。

市場戦略と業界への影響

SK hynixは現在、世界のHBM市場の約50%のシェアを占める最大手メーカーであり、その製品の大半をNVIDIAに供給している。3nmプロセス採用により、4nmプロセスでのHBM4製造を計画している競合のSamsung Electronicsとの技術格差をさらに広げることが予想される。

一般用途向けのHBM4およびHBM4Eについては、TSMCと協力して12nmプロセスを採用する方針。これはコスト効率を考慮した戦略的な判断とみられる。さらに、TeslaがSK hynixとSamsung ElectronicsにHBM4プロトタイプのサンプル提供を要請しており、新たな供給先としての可能性も浮上している。

Xenospectrum’s Take

HBM4への3nmプロセス採用は、地政学上の戦略的意義も持つことになる。米国の対中輸出規制強化に伴い、SK hynixがNVIDIA、Google、Microsoftといった米テック企業との関係強化にシフトする中、この決定は地政学的な産業再編の一端を示している。

NVIDIA CEOのJensen Huang氏がSKグループ会長のChey Tae-wonに12層HBM4チップの供給時期を6ヶ月前倒しするよう要請した事実は、AI市場における需要の逼迫と、半導体サプライチェーンの再構築が急ピッチで進んでいることを示唆している。皮肉なことに、技術覇権競争が、かつてない速度で技術革新を推し進めているようだ。

Sources

- The Korean Economic Daily: SK Hynix to produce HBM4 on 3 nm foundry process in 2025

コメント