AI向け半導体の需要が急膨張する中、チップの性能はいまや製造プロセスと並んで、パッケージング技術によっても左右される。複数のチップを1つのパッケージに集積する「先端パッケージング」技術が、AIインフラの競争を左右する要素に浮上した。

TSMCのパッケージング技術「CoWoS(Chip-on-Wafer-on-Substrate)」はNVIDIAの需要で逼迫し、代替を求める大手テック企業がIntelのEMIB(Embedded Multi-die Interconnect Bridge)に目を向け始めた。IntelのCFO David Zinsner氏は2026年3月、顧客が製造能力の「前払い」にまで応じる意向を明かした。コミットメントは「数十億ドル」規模に達する見込みで、IntelはEMIBパッケージングを財務再建の核に据えようとしている。顧客が前払いを申し出るまでになった背景は何か。

CoWoSのキャパシティはNVIDIAが60%を占有する

先端パッケージングは、NVIDIAがムーアの法則に頼らずGPU性能をスケールさせるために活用する技術だ。HBM(High Bandwidth Memory)などの異なるダイを1つのパッケージに統合することで、チップ間の帯域幅と電力効率を大幅に向上できる。

TSMCのCoWoSはこの用途で業界標準の地位を占めてきたが、現在は深刻な供給不足に陥っている。CoWoSの製造容量のうち、NVIDIAが約60%を占有しているためだ。他のAIアクセラレーター開発企業が同等の能力を持つサプライヤーを探しても、EMIBに匹敵するポートフォリオを持つ企業はほぼ存在しない。

地政学的なリスクも顧客の視野に入る。CoWoSは台湾のTSMCに集中しており、地政学的緊張が高まる局面で供給の一極集中に懸念を持つ企業が出始めている。地政学リスクを嫌う顧客にとってIntelの分散拠点は現実的な代替だ。

EMIBはインターポーザーなしでチップレットを接続する2017年生まれの技術だ

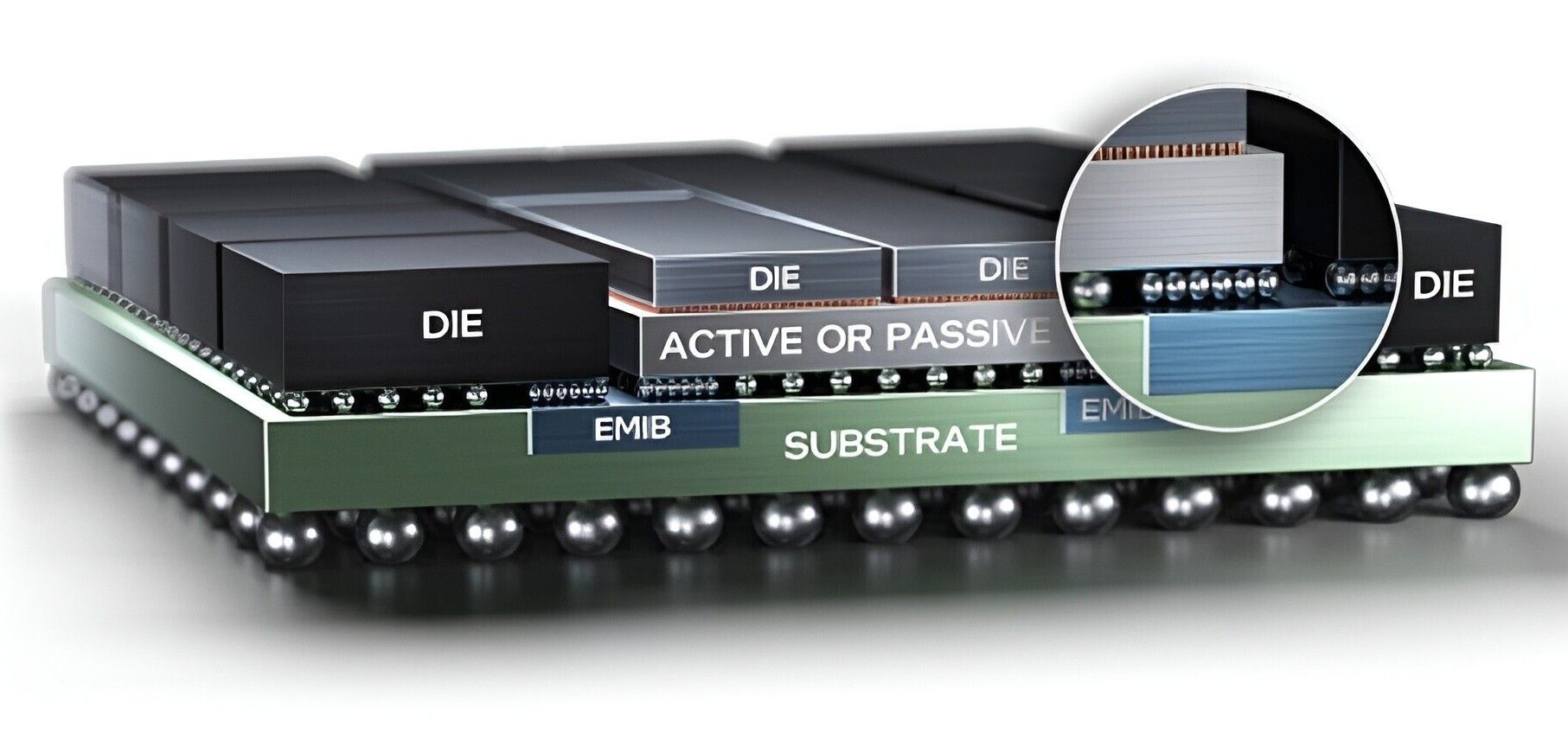

EMIBは2017年にIntelが導入した技術で、複数のチップレットを1つのパッケージに高密度に接続する。従来の大型シリコンインターポーザーを使わず、小型のシリコンブリッジを基板に埋め込む方式を採用している。インターポーザー全面を製造する場合と比べてコストと歩留まりの面で有利で、必要な部分だけに高密度配線を集中できる。

現行のEMIBに加え、TSV(Through-Silicon Via、シリコン貫通電極)を追加したEMIB-Tが2026〜2027年にかけて量産立ち上げの予定だ。垂直方向の接続密度が増すことで、より複雑な3D集積への対応が可能になる。

IntelはEMIBを自社製品の外にも開放し、外部企業向けパッケージングサービスとして提供するファウンドリービジネスを拡大している。GoogleやAmazonはこれを次世代ASIC製造の候補として検討中だ。

GoogleとAmazonがIntelのEMIBに交渉を進めている

WIREDは、GoogleとAmazonがそれぞれのASIC(特定用途向け集積回路)プロジェクト向けに、IntelのEMIBパッケージングサービスについて交渉中だと報じた。Googleについては次世代TPU(Tensor Processing Unit)へのEMIB採用が濃厚とTrendForceも伝えているが、いずれも現時点では交渉段階であり、採用が確定したわけではない。

CFO David ZinsnerはMorgan Stanleyのイベント(2026年3月5日)で、顧客が製造能力確保のために「prepay(前払い)」にまで応じる意向を語った。前払いの意向は、交渉が最終局面に入ったシグナルだ。

同イベントでZinsnerは「年間数十億ドル規模の案件クローズが近い」とも述べており、粗利益率は最大40%に達する可能性も示した。

「前払い」を申し出た顧客、CFOが語る10億ドル超のFoundry収益

Intelは2026年1月のQ4決算で、外部向けパッケージング収益の予想を「well north of $1 billion(10億ドルを大きく超える)」に上方修正した。外販収益は計画を上回るペースで拡大している。

Intel Foundryが公開した生涯契約見込み額は150億ドルを超え、正式な顧客コミットメントのタイムラインはH2 2026(2026年後半)に設定されている。次回決算発表は2026年4月23日で、具体的な顧客名や契約額の詳細が開示されるかどうかが注目される。

先端パッケージングは、CFOが示した粗利益率最大40%という数字が裏付ける通り、半導体ファウンドリーの中でも収益性が高いセグメントだ。チップ製造(ウエハープロセス)で台湾・韓国勢に後れをとるIntelにとって、パッケージングで高付加価値のポジションを確保することは収益構造の改善に直結する。

垂直統合を捨て外部委託へ:Amkor Songdo施設でのEMIB製造

Intelはこれまで自社のパッケージング製造を内製化していたが、韓国・Songdo(松島)のAmkor K5施設でEMIBの製造を委託することを決定した。Intelにとって初めての外部委託となる。

Amkorへの委託は地理的な分散という観点でも効果がある。米国・欧州・アジアに製造拠点を持つAmkorのネットワークを活用することで、TSMCの台湾集中とは異なるサプライチェーンの選択肢を顧客に提供できる。

長年堅持してきた垂直統合モデルを崩し、製造の一部を外部に委ねる方針に転換した。Intelは垂直統合モデルの限界を認め、顧客需要に応えるためにAmkorへの委託という実利を取った。

12倍レティクルのコンセプトが示す、EMIBの次のステージ

Intelはチップレット接続のさらなる高密度化に向け、12倍レティクルスケーリングのコンセプトを発表している。ただし現時点はコンセプト段階であり、確定したロードマップではない。量産化の時期や具体的なスペックは未定だ。

EMIB-Tの2026〜2027年量産立ち上げと合わせて見ると、IntelはEMIBプラットフォームを段階的に高度化しながら、顧客の将来需要にも対応しようとしている。GoogleやAmazonのような次世代AIアクセラレーター開発企業が長期的なパートナーシップを検討する際に、この技術ロードマップは判断の根拠になる。

EMIBが広く普及すれば、AIインフラの地理的・組織的な多極化が加速する。GoogleとAmazonの発注先がどこに決まるかは、次のAIチップサイクルにおけるパッケージング覇権の試金石だ。

Sources

- WCCFTech: Intel’s Advanced Packaging Is Getting the Attention It Needs From AI Customers, With EMIB Gaining Ground Against TSMC’s CoWoS

- WIRED: Why Chip Packaging Could Decide the Next Phase of the AI Boom

- TrendForce: Intel Gains Momentum: 18A Eyes Apple, EMIB Reportedly Tapped for Google-MediaTek TPUs

- The Register: Intel CFO swears big Foundry wins coming soon