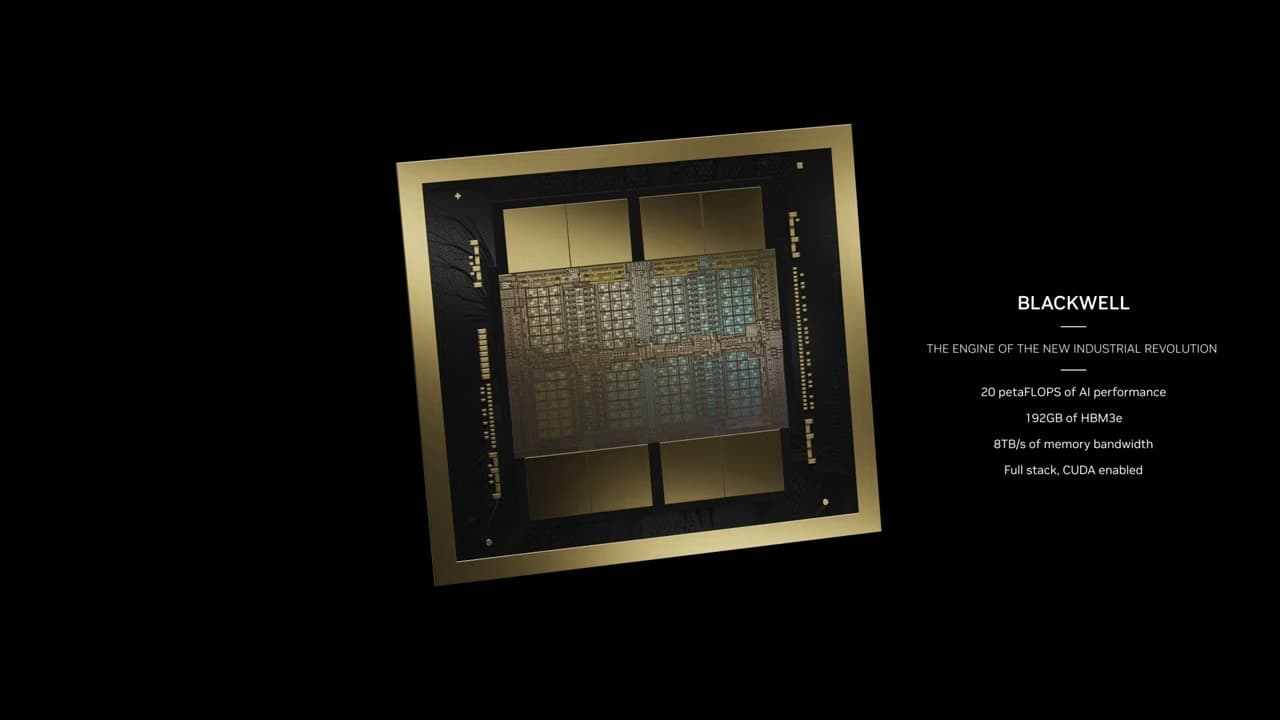

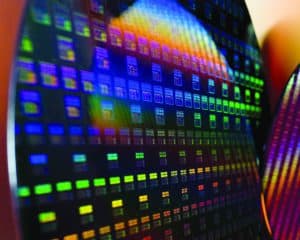

NVIDIA CEOのJensen Huang氏は、同社の次世代AIチップ「Blackwell」の生産に向けて、TSMCの最新パッケージング技術であるCoWoS-L(Chip-on-Wafer-on-Substrate with Local Silicon Interconnect)への移行を進めていることを明らかにした。この発表は、台湾のチップサプライヤーであるSiliconware Precision Industries(SPIL)のイベントで行われたものだ。

技術移行の背景と意義

NVIDIAの次世代GPUアーキテクチャ「Blackwell」は、2つのコンピュートチップレットを10TB/sという極めて高速な帯域幅で接続する必要がある。この要件を満たすため、同社は現行のCoWoS-Sから、より高度な相互接続密度を実現できるCoWoS-L技術への移行を決定した。

「Blackwellでは主にCoWoS-Lを使用します。もちろん、現在のHopperの製造ではCoWoS-Sを使用していますが、そのキャパシティもCoWoS-Lへと移行していきます」とHuang氏は説明する。「これは生産能力の削減ではなく、むしろCoWoS-L向けの能力を増強することを意味します」

技術の進化と優位性:CoWoS-LがAIチップを進化させる理由

基本構造の革新

CoWoS-L技術の革新性は、Local Silicon Interconnect(LSI)チップという新しい要素を導入した点にある。従来のCoWoS-S技術がシリコンインターポーザーのみを使用していたのに対し、CoWoS-Lではこの「LSIブリッジ」と呼ばれる小さなシリコンチップを複数配置し、有機基板と組み合わせることで、より効率的なチップ間の接続を実現している。

パフォーマンスの向上

CoWoS-L技術の採用により、以下の具体的な性能向上が可能になる:

- 相互接続密度の劇的な向上

- より多くの信号線を狭い面積に配置可能

- チップ間の距離を最小限に抑えることで信号遅延を低減

- 電力効率の改善にも貢献

- メモリ統合能力の拡大

- 最大12個のHBM3(High Bandwidth Memory)モジュールを搭載可能

- より大容量のメモリをGPUに直接接続できることで、AIモデルの処理能力が向上

- メモリバンド幅の増加により、データ転送のボトルネックを解消

- システム設計の柔軟性

- 有機基板をリディストリビューションレイヤー(RDL)として活用することで、配線の自由度が向上

- 複数のチップを効率的に配置可能

- 将来的な拡張性も確保

製造プロセスの利点

CoWoS-L技術は製造面でも重要な利点を提供する:

- 歩留まりの改善

- LSIブリッジを使用することで、大規模なシリコンインターポーザーが不要に

- 製造工程の簡素化により、不良品の発生リスクを低減

- コスト効率の向上に貢献

- スケーラビリティの向上

- モジュラー設計により、製造能力の拡大が容易

- 異なるサイズや構成のチップに対応可能

- 将来的な技術進化にも柔軟に対応

AI処理における具体的なメリット

CoWoS-L技術の導入は、AI処理において複数の重要な進展をもたらす。まず特筆すべきは演算処理能力の大幅な向上である。チップ間の高速な通信により並列処理の効率が飛躍的に改善され、これにより大規模なAIモデルの学習時間を従来よりも大幅に短縮できる。さらに、リアルタイムでの推論処理においても、より高速で安定したパフォーマンスを実現できるようになった。

メモリアクセスの最適化も、この新技術がもたらす重要な進展の一つである。より多くのHBMモジュールを搭載できるようになったことで、従来のシステムで問題となっていたメモリのボトルネックが解消される。これにより、大規模なAIモデルのパラメータをより効率的にメモリに配置できるようになり、データアクセス時の遅延も大幅に低減された。特に深層学習の分野では、モデルの規模が急速に拡大していることから、このメモリアクセスの最適化は極めて重要な意味を持つ。

さらに、システム全体の効率化という観点からも、CoWoS-L技術は大きな貢献をもたらす。電力効率が向上することで、データセンターの運用コストを抑制できるようになった。また、発熱の抑制により冷却要件も緩和され、設置面積あたりの処理能力も向上している。これらの改善は、大規模なAIインフラストラクチャを運用する企業にとって、運用コストの最適化という観点から特に重要な意味を持つ。

この技術革新により、NVIDIAのBlackwellアーキテクチャは現行のHopperアーキテクチャと比較して、著しい性能向上を実現できる見込みだ。特に、複数のコンピュートチップレット間で10TB/sという高速な相互接続を実現できる点は、大規模なAIモデルの学習や推論において決定的な優位性をもたらすと考えられる。

これらの進展は、単に技術的な性能向上にとどまらず、AI研究や応用の可能性を大きく広げる可能性を秘めている。より大規模で複雑なAIモデルの実用化が可能になることで、自然言語処理や画像認識、さらには科学計算など、幅広い分野でのブレークスルーが期待される。

製品戦略とロードマップ

NVIDIAは、Blackwellアーキテクチャに基づく複数の製品を計画している:

- B100/B200:デュアルコンピュートチップレット設計を採用し、CoWoS-L技術で実装

- B200A:単一チップ(B102シリコン)設計で144GB(4スタック)のHBM3Eメモリを搭載、従来のCoWoS-S技術を使用

当初、B100とB200には設計上の課題があったとされるが、トップグローバルルーティングメタルレイヤーの再設計によって解決されたと報告されている。

業界への影響

NVIDIAによるCoWoS-L技術への移行は、半導体産業全体に波及する物であり、特にTSMCへの影響は大きく、同社は2025年までにCoWoS生産能力を現在の2倍に拡大する計画を進めている。この生産能力拡大計画の中で、NVIDIAは全体の半分以上を占める見込みとなっており、両社の関係がより緊密化することを示している。一方で、一部のアナリストからはNVIDIAがCoWoS-S受注を最大80%削減する可能性も指摘されており、この技術移行がTSMCの収益に与える短期的な影響を懸念する声も出ている。

サプライチェーンの観点からも、この技術移行は大きな変化をもたらしている。Siliconware Precision Industries(SPIL)をはじめとする半導体後工程受託企業(OSAT)は、TSMCのCoWoS-S技術のライセンスを取得し、必要な設備投資を行ってきた。これらの企業は新たな技術動向に対応するため、事業戦略の見直しを迫られている。特に、従来のCoWoS-S実装に特化してきた企業にとって、この変化は事業モデルの転換点となる可能性が高い。

市場全体に目を向けると、この技術移行は高性能AIチップの新たなベンチマークを確立するものと見られている。NVIDIAの動きに追随する形で、他の半導体メーカーも先進的なパッケージング技術の採用を加速させる可能性が高い。これは単なる技術革新にとどまらず、AIチップの性能競争における新たなステージの幕開けを意味している。

さらに、この動きは半導体産業における研究開発の方向性にも影響を与えつつある。チップレットベースの設計とアドバンストパッケージングの組み合わせが、次世代の高性能コンピューティング製品における標準的なアプローチとして確立されつつある。これにより、パッケージング技術の重要性が一層高まり、この分野への投資や技術開発が活発化することが予想される。

このように、NVIDIAのCoWoS-L技術への移行は、単に1社の技術戦略の変更にとどまらず、半導体産業全体のエコシステムを変革する可能性を秘めている。特に、高性能コンピューティング分野におけるパッケージング技術の重要性を改めて浮き彫りにし、業界全体の技術開発の方向性に大きな影響を与えることが予想される。

Source

コメント