現代のあらゆるコンピュータは2進数(バイナリ)で動いている。CPUもメモリもストレージも、すべてが0と1の2状態を前提に設計されている。だが、論理を表現する方法はバイナリだけに限られない。3値論理(ternary logic)——3つの状態を扱う計算体系——は、理論的にはバイナリよりも情報密度が高く、数学的にも美しいとされてきた。しかし半導体製造の歴史的な経路依存により、3値コンピュータは1960年代のソ連で試みられた後は実質的に途絶えていた。

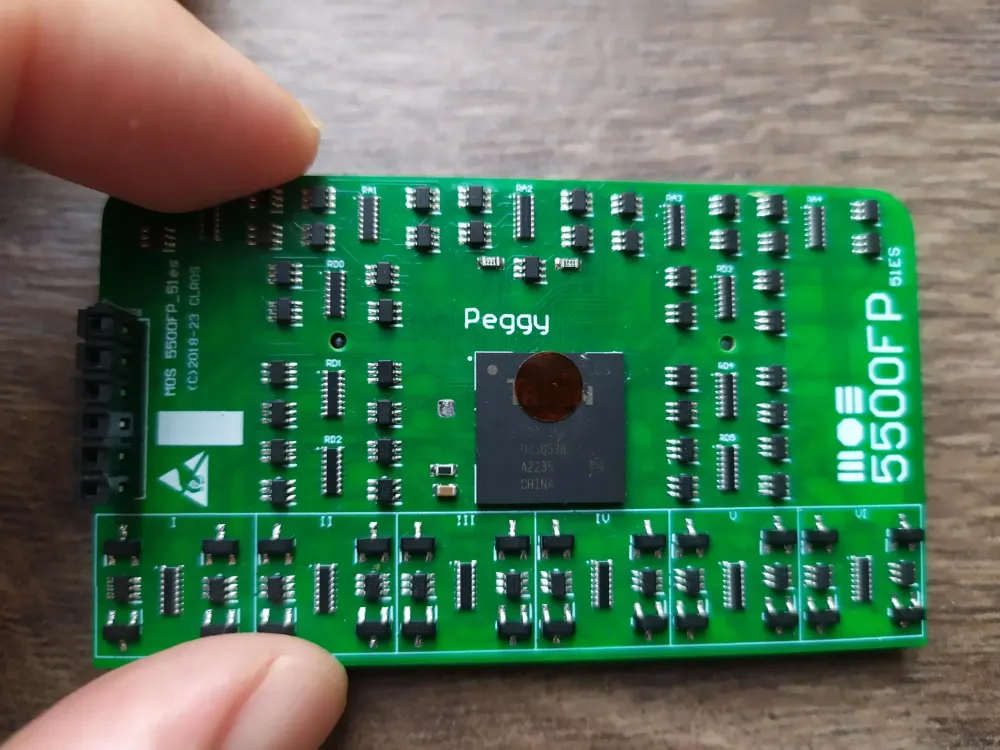

そんな中、独立研究者のClaudio Lorenzo La Rosa氏が2026年3月に発表した論文「5500FP: A 24-Trit Balanced Ternary RISC Processor」は、この60年近い空白に対する具体的な回答である。市販のFPGA(Field-Programmable Gate Array)上に24トリットの平衡3値RISCプロセッサを実装し、カスタムシリコンを起こすことなく3値コンピューティングの実験環境を構築できることを実証した。120命令のISA(命令セットアーキテクチャ)とネイティブのアトミック同期プリミティブを備え、オープンなハードウェア開発ボードも用意された、実際に動作する汎用プロセッサなのだ。

なぜ3値なのか:バイナリが唯一の選択肢ではない理由

コンピュータが二進数を採用している理由は、物理的な理由による。トランジスタのオン/オフという2状態が最もノイズ耐性が高く、製造が容易で、以降のすべてのデジタル回路がこの前提の上に積み重なってきた。だが「2状態が最も効率的か」という問いには、数学的には別の答えがある。

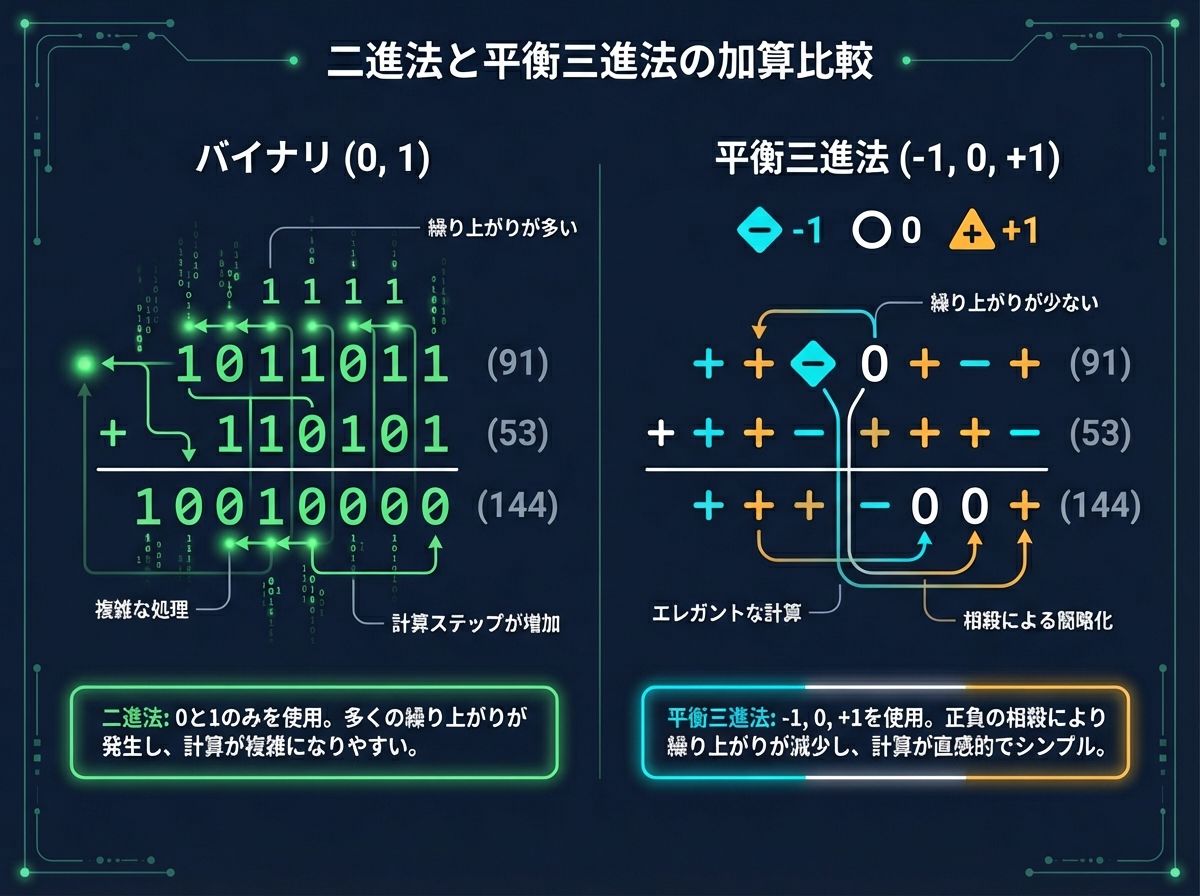

情報理論の観点では、1桁あたりの情報量は基数の対数に比例する。1ビットは2状態で1ビットの情報を持つ。3値の1桁(トリット(trit)と呼ばれる)は3状態で約1.58ビットの情報を持つ。つまり同じ桁数であれば、3値は二進数の1.58倍の情報を格納できる計算になる。Donald Knuth氏は著書「The Art of Computer Programming」第2巻で3値を「おそらく最も美しい数体系(perhaps the prettiest number system)」と評している。

5500FPが採用する「平衡3値(balanced ternary)」は、1トリットに-1、0、+1の3値を割り当てる方式だ。通常のバイナリでは負の数を表現するために符号ビットや2の補数といった仕組みが必要になるが、平衡3値では全トリットの符号を反転するだけで正負を入れ替えられる。この性質によって加減算の回路設計が簡素化され、浮動小数点演算における丸め処理も自然に行えるとされている。アイオワ大学のDouglas Jones氏が「The Ternary Manifesto」として公開している文書では、3値の数値エンコーディングがいかに合理的かが詳細に説明されている。

60年ぶりの実機:Setunの遺産と5500FPの位置づけ

3値コンピュータの歴史は1950年代末のモスクワ国立大学にまで遡る。Sergei SobolevとNikolay Brusentsovが率いるチームが開発した「Setun」は、世界初の3値コンピュータとして知られている。Setunは約50台が製造され、ソ連国内の複数の教育・研究機関で実際に稼働した。後継機のSetun 70も開発されたが、ソ連の計算機行政がIBM互換路線へ舵を切ったことで3値の系譜は途絶える。

アメリカでは1970年代にGideon Friederが「TERNAC」という3値コンピュータのプロジェクトに取り組んだが、TERNACは実機ではなくBurroughs社のバイナリ計算機上でFortranによりエミュレートされたシミュレータにとどまった。Friederは1972年に2本の論文「Ternary computers part I: motivation for ternary computers」と「Ternary computers part 2: emulation of a ternary computer」を発表しているが、ハードウェアとしての3値コンピュータは以後ほぼ姿を消す。

5500FPが意義を持つのは、Setun以来約60年ぶりに「実際に動作する汎用3値ハードウェア」として登場した点にある。2017年には3値FPGAチップの設計研究が発表され、韓国ではウエハースケールでの3値部品製造が検討されるなど、近年になって断続的に関心が復活していた。5500FPはこれらの研究を踏まえつつ、市販のFPGAボード上で実際に動作するプロセッサとして一歩先に進んだ形だ。

バイナリの上に3値を載せるジレンマ

5500FPの技術的な特徴と同時に、その本質的な限界も理解しておく必要がある。現在入手可能なFPGAはすべてバイナリ論理で動作するため、5500FPは1トリットを2ビットで表現している。3状態を2ビットに格納するため、4状態分の容量のうち1状態分が使われず、情報密度の面ではバイナリに対する3値の理論上の優位性が相殺されてしまう。

La Rosa氏自身もこの点を認識している。バイナリFPGA上での実装は「既製品のロジック部品を使える」という実用上の利点と、「既存のすべてのバイナリベースのハードウェアとインターフェースしやすい」という互換性の利点を得る代わりに、純粋な3値の効率性を犠牲にしている。つまり5500FPは3値コンピューティングの「原理実証」であり、本来の性能面での優位性を発揮するには、3値ネイティブのシリコン、つまり3状態を物理的に区別できるトランジスタの製造が必要になる。

動作周波数は20MHzで、現代のギガヘルツ級プロセッサとは比較にならない。だが速度は5500FPの目的ではない。このプロセッサが提供するのは、3値アーキテクチャの研究者や教育者が「実際にコードを書いて動かせる環境」である。120命令のRISC ISAはソフトウェア開発を行うのに十分な機能を備え、アトミック同期プリミティブの搭載はマルチプロセッシングの実験も視野に入れていることを示している。

3値コンピューティングへの再評価が始まっている背景

5500FPの出現を単なる趣味的プロジェクトと片付けるのは早い。ムーアの法則の鈍化が顕著になるなか、半導体業界はトランジスタの微細化以外の性能向上手段を模索している。プロセスの微細化が物理限界に近づくにつれ、同じトランジスタ数でより多くの情報を処理する方法を実現しうるアーキテクチャレベルでの効率改善への関心が高まっている。

3値ネイティブのトランジスタが実現すれば、同じダイ面積でバイナリの1.58倍の情報密度を得られる可能性がある。これは電力効率の改善にも直結する。データセンターの消費電力やモバイル機器のバッテリー駆動時間が常に課題とされる現在、情報密度の向上は業界が追い求めている指標のひとつだ。

韓国の研究チームがウェハースケールでの3値部品製造を検討している事実は、この方向性が純粋な学術的興味にとどまらないことを示唆している。もちろん、3値ネイティブシリコンの製造には膨大な投資と、既存のバイナリエコシステム(ソフトウェア、ツールチェーン、標準規格)との互換性という巨大な壁が立ちはだかる。Setunが失敗した理由のひとつも、まさにこのエコシステムの壁だった。

オープンな研究基盤としての価値

5500FPのもうひとつの重要な側面は、オープンハードウェアとして公開されている点である。La Rosa氏は論文をZenodoで公開し、関連情報をTernary Computing(ternary-computing.com)というWebサイトで発信している。カスタムシリコンの開発には数百万ドル規模の投資が必要だが、FPGA上の実装であれば比較的安価な開発ボードで誰でも追実験できる。

3値コンピューティングの最大の課題は、研究者がアイデアを検証するための実験環境が存在しなかったことだ。TERNACのようなソフトウェアエミュレーションでは、3値特有のハードウェア挙動——信号伝搬の特性や電力消費といったハードウェア固有の挙動——を正確に評価できない。5500FPはFPGAという制約の中ではあるものの、物理的なハードウェア上で3値ロジックを走らせることで、エミュレーションでは得られないデータを研究者に提供できる。

コンピューティングの歴史は、経路依存の産物でもある。真空管からトランジスタへ、トランジスタからICへという流れの中で、バイナリは「十分に良い」選択肢として定着し、以降のすべてのインフラがその上に構築された。しかし「十分に良い」ことと「最良」であることは異なる。5500FPが開く研究の窓は小さいが、半導体技術の次のパラダイムを考える上で、二進数以外の選択肢を真剣に検討するための具体的な足場を提供している。

論文

参考文献