現代社会のインフラを根底から支える半導体産業は、今まさに歴史的な転換点を迎えている。AI処理を担う巨大なデータセンターや日常的に持ち歩くモバイル機器の性能向上は、トランジスタのサイズを極小化し、限られたシリコンチップの上に無数の素子を詰め込む「微細化」の歴史によって実現されてきた。しかし、構成要素の寸法が原子の大きさに近づくにつれ、従来の平面的な構造による微細化は物理的な限界に直面している。

この巨大な壁を乗り越えるべく、世界中の研究機関が三次元空間を活用した新しいアーキテクチャの模索を続けている。大韓民国のDGIST(Daegu Gyeongbuk Institute of Science and Technology:大邱慶北科学技術院)に所属する電気電子計算機工学部のJae Eun Jang教授とGoeun Pyo博士らが率いる研究グループは、次世代半導体の本命とされる「垂直積層トランジスタ(vertically stacked transistors)」において、微小空間でのリーク電流(漏れ電流)を極限まで防ぐ画期的な新技術を発表した。

学術誌『Advanced Science』に掲載されたこの成果は、高集積3D半導体の実用化を阻んでいた巨大な障害を取り除き、未来のエレクトロニクスに劇的な進化をもたらす技術的突破口である。

プレナー型から垂直積層へ:半導体の歴史と物理的限界の到来

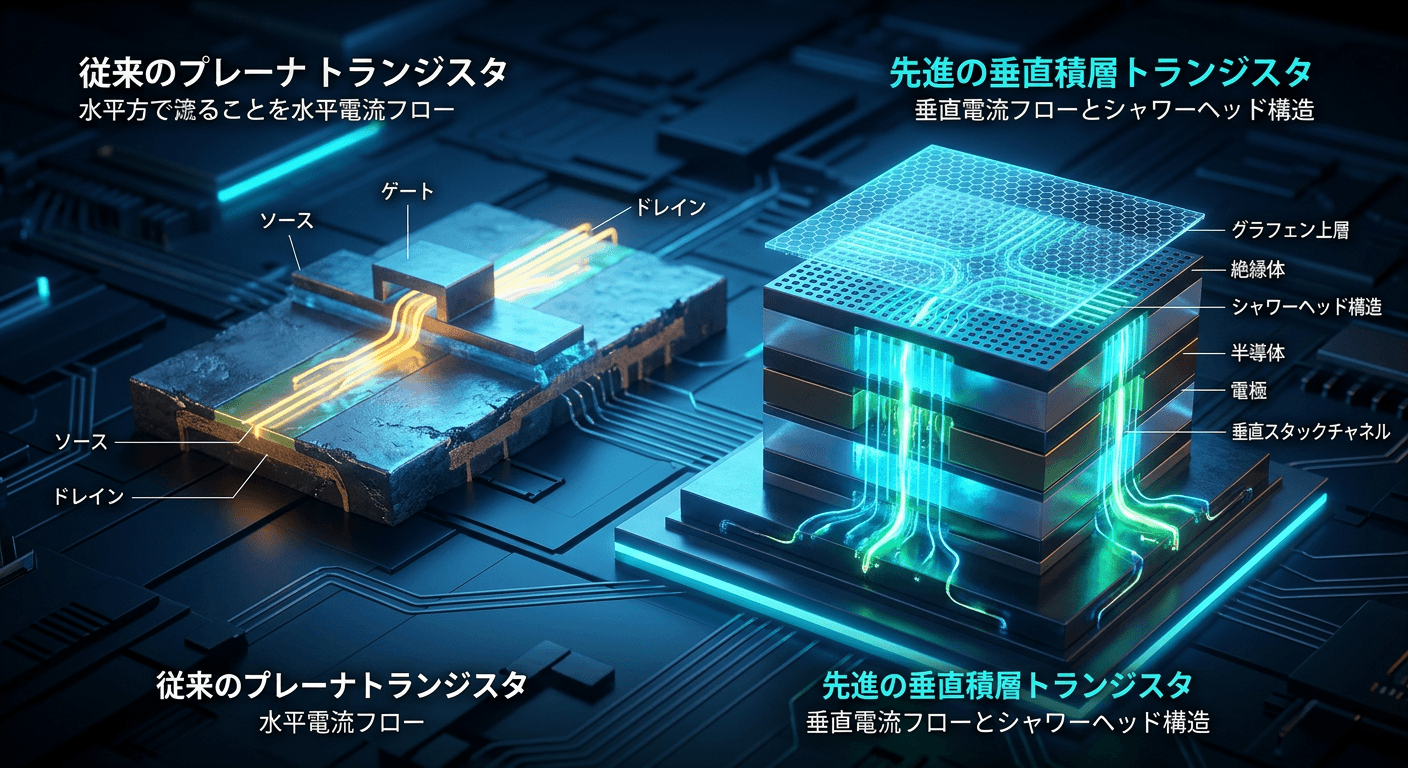

半導体技術は数十年にわたり、基板の上に素子を横並びに配置する「プレナー型(平面型)」の設計思想に基づいて進化を遂げてきた。より多くの計算能力を得るために、技術者たちはトランジスタの電子の通り道であるチャネルの長さをひたすら短くしてきた。しかし、水路の長さを短くしすぎると、水門を完全に閉めても水圧に耐えきれずに隙間から水が漏れ出してしまうのと同じように、チャネルがナノスケールに達するとゲートによる電子の制御が効かなくなる「ショートチャネル効果」が顕著になる。この制御不能なリーク電流は、現代の高性能プロセッサが膨大な熱を発し、バッテリーを急速に消耗する最大の原因となっている。

半導体業界はこの問題に対処するため、チャネルを立体的なヒレ状にしてゲートで三方から囲む「FinFET」や、四方すべてを囲む「GAA(Gate-All-Around)」といった立体構造を開発してきた。しかし、これらも基板に対して水平方向に電流を流すという基本概念の延長線上にあり、集積度の向上には自ずと限界が訪れる。そこで究極の解決策として脚光を浴びているのが、ソース、チャネル、ドレインという構成要素をパンの層のように縦方向に積み重ね、電流を垂直方向に流す「垂直積層トランジスタ」だ。このアーキテクチャは平面の専有面積を劇的に縮小させながら高い駆動力を確保できるため、高密度な三次元集積回路の実現に向けて不可欠な技術構造と見なされている。

垂直積層デバイスが抱えていたゲート電界の遮蔽問題

理論上は極めて優れた垂直積層トランジスタであるが、実用化に向けては克服すべき致命的な物理的弱点が存在していた。それは「ゲート電界のシールド(遮蔽)問題」と呼ばれる現象である。垂直構造においては、チャネル層の横や下に配置されたゲート絶縁膜とチャネルの間に、ソース電極あるいはドレイン電極が物理的に挟まり込むレイアウトになる。この巨大な金属の板が障害物となり、ゲートから発せられる電気的な信号(電界)がチャネルの中心部まで均一に浸透するのを激しく阻害してしまう。

司令塔であるゲートの指示が行き渡らなければ、トランジスタは正常なスイッチの役割を果たさない。研究チームが単一のゲートのみで動作させるシミュレーションを行った結果、ゲートの制御が及ばない領域にはオフ状態にしても電子が大量に滞留し続けることが判明した。その結果、意図しない経路を通って電流が漏れ続けてしまい、明確なオンとオフの切り替えが不可能になっていたのである。これまでの研究では、電極を極薄にしたり一部を酸化させたりする手法が試みられてきたが、高い出力電流とリーク電流の抑制を両立させる決定的な解決策は見出されていなかった。

デュアル変調構造の全貌:二つの異なる物理法則による協奏曲

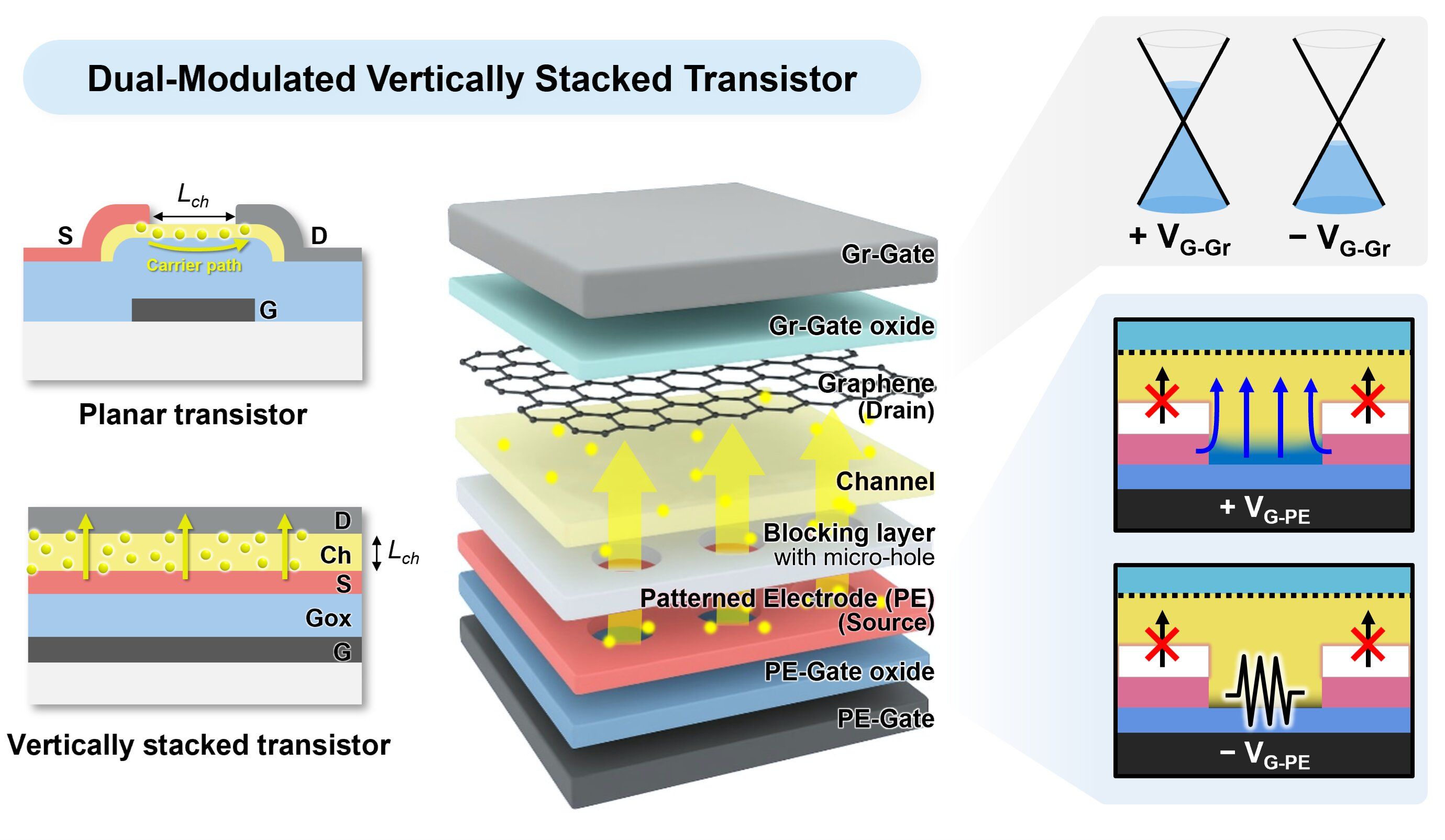

DGISTの研究チームは、この頑固な遮蔽問題を根本から解消するため、チャネルを上下から挟み込む「デュアル変調構造(dual-modulation strategy)」を考案した。同じ機能のゲートを二つ並べるのとは異なり、下部ゲート(PE-gate)と上部ゲート(Gr-gate)にそれぞれ全く異なる物理的メカニズムを持たせている。これら二つのゲートを同時に駆動させることで、互いの弱点を補完し合い、チャネル空間全体の電子の振る舞いを完璧に支配する設計を完成させたのである。

マイクロホール電極とブロッキング層による物理的制御

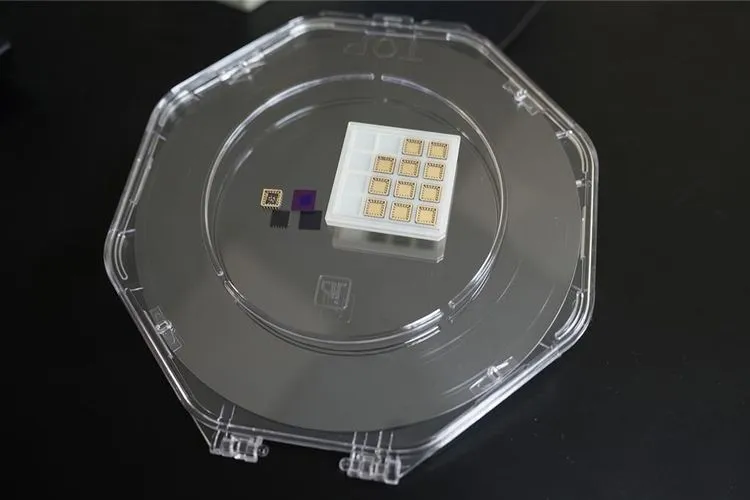

下部ゲート(PE-gate)側の設計には、物理的な形状の巧妙な工夫が凝らされている。ソース電極の素材として採用された酸化インジウムスズ(ITO)には、直径7マイクロメートルの微小な穴(マイクロホール)が格子状に無数に開けられている。ゲートからの電界は、シャワーヘッドの穴から水が吹き出すようにこの微小な隙間を通過し、厚さ40ナノメートルのIGZO(インジウム・ガリウム・亜鉛酸化物)チャネルへと直接到達する。これにより、電極の遮蔽効果を回避して電子を効果的に引き寄せることが可能になった。

しかし、穴が開いていない金属部分の直上は、依然として電界が届かない死角である。チームはこの課題を完全に排除するため、ソース電極とドレイン電極が直接重なり合うゲート圏外の領域に、酸化シリコン(SiO2)による厚さ50ナノメートルの「ブロッキング層(Leakage Blocking Layer)」を正確に挿入した。この絶縁体の堅固な壁により、電界でコントロールできない領域を通じた不要な電子の移動は物理的に完全に遮断される。水漏れを起こす経路そのものをコンクリートで塞いでしまうような、極めて確実な手法である。

夢の素材「グラフェン」によるフェルミ準位の操作

上部ゲート(Gr-gate)の制御メカニズムにおいて主役を演じるのが、ドレイン電極として組み込まれた炭素原子の二次元シート「グラフェン」である。グラフェンはディラックポイントと呼ばれる特異なエネルギーバンド構造を持っており、外部から電界を印加することでフェルミ準位(電子が存在する確率を示すエネルギーの基準値)を自在に変動させる性質を備えている。

上部ゲートにマイナスの電圧を与えると、グラフェンのフェルミ準位が低下し、IGZOチャネルとの境界面に電子の通行を拒絶する巨大な電気的障壁(ショットキー障壁)が形成される。このとき、トランジスタは完璧なオフ状態となり、一切の電流を通さない。反対にプラスの電圧を与えれば、フェルミ準位が上昇して障壁は消滅し、大電流が一気に流れ込む。下部ゲートが水路の幅を直接広げたり狭めたりする横開きの水門だとすれば、上部ゲートはグラフェンという素材の性質を利用して水門の段差そのものを上下に動かす働きを持つ。この二つの全く異なるアプローチを同期させることで、極微細空間における前例のない精密な電流制御が実現したのだ。

実証された限界突破の圧倒的パフォーマンス

緻密に計算された新しいアーキテクチャが叩き出した性能数値は、既存の半導体工学の常識を大きく覆すものであった。ソースからドレインまでの距離が極めて短いナノスケールのデバイスでありながら、ドレイン電圧3Vの過酷な条件下においても、オフ状態のリーク電流は約10のマイナス12乗アンペア(1ピコアンペア)という測定限界に近いレベルまで極限に抑制されている。単一のゲート動作ではドレイン電圧の上昇に伴ってリーク電流が急増してしまったのに対し、上下のゲートを連動させた場合はリーク電流が全く増加しない強靭さを見せた。

オン状態の電流とオフ状態のリーク電流の差を示す「オン/オフ比」は100万倍(10の6乗)を突破し、極めて明瞭なスイッチング動作を証明した。さらに、0.1Vという極わずかな駆動電圧で1平方センチメートルあたり1ミリアンペア、1Vの電圧では同50ミリアンペアという巨大な出力電流を達成している。モバイル機器の待機電力を限りなくゼロに近づけつつ、瞬時に高速な処理能力を引き出すという、相反する要求を完璧に満たす特性である。

微細化の最大の敵であるDIBL(ドレイン誘起障壁低下:ドレイン電圧の影響で意図せず電流が流れてしまう現象)も劇的に改善されている。上下のゲートが巨大な静電容量を形成してチャネル全体を強力に挟み込み、ドレインからの電界の悪影響を完全に遮断(スクリーニング)するため、しきい値電圧はゼロボルト付近で微動だにせず安定している。

カプセル化構造による自己防衛とスケーラブルな製造プロセス

実験室での優れた数値に加え、現実の過酷な環境下で長期間安定して稼働する耐久性も実用化には不可欠である。一般的に酸化物半導体は、外部からの光や長時間の電圧負荷によって特性が劣化しやすい弱点を持つ。しかし、DGISTの垂直積層トランジスタは、極薄のチャネル層の周囲を金属ゲート、絶縁層、電極が隙間なく覆い隠す「自己カプセル化(Self-passivating)」構造を採用している。光が内部の半導体に到達することを構造的に防ぐ要塞のような設計である。

実際にデバイスに対して強力なLED光や紫外線(UV光)を照射し続けるテストを実施しても、電流値やしきい値電圧の変動はほぼ観測されなかった。また、マイナス方向の電圧を1000秒間にわたってかけ続けるバイアスストレス試験においても、初期の優れた性能をそのまま維持した。デバイスを保護するための特別なコーティング(パッシベーション層)を追加する工程を完全に省きながら、これほどの高い信頼性を獲得している点は特筆に値する。

製造プロセスの観点からも、このアーキテクチャは産業界に多大な恩恵をもたらす。複雑で高価な極端紫外線(EUV)露光装置を用いたナノメートル単位の精緻な位置合わせを必要としないのが最大の特徴である。最も精度を要する工程でもサブミクロン(1ミリの1万分の1)レベルのアライメント精度で十分であるため、シリコンウェハー全体での大規模な量産において位置ズレによるエラーが蓄積しにくい。また、熱処理を含むすべての製造工程が300℃以下の低温で行われるため、熱に弱い柔軟な素材(フレキシブル基板)上での製造も可能になる。

次世代エレクトロニクスの扉を開く革新技術

数十年にわたり半導体産業を牽引してきたムーアの法則が物理的な限界を迎える中、垂直積層トランジスタの実用化は業界全体にとって焦眉の急であった。今回DGISTの研究チームが提示したデュアル変調構造は、微細空間における電流の漏れという最大の障壁を、理論的かつ実践的に打破した画期的な成果である。ゲート電界の遮蔽問題を、物理的な絶縁壁と新素材グラフェンの電子的な性質を組み合わせて解決した設計思想は、非常に洗練されており美しい。

リーク電流が極限まで抑え込まれ、低電圧での高出力を実現したこの技術は、充電の頻度を劇的に減らす次世代のウェアラブル端末や、人間の脳を模倣して膨大な計算を省電力で行うニューロモルフィック・コンピューティング・チップへの応用に直結する。平面から立体へ、そして三次元方向に素子を何層にも重ね合わせる超高密度な集積回路の実現に向けて、確固たる基盤が築かれた。

従来型の垂直トランジスタが抱えていた根本的な限界を鮮やかに克服した本技術は、次世代の低電力・高集積3D半導体時代の幕開けを告げる重要なマイルストーンとなる。人類の技術的進化の最前線において、材料科学の深淵な理解と精緻なアーキテクチャ設計の融合が、テクノロジーの未来を切り拓く力強い原動力となっている。

論文

- Advanced Science: Dual-Modulated Vertically Stacked Transistors With Fully Laminated Plate-Type Architecture Featuring Nanoscale Channel Length

参考文献